Heim >Technologie-Peripheriegeräte >KI >NVIDIA Chefwissenschaftler: Vergangenheit, Gegenwart und Zukunft der Deep-Learning-Hardware

NVIDIA Chefwissenschaftler: Vergangenheit, Gegenwart und Zukunft der Deep-Learning-Hardware

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBnach vorne

- 2023-04-12 15:07:072016Durchsuche

Die letzten zehn Jahre waren das „goldene Jahrzehnt“ des Deep Learning. Es hat die Art und Weise, wie Menschen arbeiten und spielen, völlig verändert und wurde in verschiedenen Branchen wie der medizinischen Versorgung, der Bildung usw. weit verbreitet Produktdesign ist untrennbar mit der Weiterentwicklung der Computerhardware verbunden, insbesondere mit der Innovation der GPU.

Die erfolgreiche Implementierung der Deep-Learning-Technologie hängt von drei Hauptelementen ab: Das erste ist der Algorithmus. Die meisten Deep-Learning-Algorithmen wie Deep Neural Networks, Convolutional Neural Networks, Backpropagation-Algorithmen und stochastischer Gradientenabstieg wurden in den 1980er Jahren oder noch früher vorgeschlagen.

Der zweite ist der Datensatz. Der zum Trainieren eines neuronalen Netzwerks verwendete Datensatz muss groß genug sein, damit das neuronale Netzwerk andere Techniken übertreffen kann. Erst zu Beginn des 21. Jahrhunderts wurden große Datenmengen wie Pascal und ImageNet verfügbar. Der dritte ist Hardware. Nur mit einer ausgereiften Hardwareentwicklung kann die Zeit, die zum Trainieren großer neuronaler Netze mit großen Datensätzen erforderlich ist, in einem angemessenen Bereich kontrolliert werden. Die Branche geht im Allgemeinen davon aus, dass eine „vernünftigere“ Schulungszeit etwa zwei Wochen beträgt.

Der zweite ist der Datensatz. Der zum Trainieren eines neuronalen Netzwerks verwendete Datensatz muss groß genug sein, damit das neuronale Netzwerk andere Techniken übertreffen kann. Erst zu Beginn des 21. Jahrhunderts wurden große Datenmengen wie Pascal und ImageNet verfügbar. Der dritte ist Hardware. Nur mit einer ausgereiften Hardwareentwicklung kann die Zeit, die zum Trainieren großer neuronaler Netze mit großen Datensätzen erforderlich ist, in einem angemessenen Bereich kontrolliert werden. Die Branche geht im Allgemeinen davon aus, dass eine „vernünftigere“ Schulungszeit etwa zwei Wochen beträgt.

An diesem Punkt hat sich im Bereich Deep Learning ein Präriefeuer entzündet. Wenn Algorithmen und Datensätze als der gemischte Treibstoff des Deep Learning betrachtet werden, dann ist die GPU der Funke, der sie entzündet. Wenn leistungsstarke GPUs zum Trainieren von Netzwerken verwendet werden können, wird die Deep-Learning-Technologie praktisch.

Seitdem hat Deep Learning andere Algorithmen ersetzt und wird häufig in der Bildklassifizierung, Bilderkennung, Spracherkennung, Verarbeitung natürlicher Sprache, Zeitanalyse und anderen Bereichen eingesetzt. und selbst in Go ist es auch im Schach und Schach zu sehen. Da Deep Learning in alle Aspekte des menschlichen Lebens vordringt, erfordern Modelltraining und Inferenz immer anspruchsvollere Hardware.

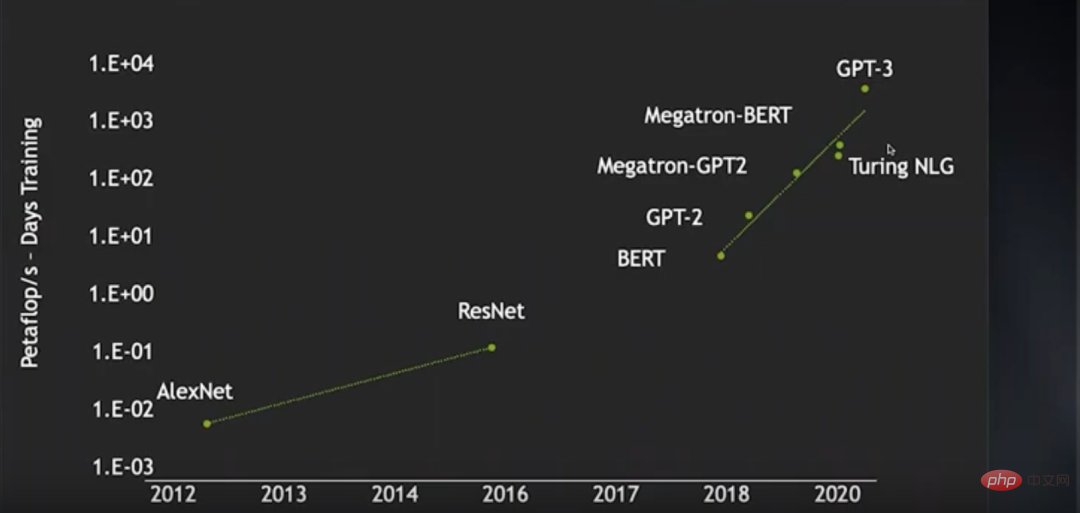

Von der Entstehung von AlexNet in Von 2012 bis zum Erscheinen von ResNet im Jahr 2016 stieg der Trainingsrechenleistungsverbrauch von Bild-Neuronalen Netzen (in Petaflop/s-Tag) um fast zwei Größenordnungen. Von BERT im Jahr 2018 bis GPT-3 stieg die Trainingsrechenleistung in den letzten Jahren Der Verbrauch stieg um fast 4 Größenordnungen. In diesem Zeitraum wurde dank der Weiterentwicklung bestimmter Technologien die Trainingseffizienz neuronaler Netze erheblich verbessert und dadurch viel Rechenleistung eingespart, andernfalls wäre der Anstieg des Rechenleistungsverbrauchs noch übertriebener ausgefallen.

Von der Entstehung von AlexNet in Von 2012 bis zum Erscheinen von ResNet im Jahr 2016 stieg der Trainingsrechenleistungsverbrauch von Bild-Neuronalen Netzen (in Petaflop/s-Tag) um fast zwei Größenordnungen. Von BERT im Jahr 2018 bis GPT-3 stieg die Trainingsrechenleistung in den letzten Jahren Der Verbrauch stieg um fast 4 Größenordnungen. In diesem Zeitraum wurde dank der Weiterentwicklung bestimmter Technologien die Trainingseffizienz neuronaler Netze erheblich verbessert und dadurch viel Rechenleistung eingespart, andernfalls wäre der Anstieg des Rechenleistungsverbrauchs noch übertriebener ausgefallen.

Die Forscher wollten ein größeres Sprachmodell mit einem größeren unbeaufsichtigten Sprachdatensatz trainieren. Obwohl sie bereits über einen GPU-Cluster mit 4000 Knoten verfügten, waren die Operationen möglich die innerhalb einer angemessenen Einarbeitungszeit bearbeitet werden können, sind noch sehr begrenzt. Das heißt, wie schnell sich die Deep-Learning-Technologie entwickelt, hängt davon ab, wie schnell sich die Hardware entwickelt.

Heutzutage werden Deep-Learning-Modelle nicht nur immer komplexer, sondern haben auch ein immer breiteres Anwendungsspektrum. Daher besteht die Notwendigkeit, die Leistung des Deep Learning weiter zu verbessern. Wie kann sich die Deep-Learning-Hardware also weiter verbessern? NVIDIA-Chefwissenschaftler Bill Dally ist zweifellos die Autorität, die diese Frage beantworten kann. Mehrere Richtungen zur Verbesserung der Leistungserweiterung. Die OneFlow-Community hat dies zusammengestellt.

1 Entwicklungsgeschichte der GPU-Architektur

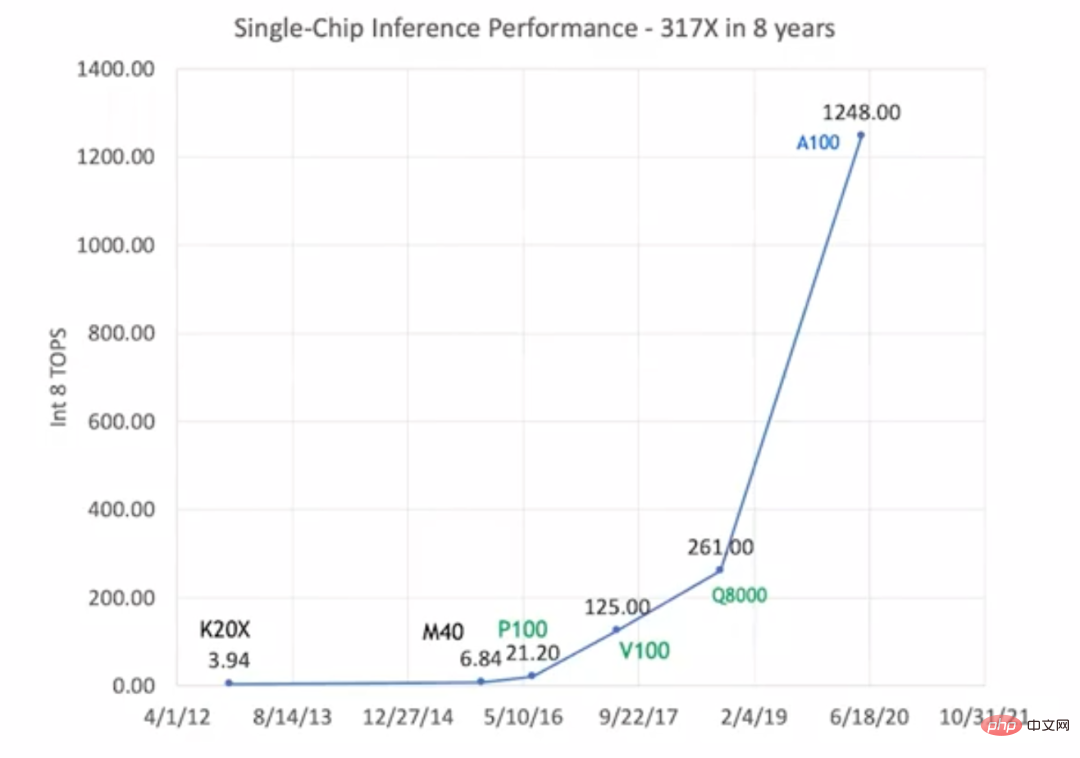

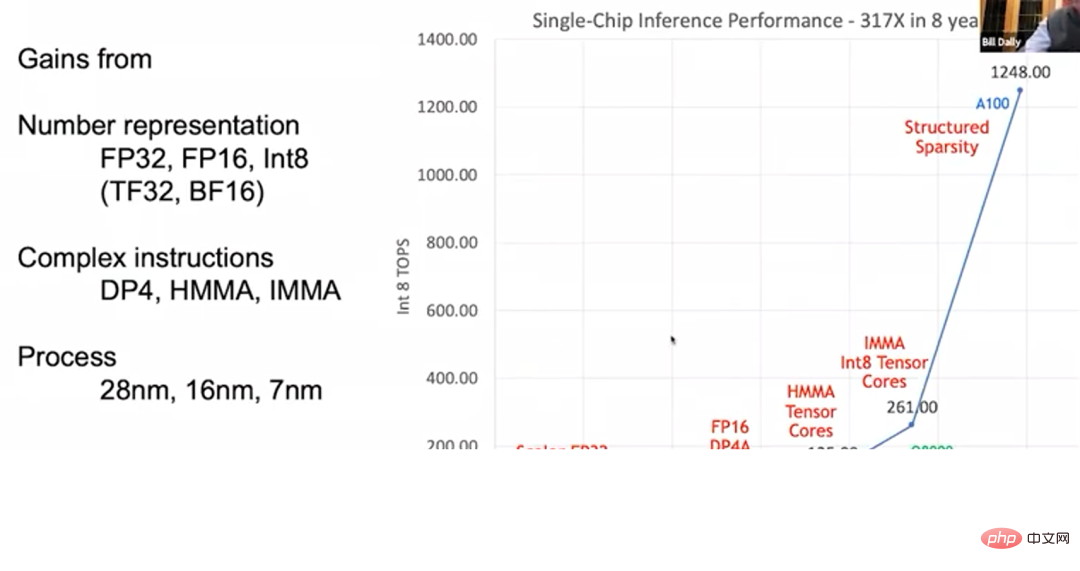

Von K20X im Jahr 2012 von Beim 2020 A100 hat sich die GPU-Inferenzleistung auf das 317-fache erhöht. Dies nennen wir „Huangs Gesetz“, und diese Entwicklungsrate ist viel schneller als das „Mooresche Gesetz“.

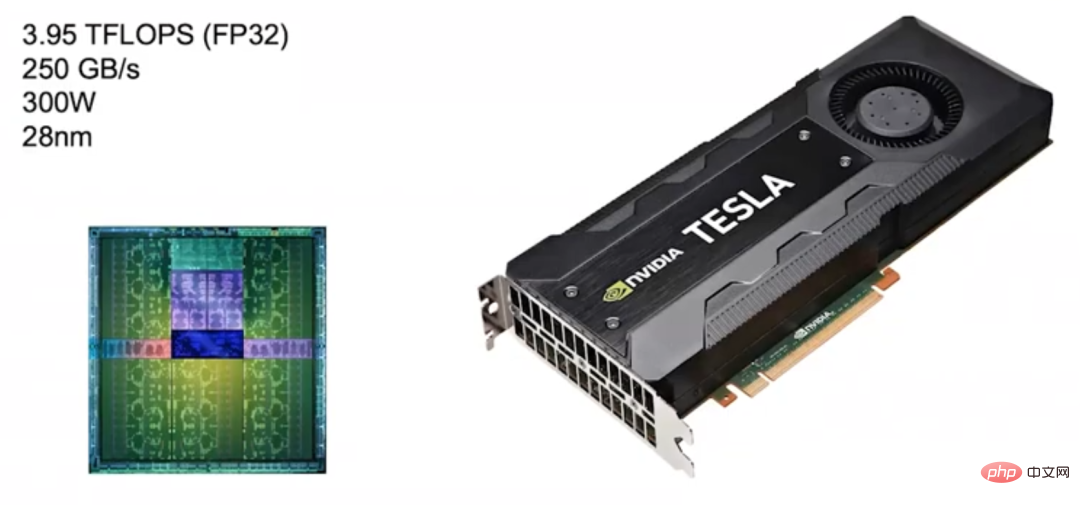

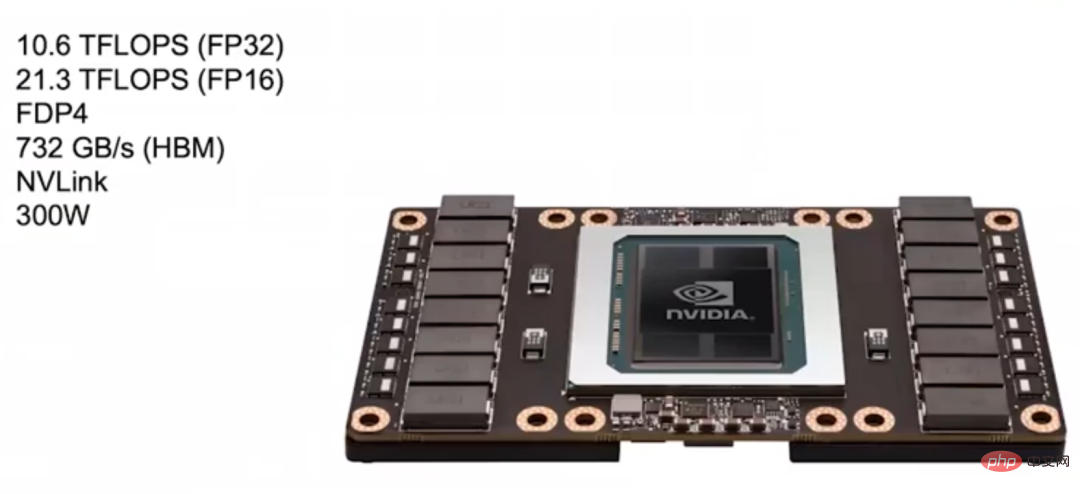

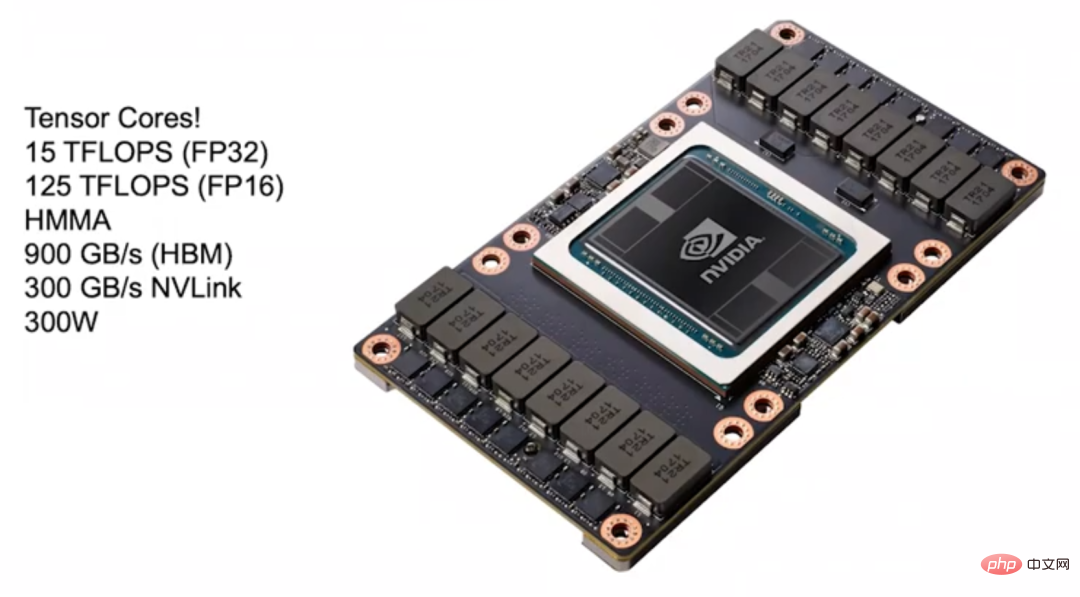

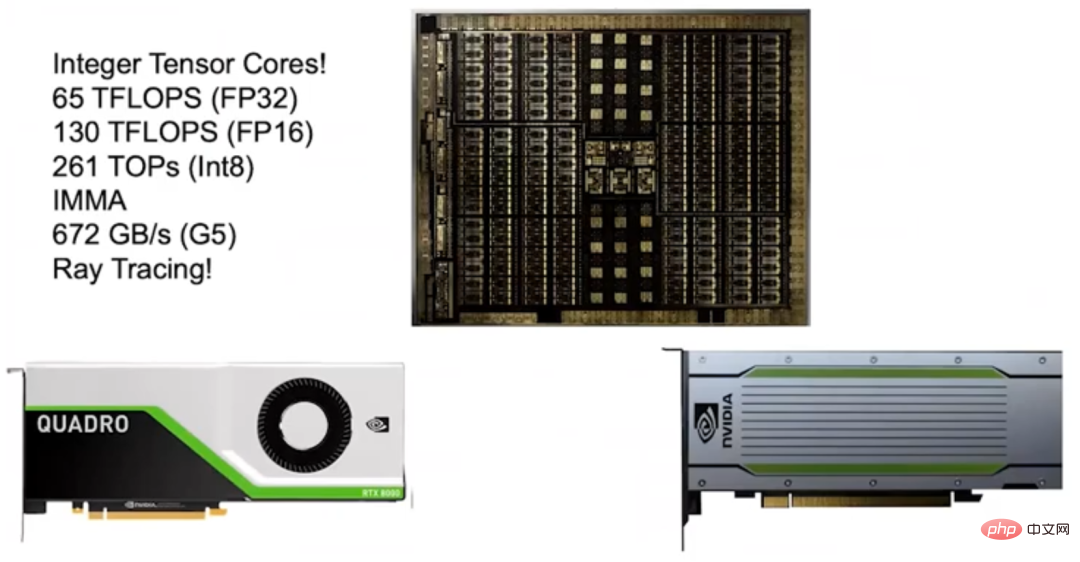

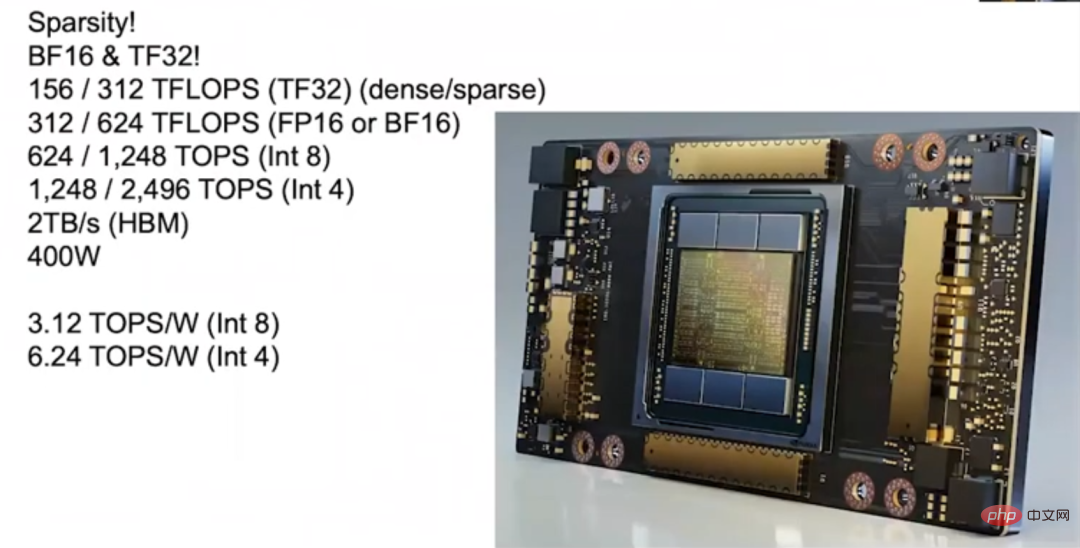

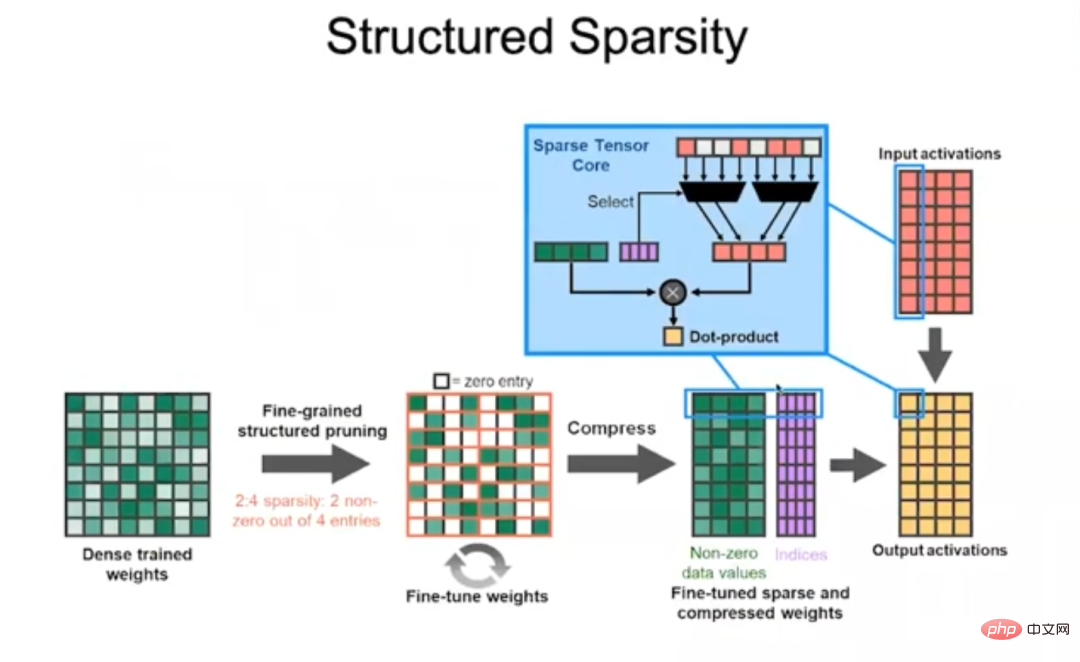

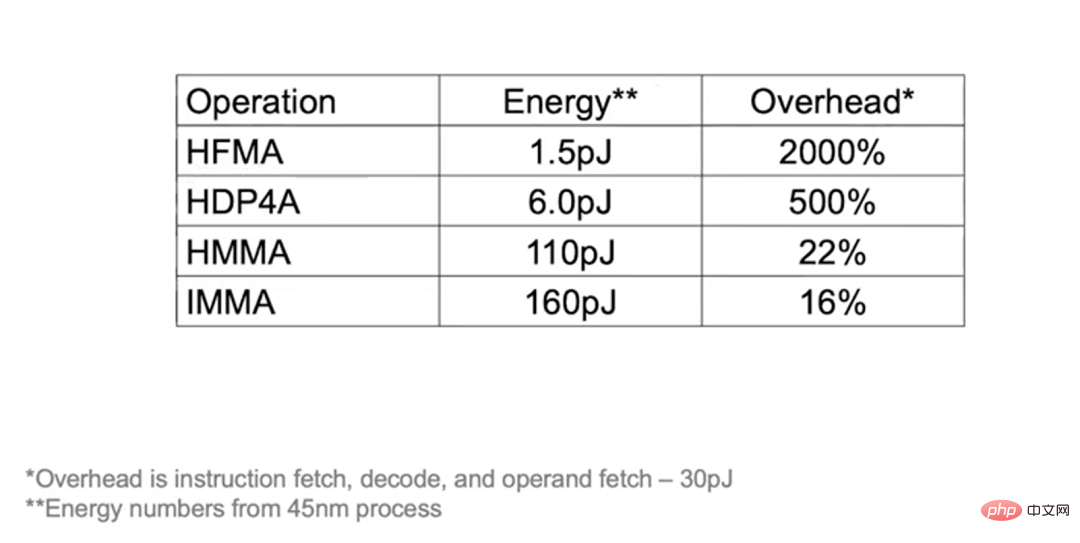

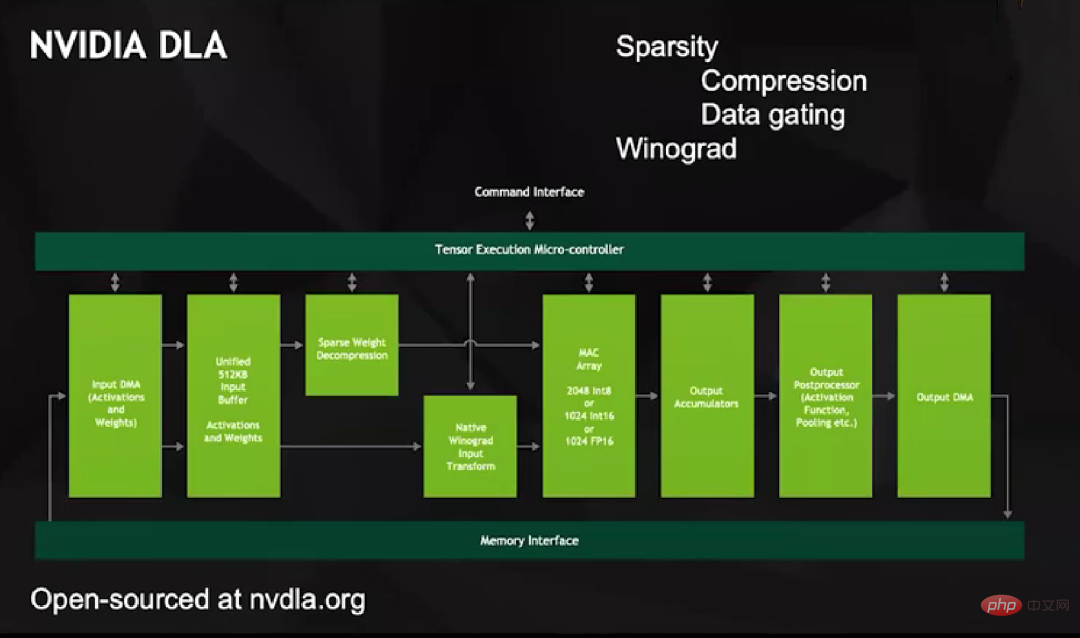

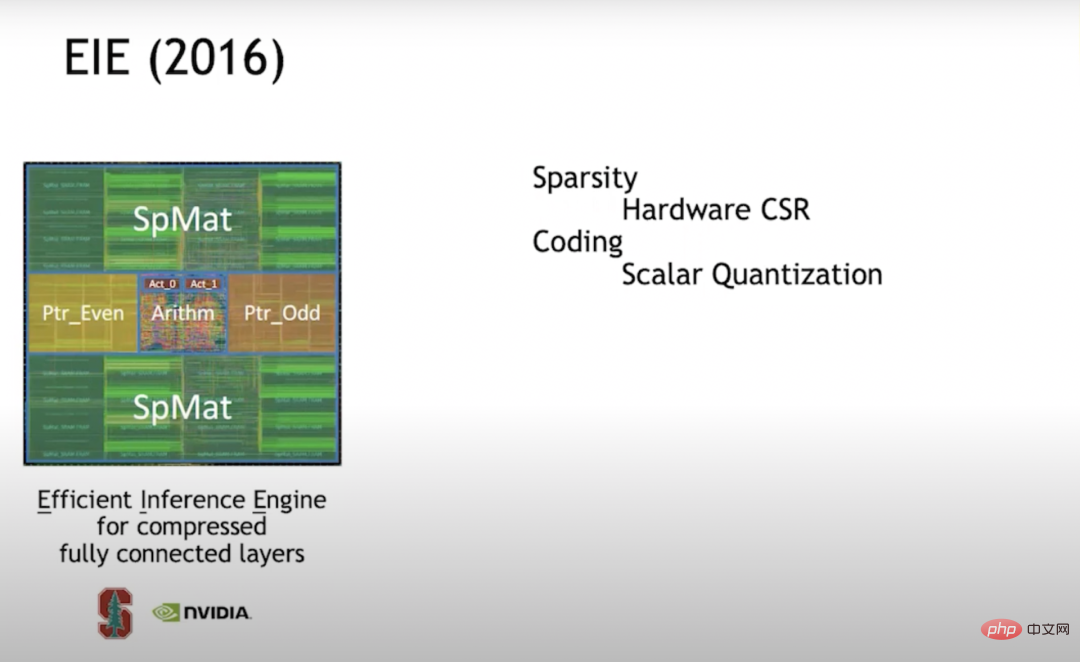

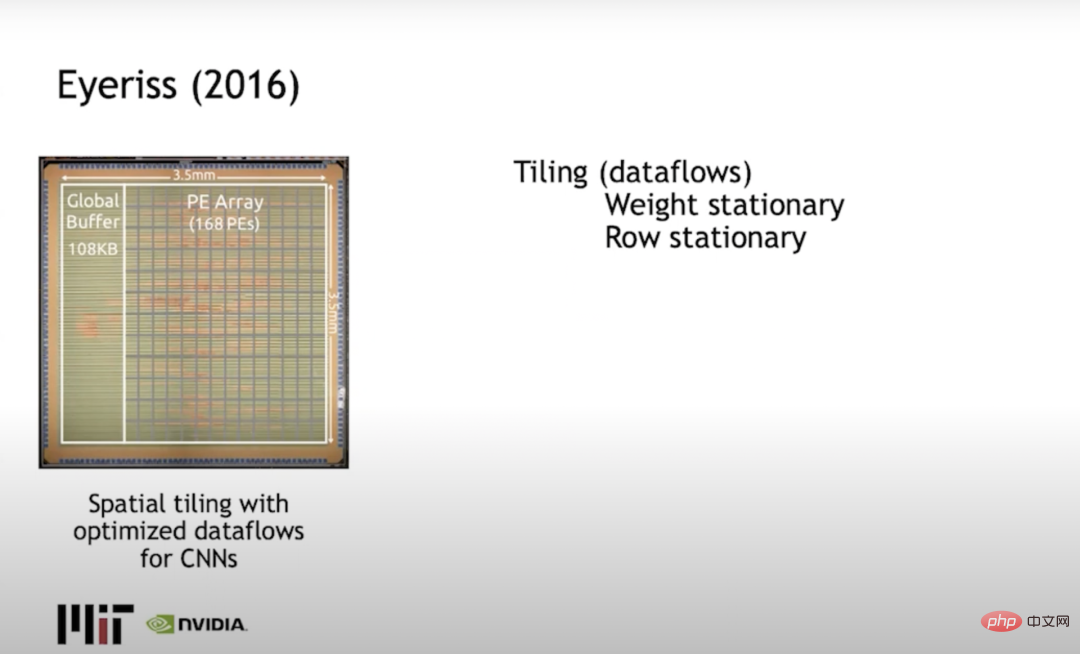

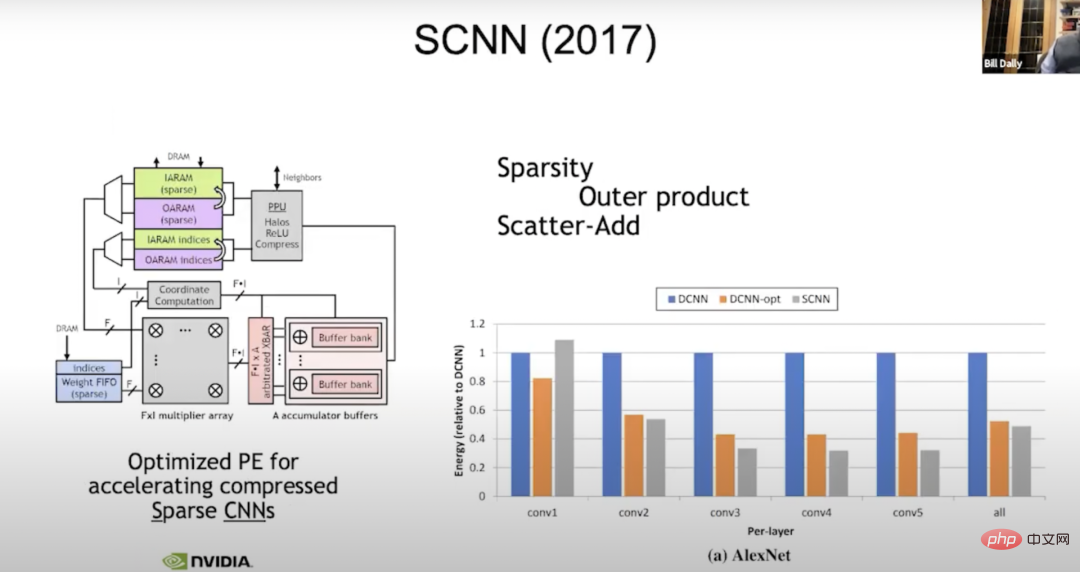

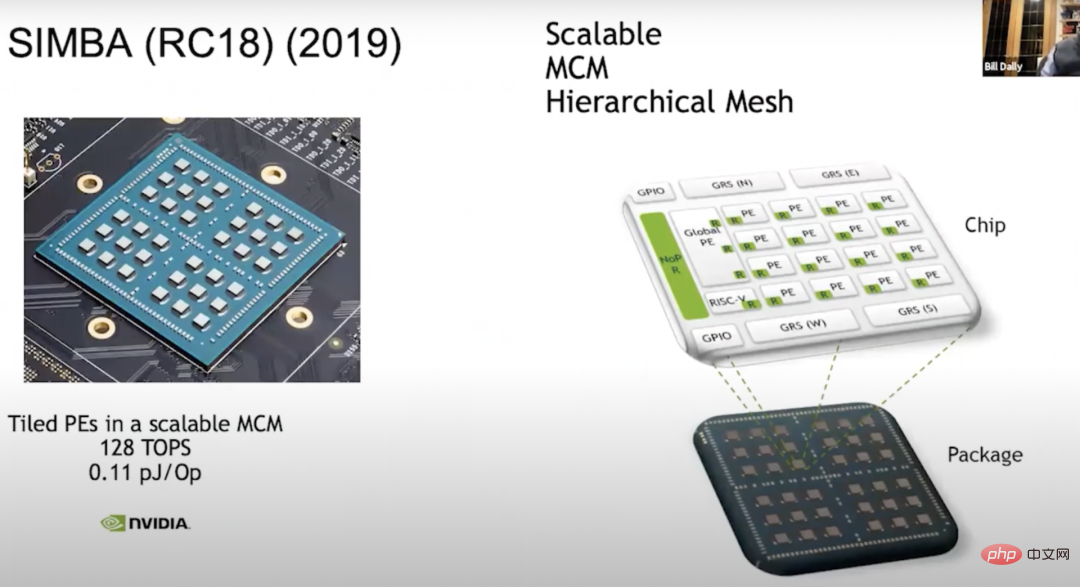

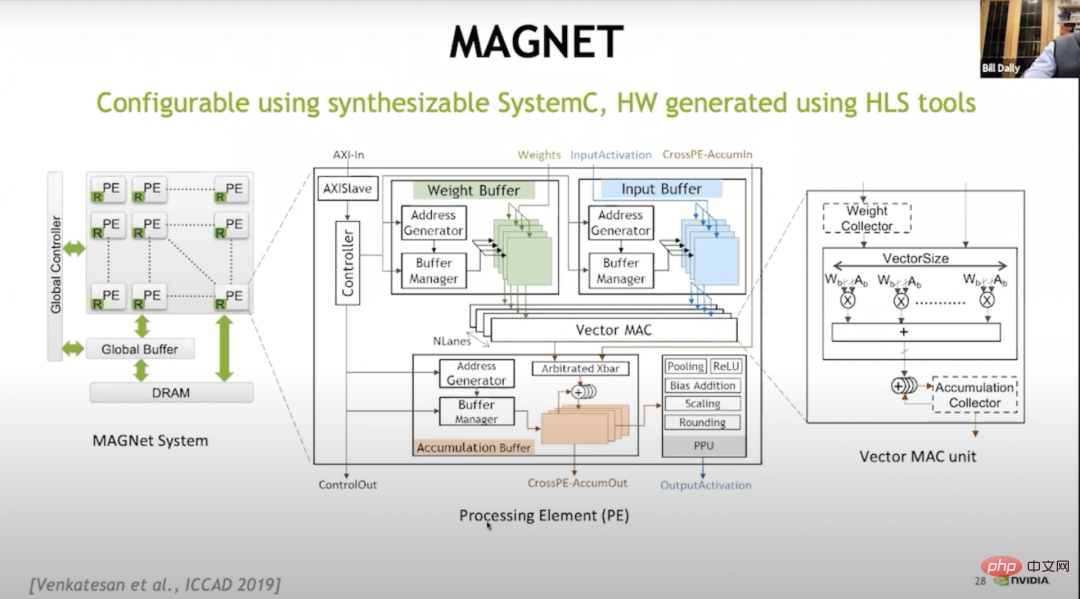

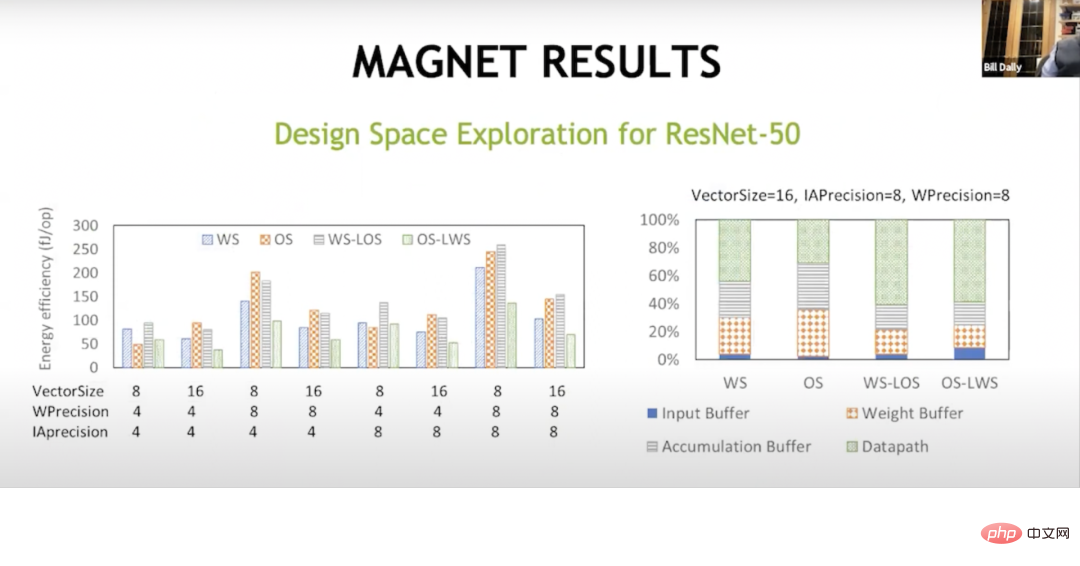

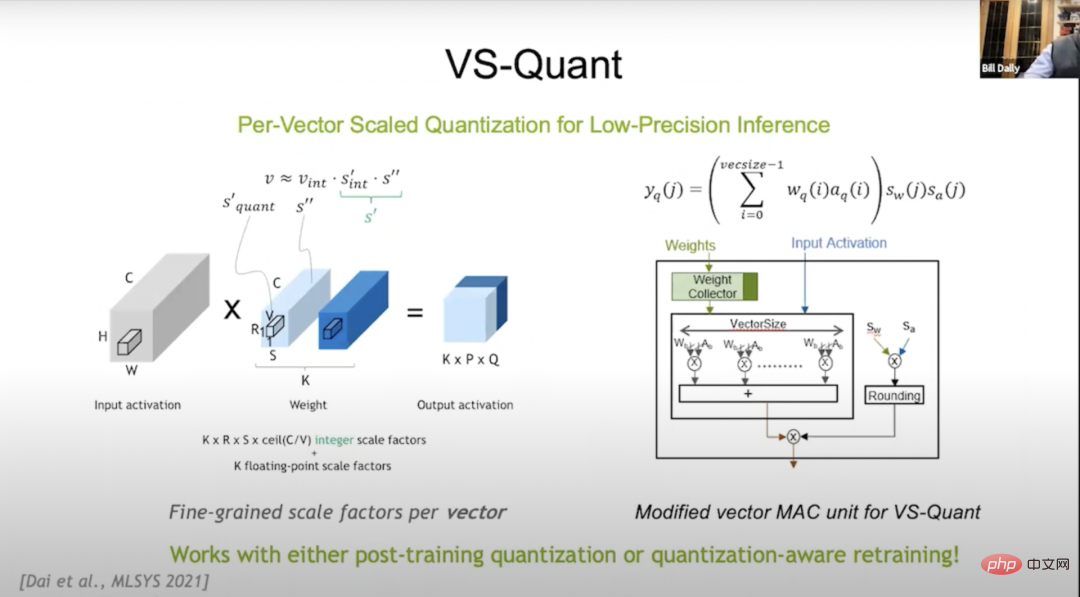

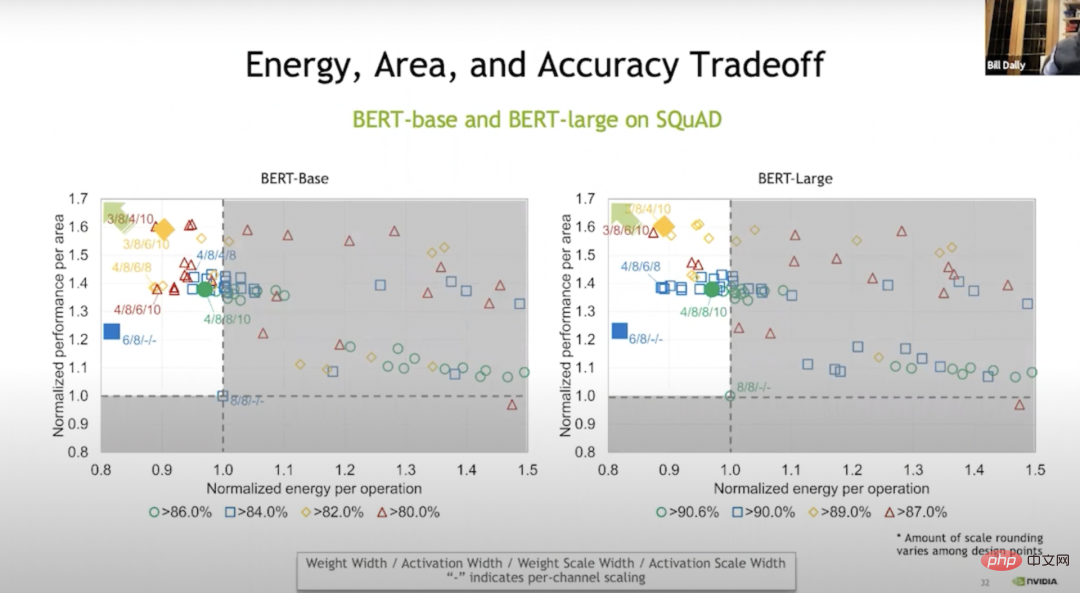

Die Inferenzleistung der GPU hat sich verbessert Aber im Gegensatz zum „Mooreschen Gesetz“ hängt die Leistungsverbesserung der GPU im „Huangschen Gesetz“ nicht vollständig vom Fortschritt der Prozesstechnologie ab. Das obige Bild markiert diese GPU-Typen in den Farben Schwarz, Grün und Blau, was darauf hinweist, dass sie drei verschiedene Prozesstechnologien verwenden. Der frühe K20X und der M40 nutzten den 28-nm-Prozess; der P100, der V100 und der Q8000 verwendeten den 16-nm-Prozess und der A100 den 7-nm-Prozess. Fortschritte in der Prozesstechnologie können die GPU-Leistung nur auf das 1,5- bis 2-fache des ursprünglichen Niveaus steigern. Die insgesamt 317-fache Leistungssteigerung ist vor allem auf die Verbesserung der GPU-Architektur und des Schaltungsdesigns zurückzuführen. Im Jahr 2012 brachte NVIDIA eine GPU mit Kepler-Architektur auf den Markt, die jedoch nicht speziell für Deep Learning entwickelt wurde. Nvidia begann sich erst im Jahr 2010 mit Deep Learning zu beschäftigen und hatte zu diesem Zeitpunkt noch nicht darüber nachgedacht, GPU-Produkte für Deep Learning anzupassen. Kepler (2012) Keplers Zielanwendungsszenario ist Bildverarbeitung und Hochleistungsrechnen, wird jedoch hauptsächlich für die Bildverarbeitung verwendet. Daher zeichnet es sich durch eine hohe Gleitkomma-Rechenleistung aus, wobei die FP32-Berechnungsgeschwindigkeit (Einzelpräzisions-Gleitkommaberechnung) fast 4 TFLOPS und die Speicherbandbreite 250 GB/s erreicht. Aufgrund der hervorragenden Leistung von Kepler betrachtet NVIDIA es auch als Basis für seine eigenen Produkte. Pascal (2016)Später führte Nvidia 2016 die Pascal-Architektur ein, deren Design besser für Deep Learning geeignet ist. Nach einigen Recherchen stellte NVIDIA fest, dass viele neuronale Netze mit FP16 (Gleitkommaberechnung mit halber Genauigkeit) trainiert werden können, sodass die meisten Modelle der Pascal-Architektur FP16-Berechnungen unterstützen. Die FP32-Berechnungsgeschwindigkeit dieser Pascal-GPU im Bild unten kann 10,6 TFLOPS erreichen, was viel höher ist als die der vorherigen Kepler-GPU, und ihre FP16-Berechnung ist schneller, doppelt so schnell wie FP32. Die Pascal-Architektur unterstützt auch komplexere Anweisungen wie FDP4, sodass der Aufwand für das Abrufen von Anweisungen, die Dekodierung und das Abrufen von Operanden in 8 Rechenoperationen amortisiert werden kann. Im Vergleich zum vorherigen Fuse Multiply-Add-Befehl (Fuse Multiply-Add), der den Overhead nur zwei arithmetischen Operationen zuordnen kann, kann die Pascal-Architektur den durch zusätzlichen Overhead verursachten Energieverbrauch reduzieren und ihn stattdessen für mathematische Operationen verwenden. Die Pascal-Architektur verwendet auch HBM-Videospeicher mit einer Bandbreite von 732 GB/s, was dem Dreifachen von Kepler entspricht. Der Grund für die Erhöhung der Bandbreite liegt darin, dass die Speicherbandbreite den größten Engpass bei der Verbesserung der Deep-Learning-Leistung darstellt. Darüber hinaus nutzt Pascal NVLink, um mehr Maschinen und GPU-Cluster zu verbinden und so umfangreiche Schulungen besser abzuschließen. Das von NVIDIA für Deep Learning eingeführte DGX-1-System verwendet 8 GPUs basierend auf der Pascal-Architektur. ... Tensor Core wird in der Volta-Architektur zur Beschleunigung des Deep Learning eingeführt. Tensor Core kann in Form von Anweisungen mit der GPU verbunden werden. Die Schlüsselanweisung ist HMMA (Half Precision Matrix Multiply Accumulate), die zwei 4×4 FP16-Matrizen multipliziert und die Ergebnisse dann zu einer addiert. Bei FP32-Matrizen handelt es sich um eine Operation kommt beim Deep Learning sehr häufig vor. Durch die HMMA-Anweisung kann der Aufwand für das Abrufen von Anweisungen und die Dekodierung durch Amortisation auf die ursprünglichen 10 bis 20 % reduziert werden. Volta hat außerdem den HBM-Videospeicher aktualisiert, sodass die Speicherbandbreite 900 GB/s erreicht, und verwendet außerdem eine neue Version von NVLink, die die Bandbreite beim Aufbau eines Clusters verdoppeln kann. Darüber hinaus führt die Volta-Architektur auch NVSwitch ein, der mehrere GPUs verbinden kann. Theoretisch kann NVSwitch bis zu 1024 GPUs verbinden, um eine große Maschine mit gemeinsam genutztem Speicher aufzubauen. Turing (2018) Im Jahr 2018 brachte NVIDIA die Turing-Architektur auf den Markt. Aufgrund des großen Erfolgs des vorherigen Tensor Core hat NVIDIA den Integer Tensor Core auf den Markt gebracht. Da die meisten neuronalen Netze mit FP16 trainiert werden können und die Inferenz keine zu hohe Genauigkeit und keinen großen Dynamikbereich erfordert, verwenden Sie einfach Int8. Daher führte NVIDIA den Integer Tensor Core in der Turing-Architektur ein, was die Leistung verdoppelte. Die Turing-Architektur nutzt auch GDDR-Speicher, um NLP-Modelle und Empfehlungssysteme mit hohen Bandbreitenanforderungen zu unterstützen. Damals bezweifelten einige Leute, dass die Energieeffizienz der Turing-Architektur nicht so gut sei wie die anderer Beschleuniger auf dem Markt. Wenn Sie jedoch sorgfältig rechnen, werden Sie feststellen, dass die Turing-Architektur tatsächlich energieeffizienter ist, da Turing G5-Videospeicher verwendet, während andere Beschleuniger LPDDR-Speicher verwenden. Meiner Meinung nach ist die Wahl des G5-Speichers die richtige Entscheidung, da er Modelle mit hohen Bandbreitenanforderungen unterstützen kann, die ähnliche Produkte nicht unterstützen können. Was mich an der Turing-Architektur sehr stolz macht, ist, dass sie auch mit einem RT Core ausgestattet ist, der Ray Tracing unterstützt. Nvidia begann erst 2013 mit der Erforschung von RT Core und brachte RT Core nur fünf Jahre später offiziell auf den Markt. Ampere (2020) Im Jahr 2020 veröffentlichte NVIDIA die Ampere-Architektur, die dem in diesem Jahr veröffentlichten A100 einen Leistungssprung mit einer Inferenzgeschwindigkeit von mehr als 1.200 Teraflops ermöglichte. Einer der großen Vorteile der Ampere-Architektur besteht darin, dass sie Sparsity unterstützt. Wir haben festgestellt, dass die meisten neuronalen Netze sparsifiziert werden können, das heißt, das neuronale Netz kann „beschnitten“ werden und eine große Anzahl von Gewichten kann auf 0 gesetzt werden, ohne dass dies Auswirkungen auf seine Genauigkeit hat. Allerdings können unterschiedliche neuronale Netze unterschiedlich stark sparsifiziert werden, was etwas knifflig ist. Beispielsweise kann die Dichte von Faltungs-Neuronalen Netzen ohne Einbußen bei der Genauigkeit auf 30 bis 40 % reduziert werden, während die von vollständig verbundenen neuronalen Netzen auf 10 bis 20 % reduziert werden kann. Die traditionelle Ansicht ist, dass aufgrund der hohen Kosten für den Betrieb von Paketen mit dünner Matrix der Kompromiss nicht so gut ist wie der Betrieb von Paketen mit dichter Matrix, wenn die Dichte nicht unter 10 % reduziert werden kann. Wir haben zunächst mit der Stanford University zusammengearbeitet, um die Sparsität zu untersuchen, und später sehr gute Maschinen gebaut, die effizient laufen können, wenn die Matrixdichte 50 % erreicht. Wir möchten jedoch die Sparse-Matrix im Hinblick auf das Power-Gating effizienter machen Es ist immer noch schwierig, die Matrix zu verbessern, und hier wollen wir immer durchbrechen. Endlich haben wir das Problem überwunden und Ampere entwickelt, und das Geheimnis ist strukturierte Sparsity. Structured Sparse Die Ampere-Architektur legt fest, dass es für jeweils 4 Werte der Matrix nicht mehr als 2 Werte ungleich Null geben darf, d. h. die Gewichte werden um komprimiert Entfernen der Nicht-Null-Werte. Bestimmen Sie durch Eingabe des Codeworts (Codewort), welche Gewichte beibehalten werden sollen, und bestimmen Sie mithilfe des Codeworts, mit welchen Eingabeaktivierungen diese Nicht-Null-Gewichte multipliziert werden sollen, und addieren Sie sie dann, um den Punktmultiplikationsvorgang abzuschließen. Dieser Ansatz ist sehr effizient und ermöglicht es der Ampere-Architektur, die Leistung der meisten neuronalen Netze zu verdoppeln. Darüber hinaus verfügt die Ampere-Architektur über viele Neuerungen. Beispielsweise verfügt Ampere über ein integriertes TF32-Format (TensorFloat-32), das das 8-Bit-Exponentenbit von FP32 und das 10-Bit-Mantissenbit von FP16 kombiniert. Ampere unterstützt auch das BFLOAT-Format. Die Exponentenbits von BFLOAT sind die gleichen wie bei FP32 und die Mantissenbits sind kleiner als bei FP32, sodass es als reduzierte Version von FP32 betrachtet werden kann. Alle oben genannten Datenformate unterstützen Structured Sparse. Unabhängig davon, ob Sie FP16 und TF32 für das Training oder Int8 und Int4 für die Inferenz verwenden, können Sie die hohe Leistung von Structured Sparse nutzen. Da Ampere bei der Quantisierung immer besser wird, kann es auf viele neuronale Netze angewendet werden und eine hohe Leistung gewährleisten. Ampere verfügt über 6 HBM-Stacks und die Bandbreite des HBM-Speichers wurde ebenfalls auf 2 TB/s erhöht. Bei der End-to-End-Inferenz kann die Rechenleistung von Ampere 3,12 TOPS/W (Int8) und 6,24 TOPS/W (Int4) erreichen. Zweitens unterstützt die GPU komplexe Anweisungen. Endlich der Fortschritt der Prozesstechnik. Der Chipherstellungsprozess hat sich von 28 Nanometern auf die heutigen 7 Nanometer weiterentwickelt, was einen gewissen Beitrag zur Verbesserung der GPU-Leistung geleistet hat. Das folgende Beispiel kann Ihnen ein besseres Verständnis der Auswirkung der Kostenteilung vermitteln: Wenn Sie eine HFMA-Operation durchführen, betragen die Operationen „Multiplizieren“ und „Addieren“ insgesamt nur 1,5 pJ (Picojoule, Picojoule), während Anweisungen abgerufen, dekodiert und Operanden abgerufen werden Es erfordert einen Gemeinkostenaufwand von 30 pJ und die Kosten belaufen sich bei der Amortisierung auf bis zu 2000 %. Und wenn eine HDP4A-Operation ausgeführt wird, kann der Overhead auf 8 Operationen verteilt werden, wodurch der Overhead auf 500 % reduziert wird. Beim HMMA-Betrieb beträgt der Overhead nur 22 %, da der Großteil des Energieverbrauchs für die Last verwendet wird, und IMMA ist mit 16 % sogar noch niedriger. Während das Streben nach Programmierbarkeit einen geringen Mehraufwand mit sich bringt, sind die Leistungsverbesserungen, die durch die Einführung eines anderen Designs erzielt werden können, wichtiger.

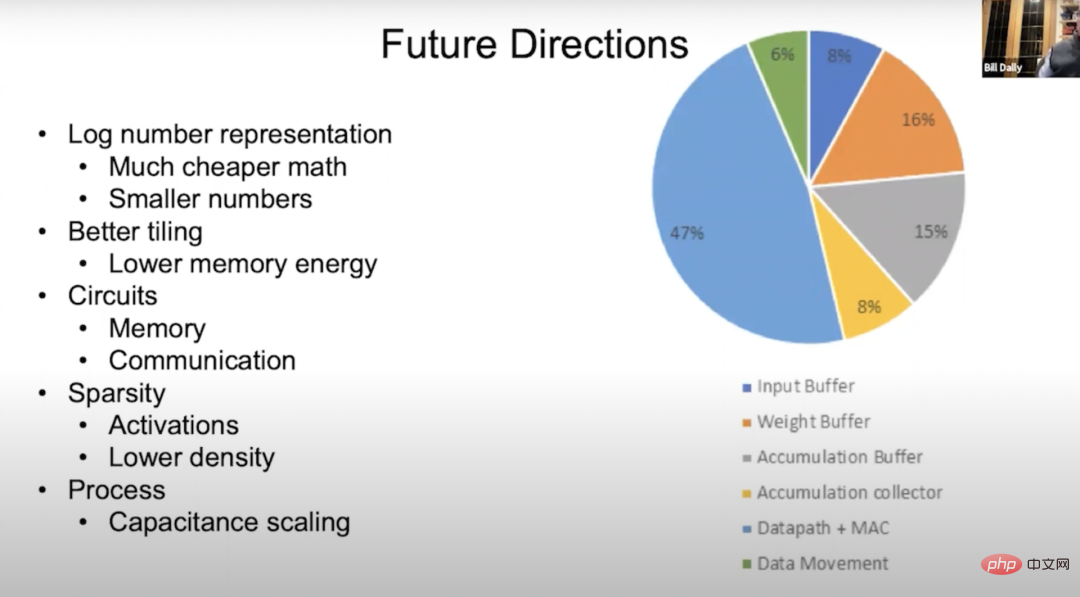

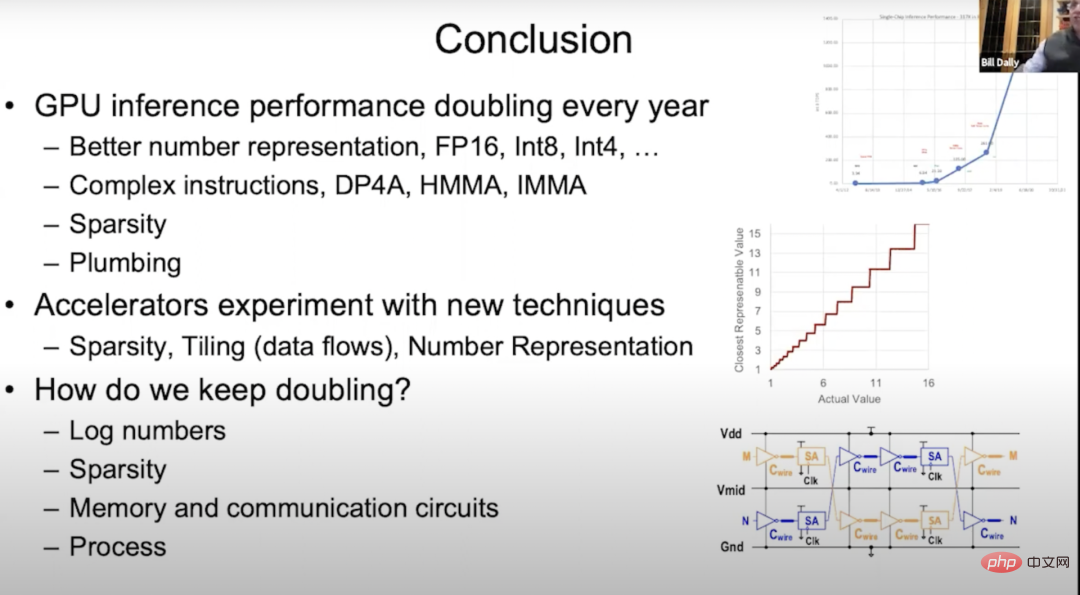

Im Jahr 2020 erwarb NVIDIA Mellanox und kann nun ein komplettes Set an Rechenzentrumslösungen einschließlich Switches und Interconnect für den Aufbau großer GPU-Cluster bereitstellen. Darüber hinaus sind wir mit dem DGX SuperPOD ausgestattet, der in den Top 20 der AI Performance Record 500-Liste rangiert. In der Vergangenheit mussten Benutzer ihre Maschinen anpassen, aber jetzt müssen sie nur noch eine vorkonfigurierte Maschine kaufen, die DGX SuperPOD einsetzen kann, um die hohe Leistung von DGX SuperPOD zu nutzen. Darüber hinaus eignen sich diese Maschinen gut für das wissenschaftliche Rechnen. In der Vergangenheit dauerte es mehrere Monate, ein einzelnes großes Sprachmodell mit einer einzelnen Maschine zu trainieren, aber die Trainingseffizienz kann durch den Aufbau eines GPU-Clusters erheblich verbessert werden, indem GPU-Cluster-Verbindungen optimiert und die Leistung einer einzelnen GPU verbessert werden sind gleichermaßen wichtig. Lassen Sie uns als Nächstes über NVIDIAs Forschungs- und Entwicklungsarbeit an Beschleunigern sprechen. Nvidia betrachtet Beschleuniger als Träger zum Testen neuer Technologien, und erfolgreiche Technologien werden schließlich auf Mainstream-GPUs angewendet. Der Beschleuniger kann folgendermaßen verstanden werden: Er verfügt über eine Matrixmultiplikationseinheit, die von der Speicherhierarchie eingegeben wird, und als Nächstes muss der größte Teil des Energieverbrauchs für Matrixmultiplikationsberechnungen anstelle der Datenverarbeitung verwendet werden. Um dieses Ziel zu erreichen, haben wir etwa 2013 das NVIDIA DLA-Projekt gestartet. Es handelt sich um ein Open-Source-Produkt mit sehr umfassenden unterstützenden Funktionen, das sich nicht von anderen Deep-Learning-Beschleunigern unterscheidet. Aber DLA verfügt über ein großes MAC-Array, das 2048 Int8-, 1024 Int16- oder 1024 FP16-Operationen unterstützt. DLA hat zwei einzigartige Eigenschaften: Erstens unterstützt es die Sparsifizierung. Wir beginnen mit der niedrig hängenden Frucht, einschließlich von DMA zum Unified Buffer und vom Unified Buffer zum MAC-Array. Wir entscheiden, welche Elemente durch die Codierung übrig bleiben, und lösen diese Elemente dann auf und dann zur Berechnung in das MAC-Array eingegeben. Die DLA-Dekomprimierungsmethode ist cleverer. Sie gibt keine Nullwerte in das MAC-Array ein, da dadurch eine Reihe von Daten zu Nullen wird. Stattdessen wird eine separate Leitung zur Darstellung des Nullwerts eingerichtet, und wenn der Multiplikator diese Leitung an einem der Eingänge empfängt, speichert er die Daten im Multiplikator und sendet dann den Ausgang, der sich um keinen numerischen Wert erhöht Gating ist sehr energieeffizient. Die zweite besteht darin, die Winograd-Transformation auf Hardwareebene zu unterstützen. Wissen Sie, wenn Sie eine Faltung durchführen möchten, beispielsweise einen m×n-Faltungskern, benötigen Sie n 2 Multiplikatoren und Addierer im räumlichen Bereich, aber wenn Sie dies im Frequenzbereich tun, benötigen Sie nur Punkt für Punkt Multiplikation. Daher sind große Faltungskernoperationen im Frequenzbereich effizienter als im räumlichen Bereich. Abhängig von der Größe des Faltungskerns kann die Winograd-Transformation bei einigen Bildnetzwerken eine vierfache Leistungsverbesserung bewirken. EIE (2016) 2016 habe ich EIE (Efficient Inference) in Stanford bei meinem damaligen Studenten Han Song (MIT EECS Assistant Professor, ehemaliger Mitbegründer von Shenjian Technology) Engine studiert ). Dies war eine der ersten Untersuchungen zur Sparsifizierung. Wir unterstützen die CSR-Matrixdarstellung (Compressed Sparse Row) auf Hardwareebene. Bei einer Dichte von 50 % ist sie sogar energiesparender als Full-Density-Computing. Später entdeckte ich, dass man, wenn man den Beschleuniger effizienter machen möchte, ein Vektoreinheiten-Array erstellen sollte, damit jede Engine nicht nur eine einzelne Multiplikation-Akkumulierung ausführt, sondern jedes PE (Verarbeitungselement) eine 16-fache Leistung erbringt 16=256 pro Zyklus. Als wir jedoch mit dem Aufbau von Vektorzell-Arrays begannen, stellten wir fest, dass es schwierig war, Sparsity effizient zu erreichen, und wandten uns daher der strukturierten Sparsity zu. Wenn EIE die Skalareinheit verarbeitet, speichert es die Zeigerstruktur in einem separaten Speicher und verarbeitet dann die Zeigerstruktur durch die Pipeline-Stufe, um zu bestimmen, welche Daten multipliziert werden können, führt dann die Multiplikation durch und platziert das Operationsergebnis darin den entsprechenden Ort. Dieser gesamte Prozess läuft sehr effizient ab. Wir haben auch herausgefunden, dass neben dem „Beschneiden“, um Sparsity zu erreichen, die Methode zur Verbesserung der Effizienz neuronaler Netzwerkoperationen die Quantisierung ist. Daher haben wir uns für die Codebuchquantisierung entschieden. Die Codebuch-Quantisierung ist der beste Weg, die Effizienz zu verbessern, wenn es um in Bits ausgedrückte Daten geht. Also haben wir mit dem Codebuch trainiert. Es stellt sich heraus, dass Sie Backpropagation auf alles anwenden können, wenn Sie Backpropagation verwenden können, um den Gradientenabstieg zu erfassen. Deshalb haben wir Backpropagation im Codebuch verwendet, um den optimalen Satz von Codewörtern für eine bestimmte Genauigkeit zu trainieren. Unter der Annahme, dass das Codebuch 7 Bits hat, erhalten Sie 128 Codewörter. Wir finden die optimalen 128 Codewörter im neuronalen Netzwerk für das Training. Die Quantisierung von Codebüchern steht vor einem Problem: Der Aufwand für mathematische Operationen ist hoch. Denn egal wie groß das Codebuch ist und wie hoch der tatsächliche Wert ist, Sie müssen ihn im RAM (Random Access Memory) nachschlagen. Tatsächliche Werte müssen mit hoher Präzision dargestellt werden, und Sie können diese Codewörter nicht genau darstellen. Deshalb haben wir viel Wert auf hochpräzise Mathematik gelegt. Unter dem Gesichtspunkt der Komprimierung funktioniert dies sehr gut, aber unter dem Gesichtspunkt der mathematischen Energie ist es nicht sehr kosteneffektiv, sodass wir diese Technologie in späteren Arbeiten aufgegeben haben. Eyeriss (2016) Joel Emer (beide bei NVIDIA und MIT) und Vivienne Sze am MIT haben Eyeriss entwickelt, das hauptsächlich die Kachelung löst. Das Problem oder wie man die Berechnung einschränkt, ist um die Datenbewegung zu minimieren. Ein typischer Ansatz besteht darin, stationäre Zeilen zu verwenden, Gewichte in Zeilen zu verteilen und Aktivierungen in Spalten auszugeben und den Energieverbrauch durch Datenbewegungen zu minimieren. SCNN (2017) Wir führen derzeit noch Sparsity-Forschung durch. Im Jahr 2017 haben wir eine Maschine namens SCNN (Sparse CNNs) für die Sparse-Kompilierung gebaut (eine Weiterentwicklung neuronaler Netze). Wir haben alle komplexen Probleme im Zusammenhang mit dem Umgang mit Sparsity in die Ausgabe verschoben. Lesen Sie alle Eingabeaktivierungen und finden Sie heraus, wohin sie gehen müssen. Der „f-weite Vektor“ ist hier also eine typische Vektoreingabeaktivierung. Wir werden vier Eingabeaktivierungen gleichzeitig lesen, vier Gewichte, und jede Gewichtung muss mit jeder Eingabeaktivierung multipliziert werden. Es ist nur eine Frage, wo das Ergebnis platziert werden soll, also multiplizieren wir f mit f. Bei der Koordinatenberechnung nehmen wir den Exponenten der Eingabeaktivierung und das Gewicht und berechnen die Position, an der sich das summierte Ergebnis in der Ausgabeaktivierung befinden muss. Anschließend wird eine Datenstreuungsberechnung (scatter_add) für diese Akkumulatorpuffer durchgeführt. Vorher hat alles perfekt funktioniert. Es stellt sich jedoch heraus, dass es keine gute Idee ist, Unregelmäßigkeiten auf die Ausgabe zu übertragen, da in der Ausgabe die Genauigkeit tatsächlich am größten ist. Wenn Sie dazu neigen, zu akkumulieren, führen Sie acht Bits Gewichtung und acht Bits Aktivierung durch, und die Gesamtsumme beträgt 24 Bits. Hier verwenden wir breite Akkumulatoren, um viele Datenbewegungen durchzuführen, was besser ist als eine intensivere Datenbewegung. Allerdings ist die Verbesserung nicht so groß wie gedacht, vielleicht 50 % der Energie der Dichteeinheit. SIMBA (RC18) (2019) Eine weitere Sache, die wir tun werden, ist: 2018 ein Multi-Chip-Modul zu bauen – SIMBA (RC18) mit vorhandenen Beschleunigern. Die Idee von Die Durchführung dieser Forschung erfolgte im Jahr 2008 und dieser Chip demonstrierte auch viele geniale Technologien. Es verfügt über eine gute PE-Architektur und der Chip bietet in der Mitte eine sehr effektive Signalisierungstechnologie. Jetzt skaliert die Architektur auf volle 36 Chips, von denen jeder über eine 4x4-PE-Matrix verfügt, und innerhalb dieser Einheit verfügt jedes PE über 8 breite Vektoreinheiten, sodass wir 128 TOPS Rechenleistung erhalten können, wobei jeder Op 0,1 pJ hat entspricht etwa 10 TOPS/W. Wir haben viel über Kompromisse gelernt. Wir erkannten, dass der Aufbau dieser PE-Arrays dem Aufbau eines sehr großen Designraums ähnelte, in dem es darum ging, wie man die Speicherhierarchie aufbaut, wie man Daten plant usw., also bauten wir ein System namens MAGNET. MAGNET Das obige Bild ist ein Design-Space-Explorationssystem, das 2019 auf der ICCAD (International Conference on Computer-Aided Design) veröffentlicht wurde. Es wird hauptsächlich zur Aufzählung seines Designraums verwendet, wie zum Beispiel: Jede Vektoreinheit sollte haben Wie breit, wie viele Vektoreinheiten gibt es pro PE, wie groß ist der Gewichtspuffer, wie groß ist der Akkumulatorpuffer, wie groß ist der Aktivierungspuffer usw. Später stellte sich heraus, dass wir eine weitere Ebene des Cachings durchführen mussten, also fügten wir einen Gewichtssammler und einen Akkumulatorsammler hinzu. MAGNET-ERGEBNISSE Mit dieser zusätzlichen Caching-Ebene ist es uns endlich gelungen. Dies zeigt, dass der Datenfluss hier unterschiedlich ist und der gewichtete Datenfluss ursprünglich von Sze und Joel durchgeführt wurde. Sie stecken den Großteil Ihrer Energie in Dinge außerhalb des Datenpfads, beispielsweise in Akkumulationspuffer, Gewichtspuffer und Eingabepuffer. Aber mit diesen hybriden Datenströmen sind die Gewichte festgelegt, die lokalen Ausgaben sind festgelegt, die Ausgaben sind festgelegt, die lokalen Gewichte sind festgelegt, Sie können fast zwei Drittel der Energie in den mathematischen Operationen erhalten und Sie können den Energieverbrauch in diesen Speicherarrays reduzieren , also in der Speicherverarbeitung auf einer anderen Ebene der Hierarchie. Damit liegt die Leistung pro Watt nun bei etwa 20 TOPS. VS-Quant Im Jahr 2021 stellten wir auf der MLSYS-Konferenz (The Conference on Machine Learning and Systems, Machine Learning and Systems Conference) VS-Quant als Möglichkeit vor Untersuchung einer Quantisierungsmethode, die hinsichtlich der Komprimierungsbits (wo die Codebuch-Quantisierung gut funktioniert) und des mathematischen Overheads kostengünstig ist. Wir verwenden eine Ganzzahldarstellung, möchten diese jedoch so skalieren, dass der Dynamikbereich von Ganzzahlen dargestellt werden kann. Aber es stellt sich heraus, dass es nicht sehr gut funktioniert, wenn man dies jetzt auf das gesamte neuronale Netzwerk anwendet, da es viele verschiedene Dynamikbereiche im neuronalen Netzwerk gibt. Der Schlüssel zu VS-Quant ist also: Wir haben einen relativ kleinen kleinen Vektor, der einen separaten Skalierungsfaktor auferlegt, und wenn die obige Operation ungefähr auf 32 Gewichtungen angewendet wird, wird der Dynamikbereich viel kleiner sein. Wir können diese Ganzzahlen oben platzieren und sie auch anpassen und optimieren. Vielleicht haben wir die Ausreißer nicht genau dargestellt, aber die restlichen Zahlen wurden besser dargestellt. Auf diese Weise können wir Gewichte und Aktivierungen mit relativ geringer Präzision gegen höhere Genauigkeit eintauschen. Wir haben jetzt also mehrere Skalierungsfaktoren: einer ist der Gewichtsfaktor und einer ist der Aktivierungsfaktor. Kompromiss zwischen Energie, Fläche und Genauigkeit Wir führen diese Operationen grundsätzlich auf Vektorebene durch und die Ergebnisse sind wie in Bert-Base dargestellt. Im Vergleich zum Training ohne Gewichte können wir durch das Training teilweise 20 % Energie und 70 % Platz einsparen. Die grüne Farbe in der obigen Abbildung zeigt an, dass es grundsätzlich keinen Genauigkeitsverlust gibt, Orange und Rot zeigen an, dass die Genauigkeit besser ist . Hoch oder niedriger. Aber selbst im Blau-Level ist die Genauigkeit recht hoch. Mit VS-Quant und einigen anderen Optimierungen haben wir einen Testlauf mit diesen Sprachmodellen durchgeführt. Die Ausführung mit einem Sprachmodell ist viel schwieriger als die Ausführung mit einem Bildmodell, das etwa 120 TOPS/W hat. Beschleuniger Für den Beschleuniger müssen Sie also zunächst einen Matrixmultiplikator erstellen. Wir müssen eine Kachelmethode entwickeln, eine Berechnungsmethode mit sieben verschachtelten Schleifen unter Verwendung neuronaler Netze. Im Wesentlichen werden einige dieser Schleifen auf jede Schicht des Speichersystems kopiert, um die Wiederverwendung der Speicherhierarchie jeder Schicht zu maximieren und die Datenverarbeitung zu minimieren. Wir haben auch Sparsity untersucht, was bei der Komprimierung ziemlich gut ist. Es erhöht grundsätzlich die Speicherbandbreite und die Kommunikationsbandbreite und reduziert den Speicher- und Kommunikationsaufwand. Die nächste Stufe der Sparsity-Entwicklung ist: Wenn Sie einen Nullwert haben, senden Sie einfach eine separate Zeile, die den Nullwert darstellt, ohne in jeder Schleife auf 8 oder 16 Bit umschalten zu müssen. Die Ampere-Architektur kann Multiplikatoren wiederverwenden, indem sie strukturierte Sparsity verwendet. Dies ist eine sehr effiziente Methode und erfordert nur den Overhead einiger Multiplexer (im Grunde vernachlässigbar). Wir können den Multiplikator auch bei Zeigeroperationen wiederverwenden, wodurch wir die doppelte Leistung erzielen können. Zahlendarstellung ist sehr wichtig. Wir begannen mit EIE (Anmerkung des Übersetzers: Efficient Inference Engine, Vortrag von Dr. Han Song auf der ISCA 2016. Realisierte Hardwarebeschleunigung komprimierter, spärlicher neuronaler Netzwerke. ESE gewann mit seiner Approximationsmethode den besten Beitrag von FPGA2017.) und versuchte, ein Codebuch zu erstellen, aber Dies macht die Skalierung mathematisch aufwendig. Schließlich wird die im Beschleuniger erfolgreich getestete Technologie schließlich auf die GPU angewendet. Dies ist eine gute Möglichkeit zum Testen. Die GPU ist eine sehr gute Plattform für domänenspezifische Hardware und das Netzwerk ist reibungslos, sodass Deep-Learning-Anwendungen sehr schnell ausgeführt werden können. Zukünftige Richtungen Lassen Sie uns über die Zukunft der Deep-Learning-Hardware sprechen. Das Bild oben ist ein Energiefluss-Kreisdiagramm. Sie können sehen, dass der größte Teil davon in den Datenpfad fließt. Daher möchten wir dafür sorgen, dass mathematische Operationen weniger Energie verbrauchen . und Datenbewegung. Die grünen sind Datenübertragungen, der Rest sind Eingabepuffer, Gewichtspuffer, Akkumulationspuffer und Akkumulationssammler mit unterschiedlichen Anteilen. Wir versuchen, den Energieverbrauch mathematischer Operationen zu reduzieren. Eine der besten Möglichkeiten besteht darin, ihn auf ein logarithmisches System umzustellen. Denn in einem logarithmischen System wird die Multiplikation zur Addition, und die Addition ist normalerweise viel weniger energieintensiv. Eine andere Möglichkeit besteht darin, auf einen kleineren Wert umzurechnen, was durch VS-Quant erreicht werden kann. Durch eine genauere Quantisierung können wir bei neuronalen Netzen mit Zahlen geringerer Präzision eine gleichwertige Genauigkeit erzielen. Wir hoffen, mit der Kachelung bessere Ergebnisse zu erzielen, beispielsweise durch das Hinzufügen weiterer Ebenen in der Speicherhierarchie, wodurch die Speicherenergie reduziert und auch Speicherschaltkreise und Kommunikationsschaltkreise effizienter werden können. Was die Ampere-Architektur betrifft, ist die Arbeit, die wir bereits an der strukturierten Sparsity leisten, ein guter Anfang, aber ich denke, wir können es besser machen, indem wir die Dichte verringern oder mehrere Dichten wählen, um Aktivierungen und Gewichte anzupassen. Mit der Vertiefung der Forschung wird die Prozesstechnologie auch einige Fortschritte bei der Kapazitätsskalierung bringen. Seit der Veröffentlichung der Kepler-Architektur im Jahr 2012 hat sich die Inferenzleistung der GPU jedes Jahr verdoppelt. Diese Entwicklung ist vor allem auf die immer bessere digitale Darstellung zurückzuführen. Dieses Mal haben wir über viele Inhalte gesprochen, wie zum Beispiel von FP32 über FP16 bis hin zu Int8 und dann Int4 der Kepler-Architektur. Wir haben über die Verwendung komplexerer Punktprodukte durch Zuweisung von Befehls-Overhead gesprochen und akkumulieren in der Volta-Architektur, Ganzzahlmatrixmultiplikation und -akkumulation in der Turing-Architektur sowie Ampere-Architektur und strukturelle Sparsität. Ich habe sehr wenig über Klempnerarbeiten gesprochen, aber Klempnerarbeiten sind sehr wichtig. Mithilfe von Rohrleitungen werden das On-Chip-Speichersystem und das Netzwerk ausgelegt, sodass leistungsstarke Tensorkerne voll ausgenutzt werden können. Damit Tensorkerne in der Turing-Architektur ein Gigabit an Operationen pro Sekunde ausführen und die Daten in die Ausführung gemeinsamer Benchmarks einspeisen können, ist die Anordnung des Zweigspeichers, des On-Chip-Speichers und der Verbindung zwischen ihnen und dem Normalbetrieb sehr wichtig. Mit Blick auf die Zukunft sind wir bereit, verschiedene neue Technologien auf den Beschleuniger anzuwenden. Wie bereits erwähnt, haben wir im MAGNet-Projekt viele Experimente zu Sparsity- und Kacheltechniken durchgeführt und mit verschiedenen Kacheltechniken, numerischen Darstellungen usw. experimentiert. Aber wir fühlen uns immer noch gestresst, denn der Fortschritt des Deep Learning hängt tatsächlich von der kontinuierlichen Verbesserung der Hardwareleistung ab. Die Inferenzleistung der GPU jedes Jahr zu verdoppeln, ist eine große Herausforderung. Tatsächlich sind die Karten in unseren Händen fast ausgespielt, was bedeutet, dass wir mit der Entwicklung neuer Technologien beginnen müssen. Die folgenden vier Richtungen verdienen meiner Meinung nach Aufmerksamkeit: Zunächst Neues lernen digitale Darstellungen, zum Beispiel Logzahl, und ein clevereres Quantisierungsschema als EasyQuant; Abschließend die bestehende Prozesstechnik verbessern. 7 Dejan Milojicic: Wie groß ist eine Matrixfaltung, um den Winograd-Algorithmus in eine effizientere Faltungsimplementierung umzuwandeln?

Ich denke, dass die 3×3-Matrixfaltung sehr effizient ist. Je größer die Faltung, desto höher ist natürlich die Effizienz. Bill Dally: Jeder HBM-Stack hat einen separaten Frame-Puffer, so wie die Ampere-Architektur sechs Stacks hat. Unsere Speicherbandbreite wird berechnet, indem jeder Speichercontroller mit voller Bandbreite läuft. Zwischen jedem GPU-Kern gibt es eine Cache-Schicht, und die Bandbreite unseres On-Chip-Netzwerks beträgt ein Vielfaches der HBM-Bandbreite. Daher müssen wir im Grunde nur einen kleinen Teil des Streaming-Multiprozessors ausführen, um den HBM zu sättigen. Bill Dally: Der Programmierer entscheidet, wo die Daten und Threads abgelegt werden sollen, und Sie starten einfach die Threads und Daten auf der GPU und bestimmen, wo sie ausgeführt werden. Ein großer Vorteil von Systemen, die über NVLink verbunden sind, besteht darin, dass es sich um einen gemeinsam genutzten Adressraum handelt und der Overhead für die Übertragung relativ kleiner Daten ebenfalls recht gering ist. Daher verwenden wir Clusterkommunikation im Netzwerk. Wenn Sie beim Deep Learning Datenparallelität anwenden, führt normalerweise jede GPU dasselbe Netzwerk aus, verarbeitet jedoch unterschiedliche Teile desselben Datensatzes und akkumuliert jeweils Gewichtsgradienten, die Sie dann auf jeder GPU teilen und akkumulieren Sie alle Farbverläufe und addieren Sie sie dann zu den Gewichten. Die Clusterkommunikation beherrscht diese Art von Arbeit sehr gut. Dejan Milojicic: Sollten wir einen universellen Deep-Learning-Beschleuniger für alle Anwendungen entwickeln oder spezielle Beschleuniger wie Sehbeschleuniger oder Beschleuniger für die Verarbeitung natürlicher Sprache? Bill Dally: Ohne die Effizienz zu beeinträchtigen, denke ich, dass die GPU von NVIDIA in Bezug auf die Beschleunigung der Deep-Learning-Effizienz umso besser ist, je allgemeiner sie ist. Was wirklich wichtig ist, ist, dass sich der Bereich des maschinellen Lernens mit unglaublicher Geschwindigkeit weiterentwickelt. Vor ein paar Jahren nutzte jeder noch rekurrente neuronale Netze zur Verarbeitung von Sprache, und dann erschien Transformer und ersetzte RNN blitzschnell. Im Handumdrehen begann jeder, Transformer für die Verarbeitung natürlicher Sprache zu verwenden. Ebenso nutzte noch vor wenigen Jahren jeder CNNs zur Bildverarbeitung. Obwohl viele Menschen immer noch Faltungs-Neuronale Netze verwenden, beginnen immer mehr Menschen, Transformer zur Bildverarbeitung zu verwenden. Daher unterstütze ich keine übermäßige Spezialisierung von Produkten oder die Schaffung dedizierter Beschleuniger für ein bestimmtes Netzwerk, da der Produktdesignzyklus normalerweise mehrere Jahre dauert und die Leute in diesem Zeitraum wahrscheinlich keine Ergebnisse erzielen länger Nutzen Sie diese Art von Netzwerk. Wir müssen ein scharfes Auge haben, um Veränderungen in der Branche rechtzeitig zu erkennen, denn sie entwickelt sich ständig mit alarmierender Geschwindigkeit. Dejan Milojicic: Welchen Einfluss hat das Mooresche Gesetz auf die GPU-Leistung und die Speichernutzung? #🎜🎜 ##### 🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜#Bill Dally:#🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜 #Moores Gesetz das Die Kosten für Transistoren werden von Jahr zu Jahr sinken. Heutzutage nimmt die Zahl der Transistoren, die auf integrierten Schaltkreisen untergebracht werden können, zu, und auch der Chipherstellungsprozess hat einen Sprung von 16 Nanometern auf 7 Nanometer gemacht. Die Dichte der Transistoren auf integrierten Schaltkreisen wird immer größer, aber der Preis eines einzelnen Transistors ist nicht gesunken. Daher denke ich, dass Moores Gesetz etwas veraltet ist. Dennoch ist es gut, mehr Transistoren in einem integrierten Schaltkreis zu haben, damit wir größere GPUs bauen können. Große GPUs verbrauchen auch mehr Strom und sind teurer, aber das ist immer gut, denn wir können Dinge bauen, die wir vorher nicht bauen konnten. Dejan Milojicic: Wenn Entwickler Frameworks wie PyTorch mehr Aufmerksamkeit schenken, was sollten sie dann aus der Weiterentwicklung der Hardware lernen, um sich selbst zu verbessern? ? Deep-Learning-Modelle laufen effizienter? #🎜🎜 ##### 🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜#Bill Dally:#🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜 #Diese Frage ist schwierig zu antworten. Das Framework abstrahiert die Hardware gut, es gibt aber dennoch einige Faktoren, die die Ausführungsgeschwindigkeit Ihres Modells beeinflussen und die es wert sind, untersucht zu werden. Was wir versuchen können, ist, wenn wir eine bessere Technik entwickeln, etwa eine bessere numerische Darstellung, können wir versuchen, verschiedene Techniken mit dem Framework zu kombinieren und herauszufinden, welche davon effektiver ist, was ein unverzichtbarer Teil der Forschungs- und Entwicklungsarbeit ist. Dejan Milojicic: Experimentiert Nvidia mit neuen Verpackungsmethoden? #🎜🎜 ##### 🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜#Bill Dally:#🎜🎜 ## 🎜🎜 ## 🎜🎜 ## 🎜🎜 #Wir haben dirigiert Wir führen verschiedene Experimente mit verschiedenen Verpackungstechnologien durch, um herauszufinden, was sie können und was nicht, damit wir sie zum richtigen Zeitpunkt in Produkte einsetzen können. Einige dieser Projekte befassen sich beispielsweise mit Multi-Chip-Modulen, bei denen Löthöcker und Hybridbonden für die Chipstapelung verwendet werden. Tatsächlich gibt es viele einfache Verpackungstechnologien. Dejan Milojicic: Wer ist im Vergleich zu Nvidias Tensor Core und Googles TPU besser? Bill Dally: Wir wissen nicht viel über Googles neueste TPU, aber die TPUs, die sie zuvor auf den Markt gebracht haben, sind alle dedizierte Engines, im Grunde genommen integrierte große Multiplikatoren und Addierer. Array. NVIDIA vergleicht sich nie mit anderen Unternehmen, und ich denke, das ist die richtige Einstellung. Wenn wir andere blind als Konkurrenten betrachten, wird dies unseren Fortschritt verlangsamen. Anstatt uns so sehr auf das zu konzentrieren, was andere tun, sollten wir uns wirklich auf das konzentrieren, was möglich ist. Was wir tun, ist, als ob wir der Lichtgeschwindigkeit nachjagen. Wir achten mehr darauf, wie wir am besten abschneiden und wie weit wir von der Lichtgeschwindigkeit entfernt sind. Dejan Milojicic: Was denken Sie über Quantencomputing? Sind Quantensimulationen eine natürliche Erweiterung der Deep-Learning-Herausforderungen? Bill Dally: Im März 2021 haben wir ein Software-Entwicklungskit namens „cuQuantum“ veröffentlicht. Auch Google hat bereits zuvor einen Computer mit 53 Qubits entwickelt und behauptet, dieser habe „Quantenüberlegenheit“ erreicht. Einige Berechnungen, die mit herkömmlichen Computern nicht durchgeführt werden können, können mit cuQuantum innerhalb von fünf Minuten abgeschlossen werden. Wenn Sie also wirklich genaue Quantenalgorithmen anstelle der heutigen NIST-Berechnungen (Noisy Intermediate-Scale Quantum) erzielen möchten, sollte die GPU die beste Wahl sein. Nvidias traditioneller GPU-Rechner ist derzeit einer der schnellsten Quantencomputer, und auch Alibaba hat bei ähnlichen klassischen Berechnungen gute Ergebnisse erzielt, was unsere Schlussfolgerung nur bestätigt. Unsere Meinung zum Quantencomputing: Nvidia wird von den Entwicklungen in diesem Technologiebereich nicht überrascht sein. Tatsächlich haben wir auch eine Forschungsgruppe gegründet, um die neuesten Entwicklungen im Bereich Quantencomputing zu verfolgen. IBM hat beispielsweise die Entwicklung eines Chips mit 127 Qubits angekündigt. Wir haben auch Fortschritte in Aspekten wie der Anzahl der Qubits und der Kohärenzzeit verfolgt. In Anbetracht der Anzahl der benötigten Qubits, der Genauigkeit der Qubits, der Interferenz des Quantenrauschens und des für die Quantenfehlerkorrektur erforderlichen Overheads glaube ich nicht, dass Quantencomputing in den nächsten fünf Jahren kommerziell verfügbar sein wird zehn Jahre. Mein optimistischster Ausblick ist, dass man in etwa fünf Jahren damit beginnen wird, quantenchemische Simulationen durchzuführen, was am wahrscheinlichsten sein dürfte. Doch bevor es soweit ist, müssen noch viele physikalische Rätsel gelöst werden. Was viele Menschen noch nicht erkennen, ist, dass Quantencomputer analoge Computer sind und analoge Computer sehr präzise und leicht zu isolieren sein müssen, da sonst jede Kopplung mit der Umgebung zu inkonsistenten Ergebnissen führt. Dejan Milojicic: Wann werden Maschinen Ihrer Meinung nach das Niveau der künstlichen allgemeinen Intelligenz (AGI) erreichen? Bill Dally: Ich habe eine negative Meinung zu diesem Thema. Werfen Sie einen Blick auf einige der erfolgreicheren Anwendungsfälle für künstliche Intelligenz, wie zum Beispiel neuronale Netze, die im Wesentlichen universelle Funktionsfitter sind. Neuronale Netze können eine Funktion durch Beobachtung lernen, daher spiegelt sich ihr Wert immer noch in der künstlichen Wahrnehmung und nicht in der künstlichen Intelligenz wider. Obwohl wir bisher gute Ergebnisse erzielt haben, können wir weiterhin untersuchen, wie wir künstliche Intelligenz und Deep Learning nutzen können, um die Produktivität zu steigern, dadurch die medizinische Versorgung und Bildung zu verbessern und den Menschen ein besseres Leben zu ermöglichen. Tatsächlich brauchen wir dafür kein AGI, sondern sollten uns darauf konzentrieren, wie wir die vorhandene Technologie optimal nutzen können. Bis zur AGI ist es noch ein weiter Weg und wir müssen auch verstehen, was AGI ist.

2 Der 317-fache Anstieg im Laufe des Jahres ist hauptsächlich auf drei Hauptfaktoren zurückzuführen:

Der erste und wichtigste ist die Entwicklung der Zahlendarstellung.

DGX-Box

DGX-Box4 Deep Learning Accelerator: Ein Testgelände für neue Technologien

5 Die Zukunft der Deep-Learning-Hardware

6 Zusammenfassung

Bill Dally:

Das obige ist der detaillierte Inhalt vonNVIDIA Chefwissenschaftler: Vergangenheit, Gegenwart und Zukunft der Deep-Learning-Hardware. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Technologietrends, die Sie im Jahr 2023 im Auge behalten sollten

- Wie künstliche Intelligenz Rechenzentrumsteams neue Alltagsaufgaben beschert

- Können künstliche Intelligenz oder Automatisierung das Problem der geringen Energieeffizienz in Gebäuden lösen?

- OpenAI-Mitbegründer im Interview mit Huang Renxun: Die Argumentationsfähigkeiten von GPT-4 haben noch nicht die Erwartungen erfüllt

- Dank der OpenAI-Technologie übertrifft Bing von Microsoft Google im Suchverkehr