Heim >Technologie-Peripheriegeräte >KI >Details zur Supercomputing-Architektur des Tesla Dojo zum ersten Mal bekannt gegeben! „In Stücke gefickt' für autonomes Fahren

Details zur Supercomputing-Architektur des Tesla Dojo zum ersten Mal bekannt gegeben! „In Stücke gefickt' für autonomes Fahren

- PHPznach vorne

- 2023-04-11 21:46:251340Durchsuche

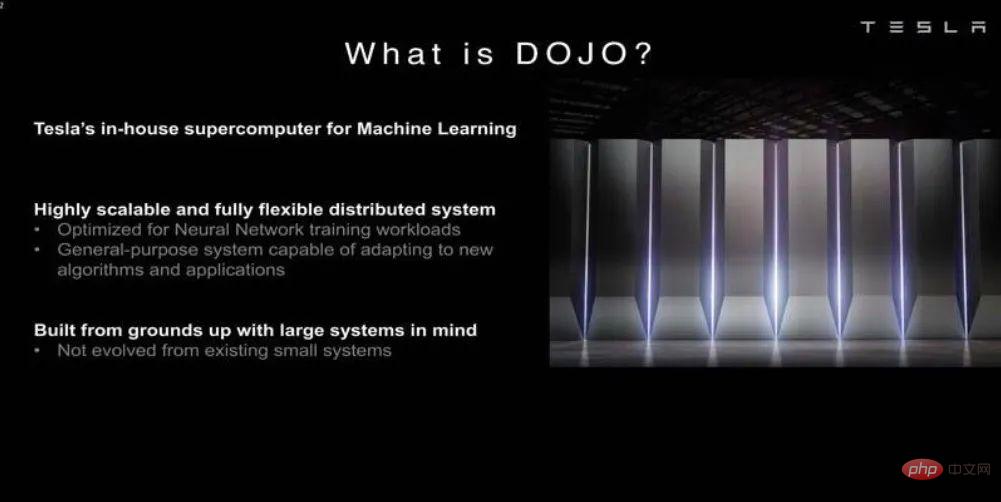

Um der wachsenden Nachfrage nach Modellen für künstliche Intelligenz und maschinelles Lernen gerecht zu werden, hat Tesla eine eigene Technologie für künstliche Intelligenz entwickelt, um Teslas Autos das automatische Fahren beizubringen.

Vor kurzem hat Tesla auf der Hot Chips 34-Konferenz viele Details über die Dojo-Supercomputing-Architektur bekannt gegeben.

Im Wesentlichen ist Dojo ein riesiger zusammensetzbarer Supercomputer, der auf einer vollständig benutzerdefinierten Architektur basiert, die Rechen-, Netzwerk-, Eingabe-/Ausgabechips (I/O) bis hin zu Befehlssatzarchitektur (ISA), Energieübertragung, Verpackung und Kühlung umfasst. All dies geschieht, um benutzerdefinierte, spezifische Trainingsalgorithmen für maschinelles Lernen in großem Maßstab auszuführen.

Ganesh Venkataramanan ist Teslas Senior Director für autonome Fahrhardware und verantwortlich für das Dojo-Projekt und das CPU-Designteam von AMD. Auf der Hot Chips 34-Konferenz stellten er und eine Gruppe von Chip-, System- und Software-Ingenieuren erstmals viele architektonische Merkmale der Maschine vor.

Rechenzentrum „Sandwich“

„Im Allgemeinen besteht der Prozess, den wir zur Herstellung von Chips verwenden, darin, sie auf eine Verpackung zu packen, die Verpackung auf die Leiterplatte zu legen und dann in das System zu gelangen. Das System geht hinein.“ das Gestell“, erklärt Venkataramanan.

Aber es gibt ein Problem bei diesem Prozess: Jedes Mal, wenn Daten vom Chip zum Paket und wieder vom Paket übertragen werden, kommt es zu Latenz und Bandbreitenverlust.

Um diese Einschränkungen zu umgehen, beschlossen Venkataramanan und sein Team, bei Null anzufangen.

So wurden die Trainingsplättchen von Dojo geboren.

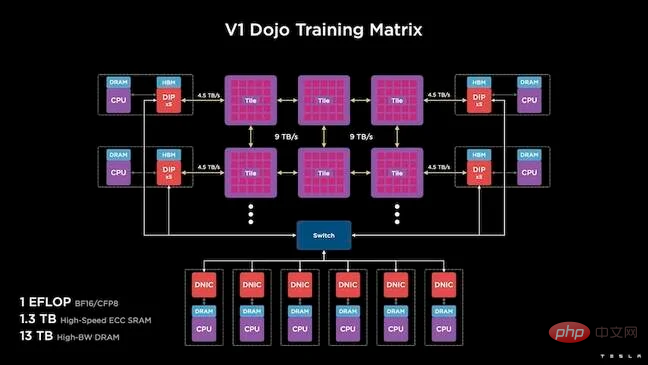

Dies ist ein eigenständiger Computercluster, der einen halben Kubikfuß einnimmt und in einem flüssigkeitsgekühlten 15-kW-Paket 556 TFLOPS FP32-Leistung leisten kann.

Jede Kachel ist mit 11 GB SRAM ausgestattet und über eine 9 TB/s-Fabric unter Verwendung eines benutzerdefinierten Übertragungsprotokolls im gesamten Stapel verbunden.

Venkataramanan sagte: „Dieses Trainingsboard stellt ein beispielloses Maß an Integration vom Computer über den Speicher bis hin zur Stromversorgung und Kommunikation dar, ohne dass zusätzliche Schalter erforderlich sind.“

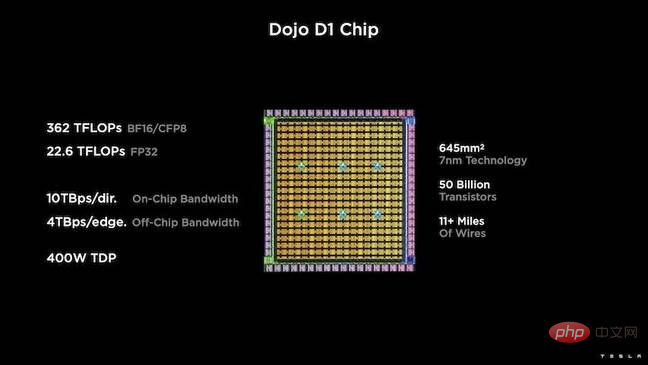

Der Kern der Trainingskachel ist ein speziell Teslas D1, ein 50-Milliarden-Transistorchip, der auf dem 7-nm-Prozess von TSMC basiert. Laut Tesla ist jeder D1 in der Lage, 22 TFLOPS FP32-Leistung bei einer TDP von 400 W zu erreichen.

Tesla nahm dann 25 D1s, teilte sie auf bekanntermaßen gute Formen auf und verpackte sie dann mithilfe der System-on-Wafer-Technologie von TSMC mit extrem geringer Latenz und extrem hoher Bandbreite, die eine massive Rechenintegration ermöglicht.

Das Systemdesign und die vertikale Stapelarchitektur auf dem Chip stellen jedoch die Stromversorgung vor Herausforderungen.

Laut Venkataramanan platzieren die meisten aktuellen Beschleuniger die Stromversorgung direkt neben dem Siliziumwafer. Er erklärte, dass dieser Ansatz zwar effektiv sei, aber bedeute, dass ein großer Teil des Beschleunigers für diese Komponenten reserviert werden müsse, was für Dojo unpraktisch sei. Daher entschied sich Tesla dafür, die Stromversorgung direkt über die Unterseite des Chips bereitzustellen.

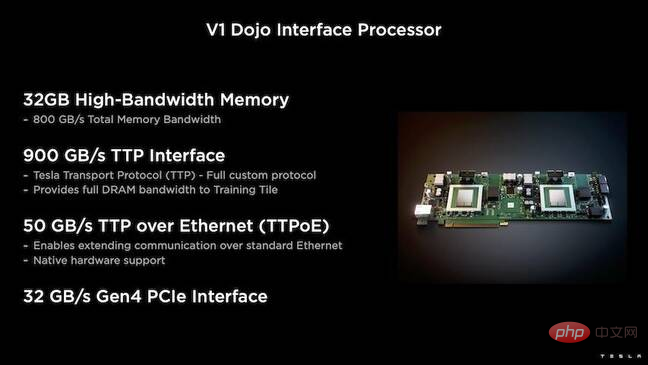

Darüber hinaus hat Tesla den Dojo Interface Processor (DIP) entwickelt, der die Brücke zwischen der Host-CPU und dem Trainingsprozessor darstellt.

Jeder DIP verfügt über 32 GB HBM und bis zu fünf dieser Karten können mit einer Trainingskachel mit 900 GB/s für insgesamt 4,5 TB/s verbunden werden, also insgesamt 160 GB pro Kachel-HBM.

Teslas V1-Konfiguration paart diese Kacheln – oder 150 D1-Chips – in einem Array, um vier Host-CPUs zu unterstützen, die jeweils mit fünf DIP-Karten ausgestattet sind, um die Ansprüche zu erreichen: Ein Exaflop der BF16- oder CFP8-Leistung.

Software

Eine solche spezialisierte Computerarchitektur erfordert einen speziellen Software-Stack. Venkataramanan und sein Team erkannten jedoch, dass die Programmierbarkeit über Erfolg oder Misserfolg von Dojo entscheiden würde.

„Wenn wir diese Systeme entwerfen, ist die einfache Programmierbarkeit durch die Software-Kollegen von größter Bedeutung. Forscher warten nicht darauf, dass Ihre Software-Leute einen handgeschriebenen Kernel schreiben, der die neuen Algorithmen unterstützt, die wir ausführen möchten.“ Zu diesem Zweck gab Tesla die Idee der Verwendung eines Kernels auf und entwarf die Architektur von Dojo um einen Compiler herum.

„Wir verwenden PiTorch. Wir erstellen eine mittlere Ebene, die uns hilft, die Hardware darunter zu parallelisieren. Darunter befindet sich kompilierter Code, um ein Framework zu erstellen, das sich an jede zukünftige Arbeit anpassen kann.“ das ist der einzige Weg.

Venkataramanan betonte zwar die Flexibilität der Software, wies jedoch darauf hin, dass die Plattform, die derzeit in ihrem Labor läuft, vorerst auf Tesla beschränkt ist.

Übersicht über die Dojo-Architektur

Lassen Sie uns nach der Lektüre des oben Gesagten einen tieferen Blick auf die Architektur von Dojo werfen.Tesla verfügt über ein Exascale-System für künstliche Intelligenz für maschinelles Lernen. Tesla verfügt über genügend Kapital, um Mitarbeiter einzustellen und Chips und Systeme speziell für seine Anwendungen zu bauen, genau wie Teslas In-Car-Systeme.

Tesla baut nicht nur einen eigenen KI-Chip, sondern auch einen Supercomputer.

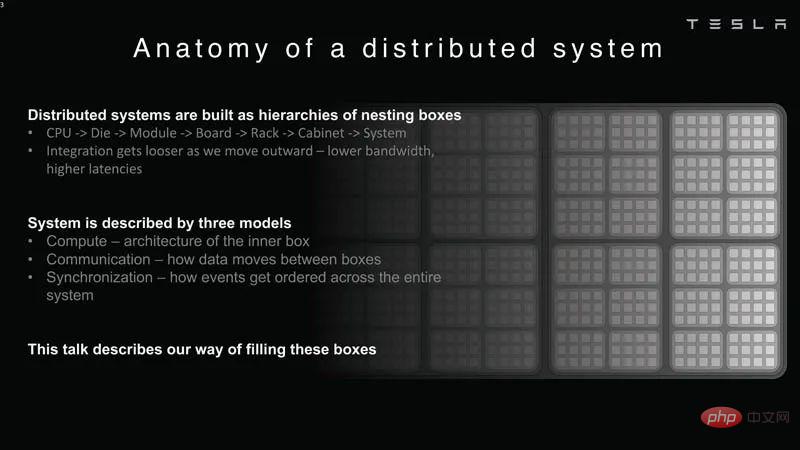

Verteilte Systemanalyse

Verteilte Systemanalyse

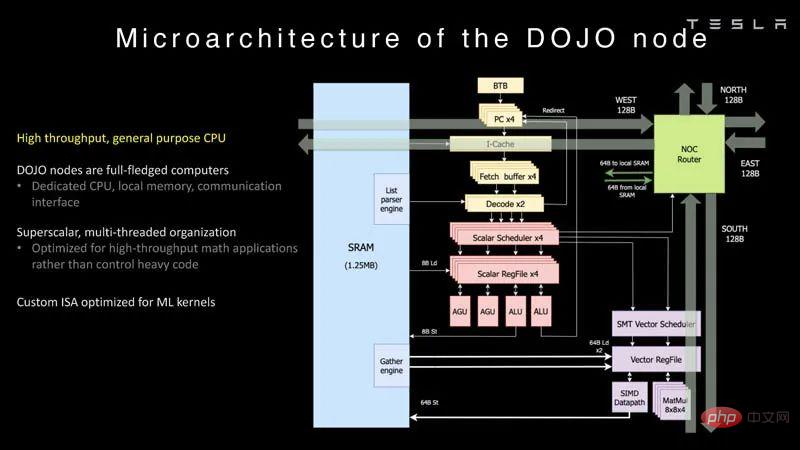

Jeder Knoten von Dojo verfügt über eine eigene CPU, einen eigenen Speicher und eine eigene Kommunikationsschnittstelle.

Dojo-Knoten

Dojo-Knoten

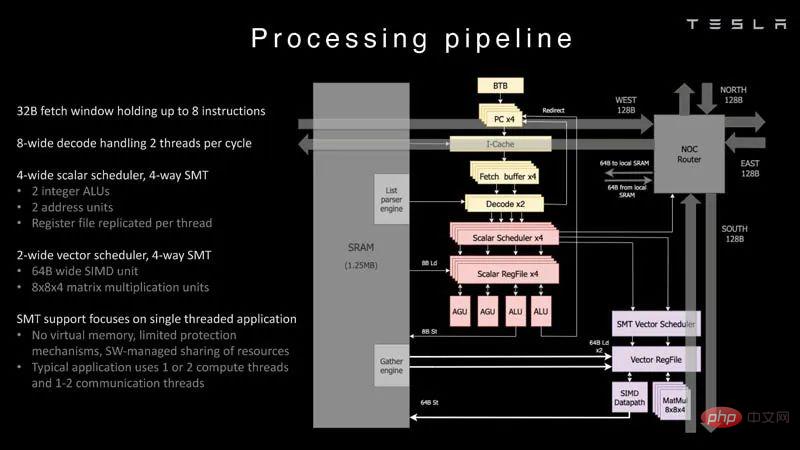

Dies ist die Verarbeitungspipeline des Dojo-Prozessors.

Verarbeitungspipeline

Verarbeitungspipeline

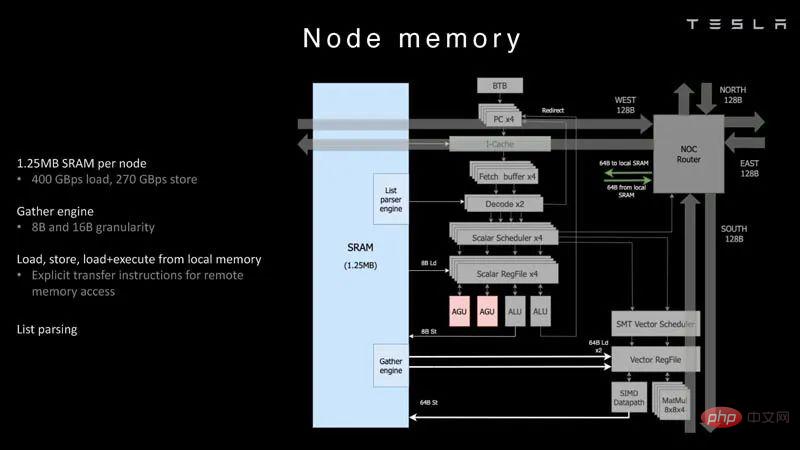

Jeder Knoten verfügt über 1,25 MB SRAM. Bei KI-Trainings- und Inferenz-Chips besteht eine gängige Technik darin, Speicher zusammen mit Berechnungen anzuordnen, um Datenübertragungen zu minimieren, die aus Energie- und Leistungssicht sehr teuer sind.

Knotenspeicher

Knotenspeicher

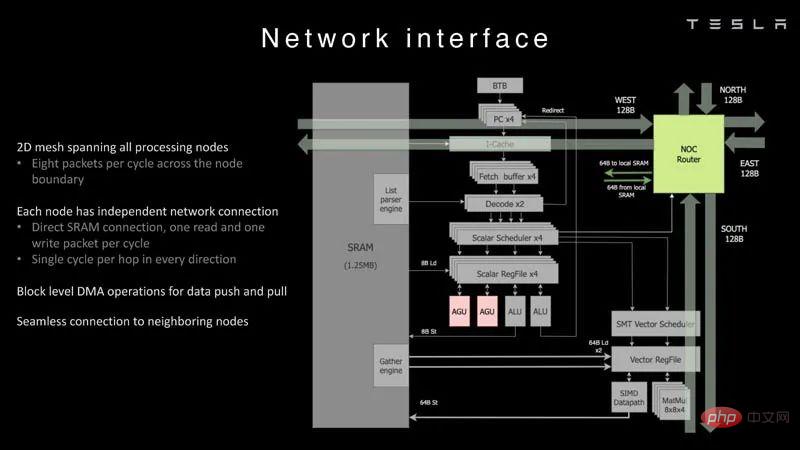

Anschließend wird jeder Knoten mit einem 2D-Gitter verbunden.

Netzwerkschnittstelle

Netzwerkschnittstelle

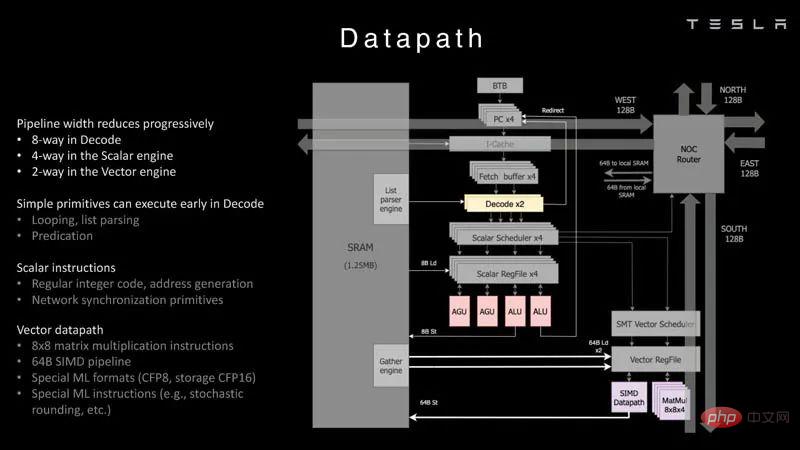

Dies ist eine Übersicht über den Datenpfad.

Datenpfad

Datenpfad

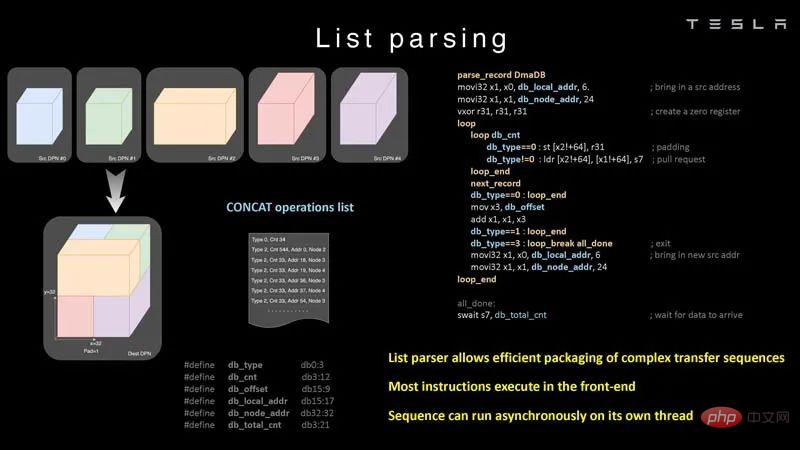

Hier ist ein Beispiel für ein Listenverständnis, das der Chip leisten kann.

List Parsing

List Parsing

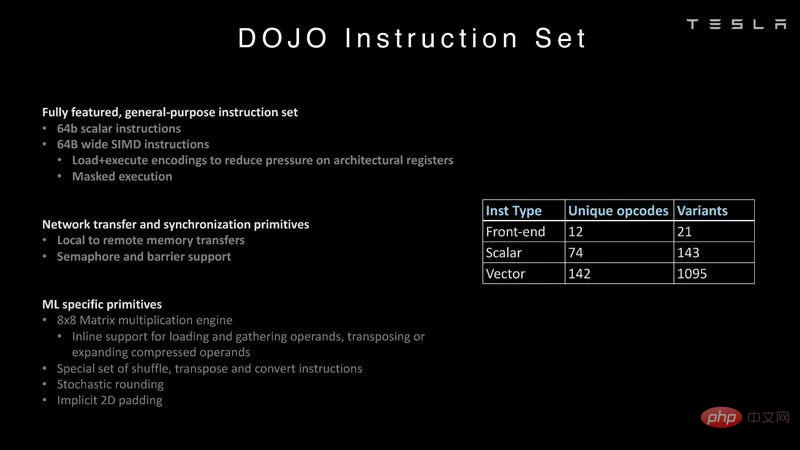

Hier geht es mehr um den ursprünglichen Befehlssatz von Tesla als um den Befehlssatz einer typischen Intel-, Arm-, NVIDIA- oder AMD-CPU/GPU.

Befehlssatz

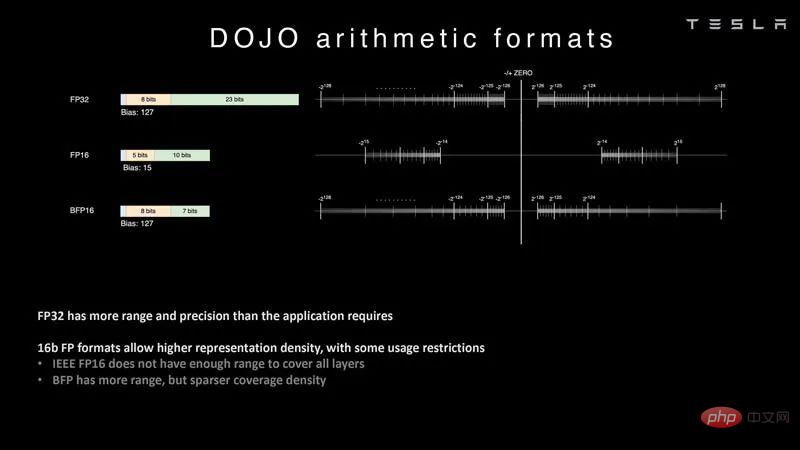

In der künstlichen Intelligenz sind arithmetische Formate wichtig, insbesondere welche Formate der Chip unterstützt. Mit DOJO kann Tesla gängige Formate wie FP32, FP16 und BFP16 untersuchen. Dabei handelt es sich um gängige Branchenformate.

Arithmetisches Format

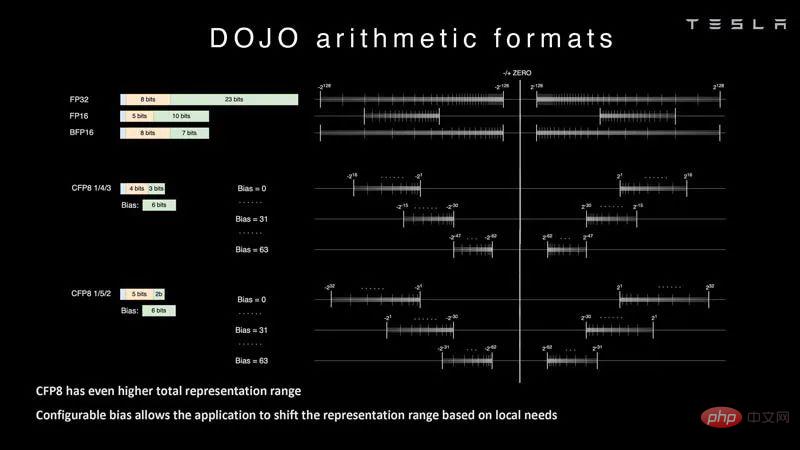

Tesla arbeitet auch an konfigurierbarem FP8 oder CFP8. Es ist in den Bereichen 4/3 und 5/2 erhältlich. Dies ähnelt der NVIDIA H100 Hopper-Konfiguration von FP8. Wir sehen auch den Kern-KI-Beschleuniger Untether.AI Boqueria 1458 RISC-V, der sich auf verschiedene FP8-Typen konzentriert.

Arithmetisches Format 2

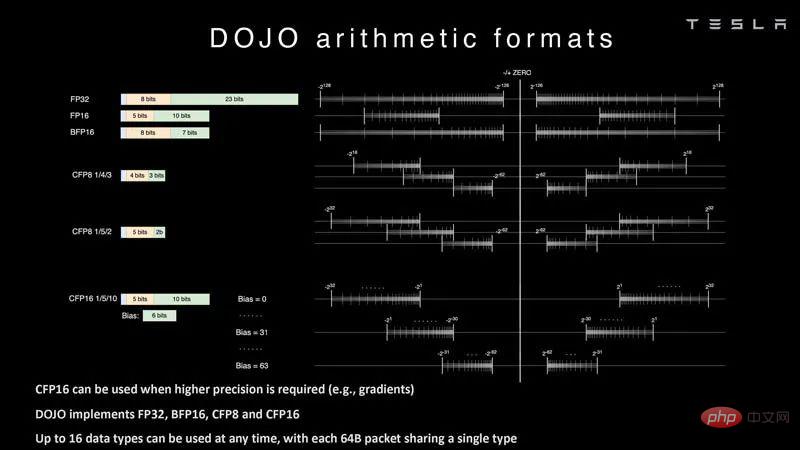

Dojo verfügt außerdem über verschiedene CFP16-Formate für höhere Genauigkeit und unterstützt FP32, BFP16, CFP8 und CFP16.

Arithmetisches Format 3

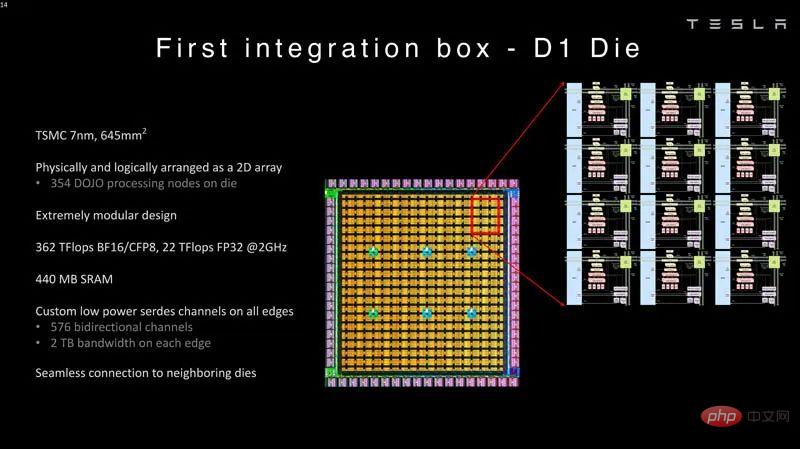

Diese Kerne werden dann in die hergestellte Form integriert. Der D1-Chip von Tesla wird von TSMC im 7-nm-Verfahren hergestellt. Jeder Chip verfügt über 354 Dojo-Verarbeitungsknoten und 440 MB SRAM.

Erste Integrationsbox D1-Form

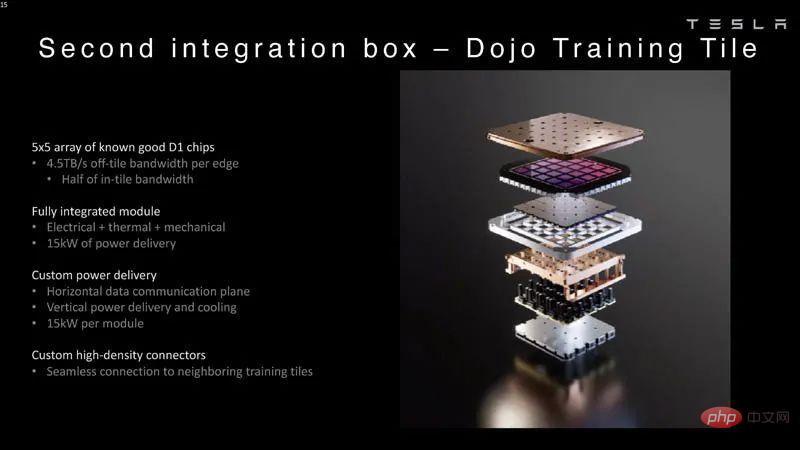

Diese D1-Chips sind auf einer Dojo-Trainingsplatte verpackt. Die D1-Chips werden getestet und dann zu einer 5×5-Kachel zusammengesetzt. Diese Kacheln haben eine Bandbreite von 4,5 TB/s pro Kante. Sie haben außerdem eine Leistungsabgabehüllkurve von 15 kW pro Modul oder etwa 600 W pro D1-Chip nach Abzug der von den 40 I/O-Chips verbrauchten Leistung. Der Vergleich zeigt, warum so etwas wie Lightmatter Passage attraktiver wäre, wenn ein Unternehmen so etwas nicht entwerfen wollte.

Sekundäre Integrationsbox Dojo-Trainingskachel

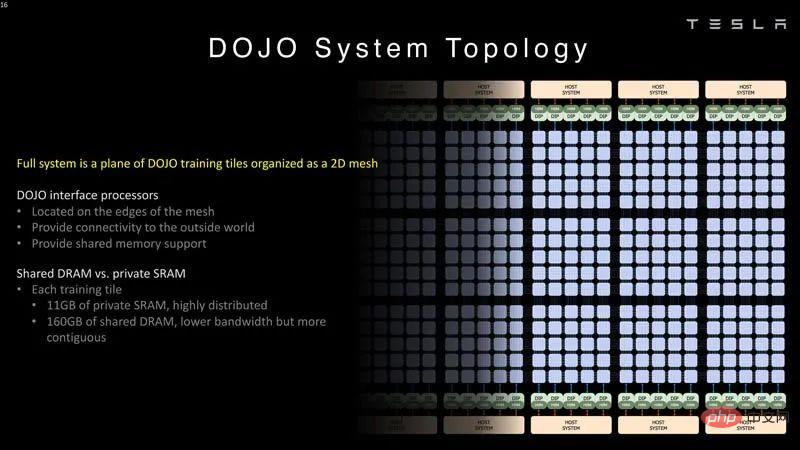

Der Schnittstellenprozessor von Dojo befindet sich am Rand des 2D-Rasters. Jeder Trainingsblock verfügt über 11 GB SRAM und 160 GB gemeinsam genutzten DRAM.

Dojo-Systemtopologie

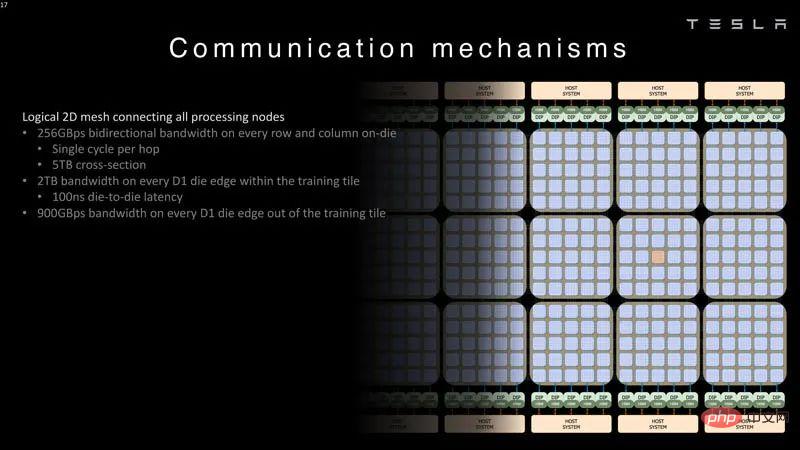

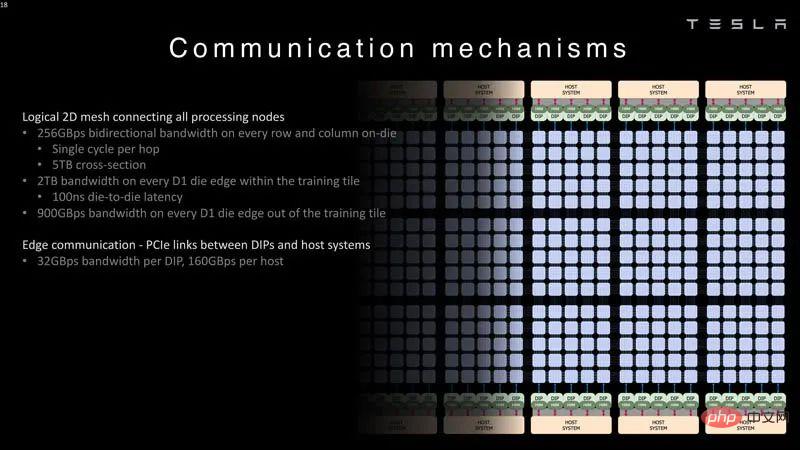

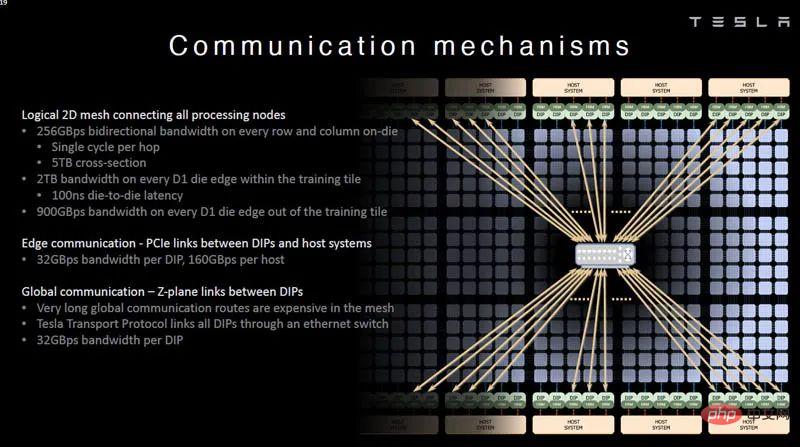

Das Folgende sind die Bandbreitendaten für das 2D-Gitter, das die Verarbeitungsknoten verbindet.

Dojo System Communication Logic 2D Grid

Jedes DIP- und Hostsystem bietet eine 32-GB/s-Verbindung.

Dojo-Systemkommunikation PCIe-Link DIP und Host

Tesla verfügt auch über Z-Flugzeug-Verbindungen für längere Strecken. Im Rest der Rede sprach Tesla über Innovationen auf Systemebene.

Kommunikationsmechanismus

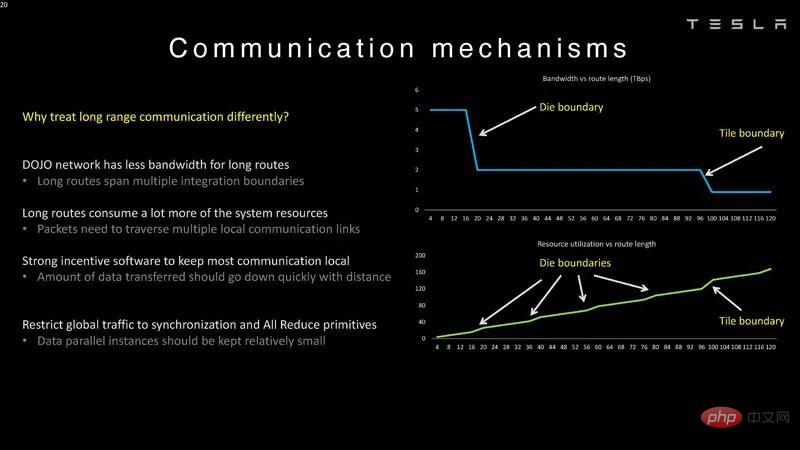

Hier sind die Latenzgrenzen für Würfel und Kacheln, deshalb werden sie in Dojo unterschiedlich behandelt. Der Grund dafür, dass Z-Ebenen-Verbindungen benötigt werden, liegt darin, dass lange Wege teuer sind.

Dojo-Systemkommunikationsmechanismus

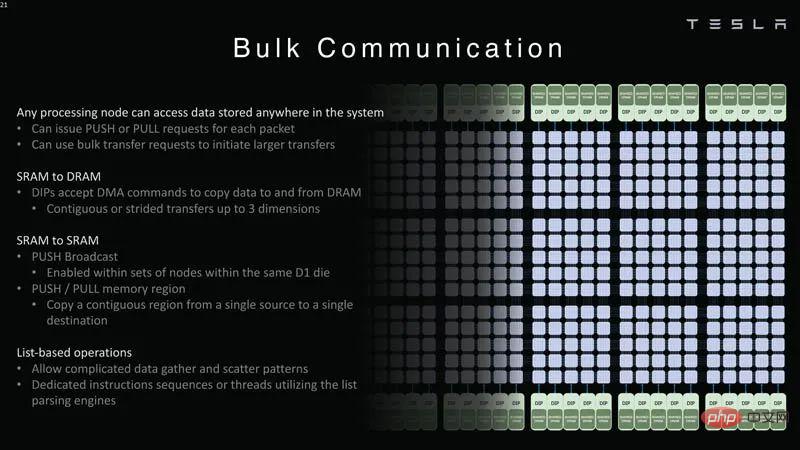

Jeder Verarbeitungsknoten kann auf Daten im gesamten System zugreifen. Jeder Knoten kann Daten in den SRAM oder DRAM pushen oder ziehen.

Dojo System Batch Communication

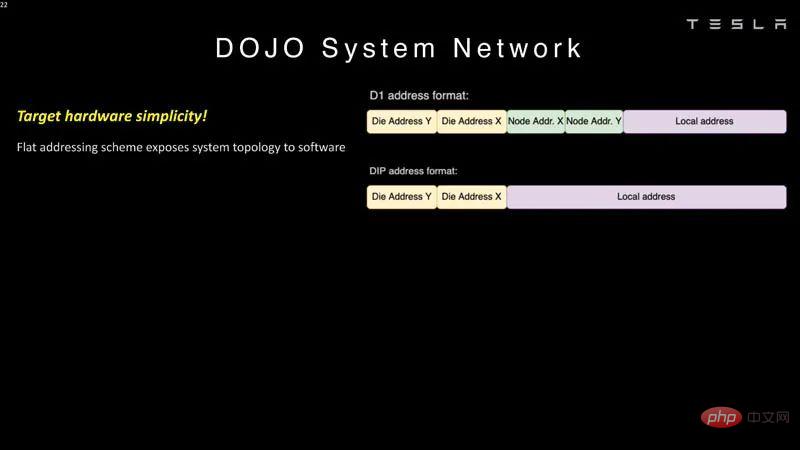

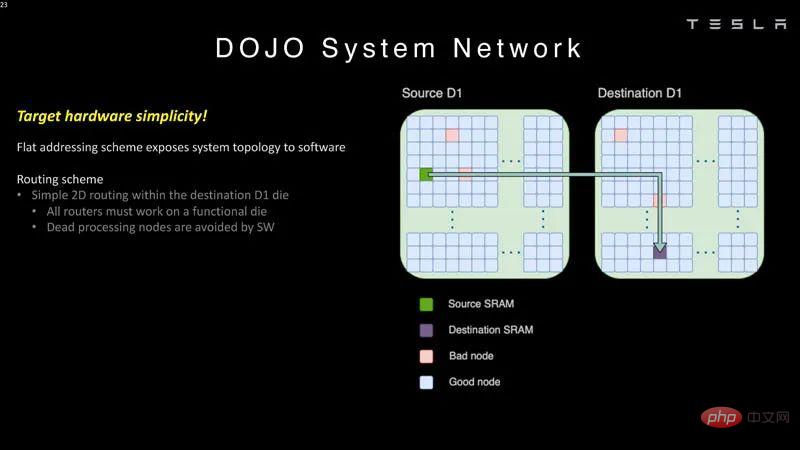

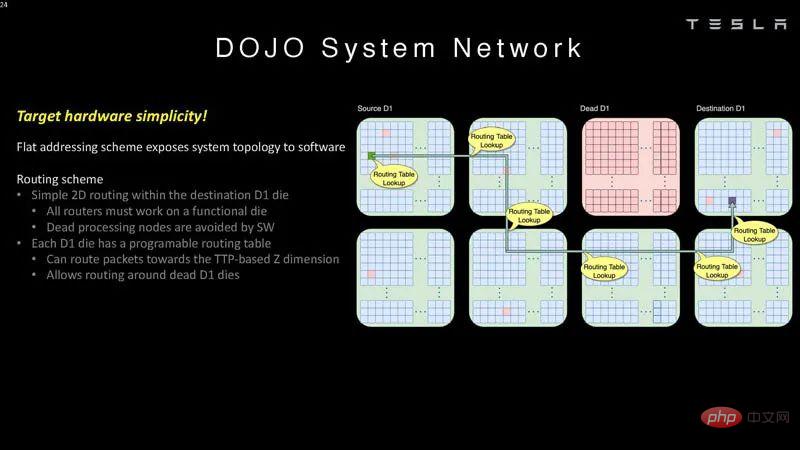

Dojo verwendet ein flaches Adressierungsschema für die Kommunikation.

Systemnetzwerk 1

Diese Chips können fehlerhafte Verarbeitungsknoten in der Software umgehen.

Systemnetzwerk 2

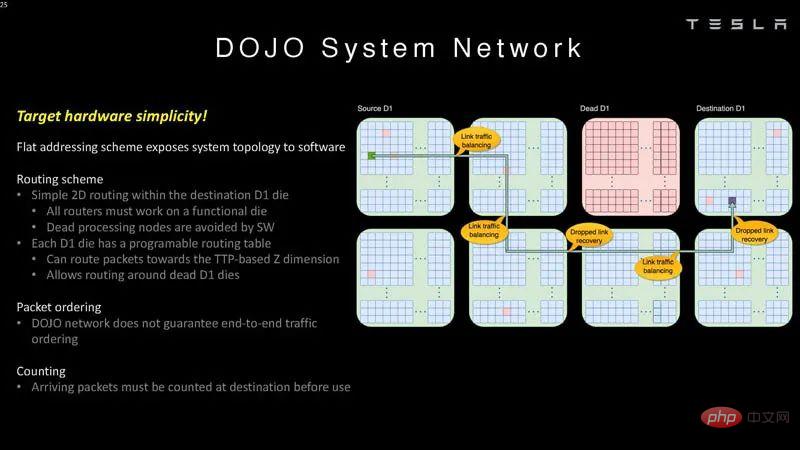

Das bedeutet, dass die Software die Systemtopologie verstehen muss.

Systemnetzwerk 3

Dojo garantiert keine End-to-End-Verkehrsreihenfolge, daher müssen Pakete am Ziel gezählt werden.

Systemnetzwerk 4

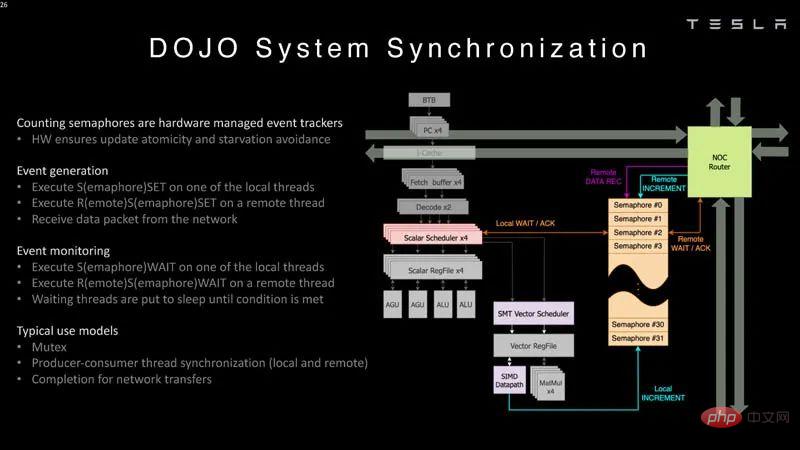

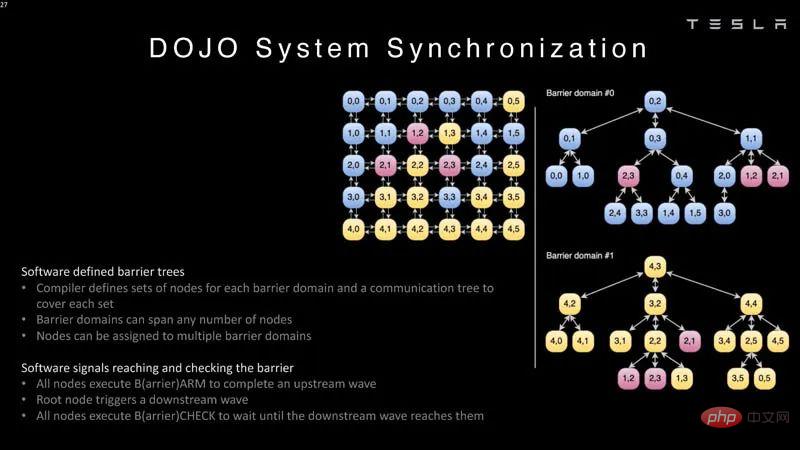

Hier erfahren Sie, wie Pakete als Teil der Systemsynchronisierung gezählt werden.

Systemsynchronisierung

Der Compiler muss einen Baum mit Knoten definieren

.

System Sync 2

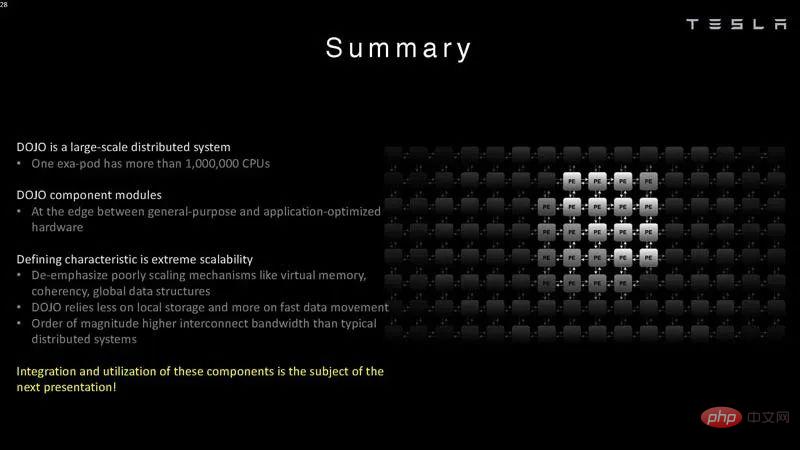

Tesla sagt, dass ein Exa-Pod über mehr als 1 Million CPUs (oder Rechenknoten) verfügt. Das sind große Systeme.

Zusammenfassung

Tesla hat das Dojo speziell für den Einsatz im großen Maßstab gebaut. Typischerweise versuchen Startups, einen oder mehrere KI-Chips pro System zu bauen. Tesla konzentriert sich eindeutig auf größere Größenordnungen.

In vielerlei Hinsicht ist es für Tesla sinnvoll, über ein riesiges KI-Trainingsgelände zu verfügen. Noch spannender ist, dass das Unternehmen nicht nur kommerziell erhältliche Systeme nutzt, sondern auch eigene Chips und Systeme baut. Einige ISAs auf der Skalarseite sind von RISC-V entlehnt, aber die Vektorseite und viele der Architekturen hat Tesla angepasst, sodass dies viel Arbeit erfordert.

Das obige ist der detaillierte Inhalt vonDetails zur Supercomputing-Architektur des Tesla Dojo zum ersten Mal bekannt gegeben! „In Stücke gefickt' für autonomes Fahren. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Technologietrends, die Sie im Jahr 2023 im Auge behalten sollten

- Wie künstliche Intelligenz Rechenzentrumsteams neue Alltagsaufgaben beschert

- Können künstliche Intelligenz oder Automatisierung das Problem der geringen Energieeffizienz in Gebäuden lösen?

- OpenAI-Mitbegründer im Interview mit Huang Renxun: Die Argumentationsfähigkeiten von GPT-4 haben noch nicht die Erwartungen erfüllt

- Dank der OpenAI-Technologie übertrifft Bing von Microsoft Google im Suchverkehr