晶体管,被誉为「20世纪最伟大的发明」。

它的出现为集成电路、微处理器以及计算机内存的产生奠定了基础。

1965年,「摩尔定律」的提出成为半导体行业几十年来的金科玉律。

它表明,每隔 18~24 个月,封装在微芯片上的晶体管数量便会增加一倍,芯片的性能也会随之翻一番。

然而,随着新工艺节点的不断推出,晶体管中原子的数量已经越来越少,种种物理极限制约着摩尔定律的进一步发展。

甚至有人认为摩尔定律已经结束了。

因此,为了「拯救」摩尔定律,工程师们不得不改变晶体管结构,继续减少面积和功耗,并提高其性能。

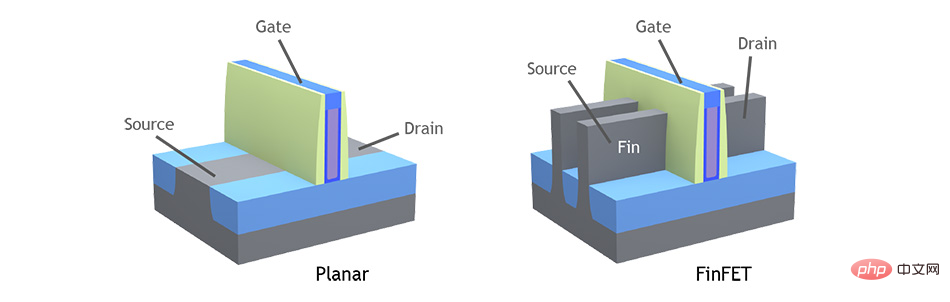

20世纪下半叶,主要流行平面晶体管设计(Planar Transistor)。跨入2010年代,3D鳍形器件(3D fin-shaped devices)逐渐替代了平面设计。

现在,一种全新的晶体管设计结构,即全环绕栅极晶体管(GAA)成为FinFET的继任者,并且即将投入生产。

但是,我们必须看得更远。因为即便是英特尔提出的这种全新晶体管架构RibbonFET,我们在缩小尺寸上的能力也有局限性。

要相信, 3D堆叠的互补金属氧化物半导体 (CMOS) 或 CFET(互补场效应晶体管)将是把摩尔定律延伸到下一个十年的关键。

晶体管的演变

每个金属氧化物半导体场效应晶体管(MOSFET)都有一套相同的基本部件:

栅极叠层 (gate stack) 、沟道区 (channel region) 、源极 (source) 、漏极 (drain)

源极和漏极经过化学掺杂,使它们要么富含移动电子(n型),要么缺乏它们(p型)。沟道区具有与源极和漏极相反的掺杂。

2011年之前的先进微处理器中的平面版本晶体管中,MOSFET的栅极叠层刚好在沟道区的上方,是用来将电场投射到沟道区域。

向栅极施加足够大的电压 (相对于源极) ,就会在通道区域形成一层移动电荷载流子,这样就能让电流在源极和漏极之间流动。

为了缩小平面晶体管设计的尺寸,一种「短沟道效应」成为物理家们的焦点。

因为随着制程技术不断提升时,晶体管中栅极的宽度被挤压的越来越小。要知道,当这个栅极低于20nm时,就会对电流失控,源极的电流会穿透栅极,直接到达漏极。

这时,就会出现「漏电」现象,这会让芯片能耗急剧上升。

为了解决这个问题,一种全新的FinFET晶体管技术提出了。它将栅极包裹在三个侧面的沟道周围,以提供更好的静电控制。

FinFET与上一代平面架构相同的性能水平下将功耗降低了约 50%。FinFET 的切换速度也更快,性能提升了 37%。

2011年,英特尔在其推出的22nm节点上引入了FinFET,并将其用在了第三代酷睿处理器的生产。

从那时起,FinFET就成为摩尔定律的主力。

然而,我们在转向FinFET的同时,也失去了一些东西。

在平面器件中,晶体管的宽度由光刻定义,因此它是一个高度灵活的参数。

但在 FinFET 中,晶体管宽度以离散增量(discrete increments)的形式出现,即每次添加一个鳍。这一特性通常被称为鳍量化(fin quantization)。

尽管 FinFET 很灵活,但鳍量化仍然是一个重要的设计约束。围绕它的设计规则,以及增加更多鳍片以提高性能的愿望增加了逻辑单元的整体面积,并使将单个晶体管变成完整逻辑电路的互连堆栈复杂化。

它还增加了晶体管的电容,从而降低了它的开关速度。因此,虽然FinFET作为行业主力为我们提供了很好的服务,但仍需要一种新的、更精细的方法。

正是这种方法引导物理学家们发明了即将推出的3D晶体管——RibbonFET。

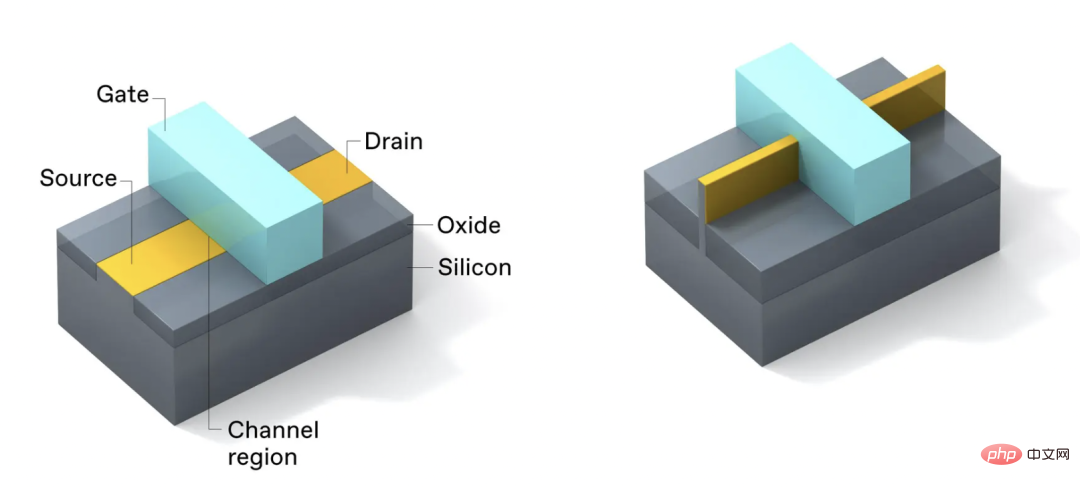

在RibbonFET中,栅极环绕晶体管沟道区域以增强对电荷载流子的控制。新结构还可以实现更好的性能和更精细的优化。

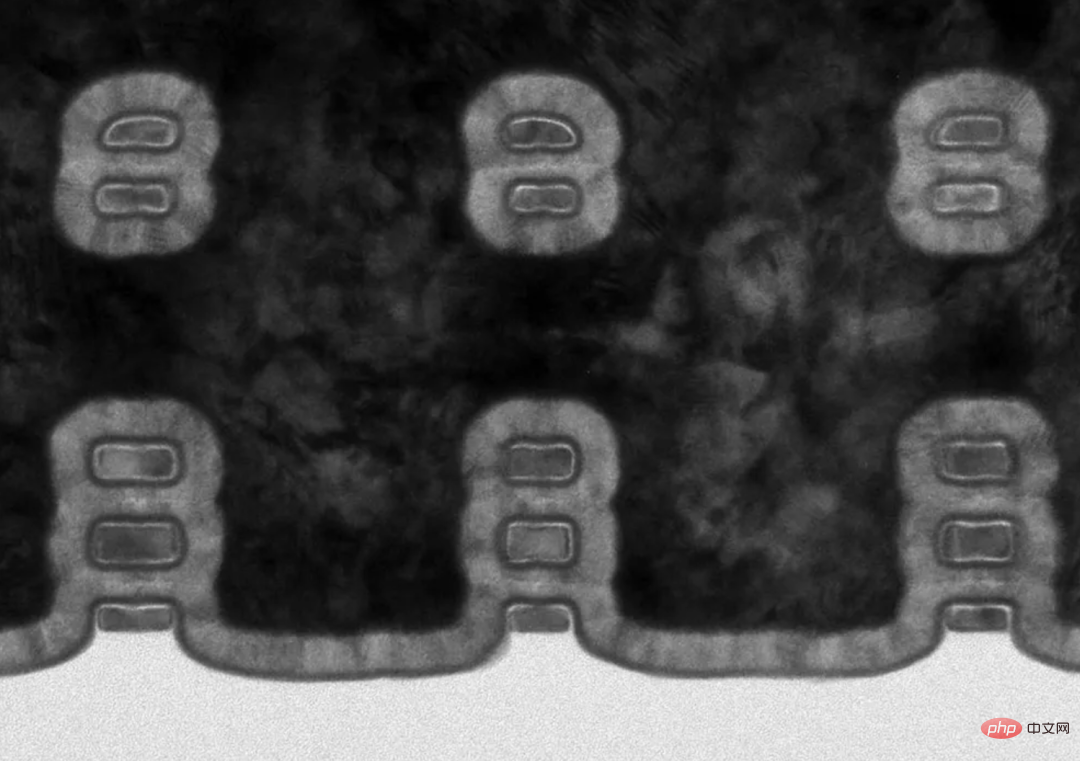

具体来讲,栅极完全围绕沟道,对沟道内的电荷载流子提供更严格的控制,这些沟道现在由纳米级硅带形成。

使用这些纳米带(纳米片),就可以再次使用光刻技术根据需要改变晶体管的宽度。

去除量化约束后,便可以为应用程序生成适当大小的宽度。这样就使我们能够平衡功率、性能和成本。

更重要的是,通过堆叠和并行操作,设备可以驱动更多的电流,不增加面积的情况下也能提升性能。

因此,英特尔认为RibbonFET是在合理功率下实现更高性能的最佳选择。

他们将在2024年Intel 20A工艺上引入RibbonFET结构。

3D堆叠CMOS

平面型、FinFET 和 RibbonFET 晶体管的一个共同点是,都使用 CMOS 技术,如前所述,CMOS 由 n 型和 p 型晶体管组成。这一技术在20世纪80年代开始成为主流,因为它比其他替代技术吸收的电流要少得多。更少的电流意味着更高的工作频率和更高的晶体管密度。

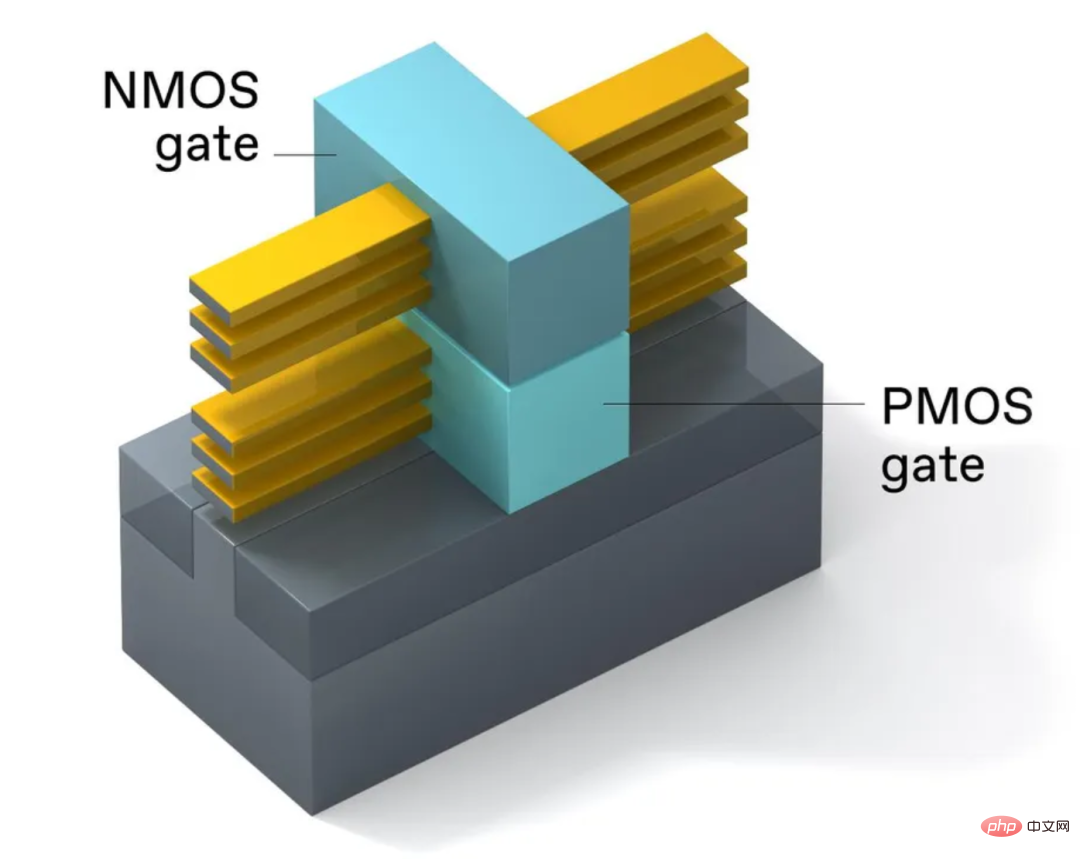

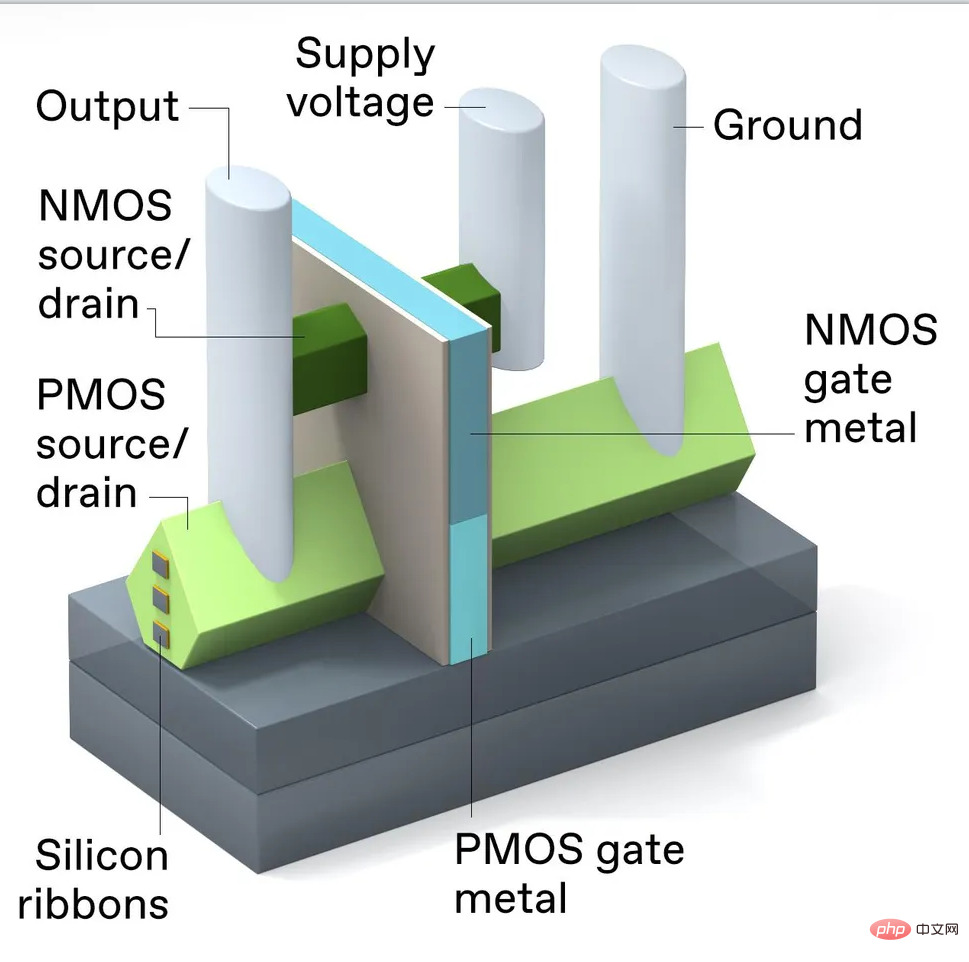

迄今为止,所有的 CMOS 技术将标准的 NMOS 和 PMOS 晶体管对并排放置。但是在2019年 IEEE 国际电子元件会议(IEDM)的主题演讲中,提出了一个「3D堆叠」晶体管的概念,将 NMOS 晶体管置于 PMOS 晶体管之上。

在 IEDM 2020上,提出了第一个使用这种3D技术的逻辑电路的设计的逆变器。3D 堆叠 CMOS 有效地减少了一半的逆变器足迹,将晶体管面积密度提升一倍,进一步推高了摩尔定律的极限。

3D 堆叠 CMOS结构,将 PMOS 器件放置在 NMOS 器件的顶部,总面积与一个 RibbonFET 面积相同。NMOS 和 PMOS 门使用不同的金属材料

要利用3D堆叠CMOS,要解决许多工艺集成上的挑战,其中一些涉及到CMOS加工制造的极限。

如何实现呢?自对齐的3D CMOS的制造始于硅晶片。在晶片上,我们沉积了一层又一层的硅和硅锗,这种结构被称为「超晶格」。然后用光刻图案来切除超晶格的一部分,留下一个鳍状结构。超晶格晶体为后续开发过程提供了强大的支撑结构。

接下来在超晶格上放置一块「假的」多晶硅,保护前者不受下一步操作的影响。这一步骤被称为垂直堆叠的双源/漏过程,在顶部纳米带(未来的NMOS位置)的两端生长掺磷硅,同时在底部纳米带(未来的 PMOS位置)上选择性地生长掺硼硅锗。之后,在电源周围放置电介质,通过放电使它们彼此隔离。

3D 堆叠有效地使每平方毫米 CMOS 晶体管密度翻倍,实际密度取决于所涉及的逻辑单元的复杂性。

最后是门的构建。首先移除之前安装的假门,暴露出硅纳米带。接下来只蚀刻掉锗硅,释放出一堆平行的硅纳米带,这就是晶体管的沟道区域。

然后在纳米带的四面涂上一层极薄的绝缘层,这层绝缘层具有很高的介电常数。纳米带通道是如此之小,无法像平面晶体管那样有效地以化学方式涂敷。

用一种金属环绕底部的纳米带形成一个 p 掺杂通道,顶部的纳米带与另一个纳米带形成一个 n 掺杂通道。这样,门堆栈构建完成,两个晶体管安装完毕。

这个过程可能看起来很复杂,但它比另一种技术( 顺序3D堆叠 )要好。如果使用后者,NMOS 器件和 PMOS 器件要安装在分离的晶片上,然后把两者合在一起,将PMOS层转移到 NMOS 晶片上。而自对齐3D堆叠方法加工步骤较少,可以更严格的控制制造成本。

而且更重要的是,这种自对齐方法还避免了在连接两片晶圆时可能发生的对准错误问题。制作所有需要的连接到3D堆叠CMOS 挑战性很高。电源连接将需要从下面的设备堆栈。在设计上,NMOS 器件[上]和 PMOS 器件[下]有单独的源/漏接触,但是两个器件共用一个栅极。

值得注意的是,需要优化 NMOS 和 PMOS 之间的垂直间距:如果太短,就会增加寄生电容,如果太长,就会增加两个设备之间互连的电阻。无论哪种极端情况都会导致电路变慢,消耗更多的电力。

许多设计研究,如美国 TEL 研究中心在 IEDM 2021会议上提出的一项研究,提出在3D CMOS 有限的空间内提供所有必要的互连,这样做不会显著增加它们构成的逻辑单元的面积。该研究表明,在寻找最佳互连选择方面存在许多创新的机会。

摩尔定律的未来

有了带状场效应晶体管和3D CMOS,我们就有了一条为摩尔定律续命明确路线,至少可以续到2024年以后。

在2005年的一次采访中,摩尔定律的提出者戈登 · 摩尔承认「自己时不时地对取得的进步感到惊讶」。

他说,「一路走来,有好几次我都以为我们已经走到了尽头,结果我们的创意无限工程师们想出了克服困难的办法。」

随着晶体管制造工艺经过 FinFET,并随着不断优化来到RibbonFET时代, 最终向3D堆叠 CMOS工艺的迈进,我们预计,留给戈登·摩尔先生的惊讶不久还会到来的。

以上是晶体管救命稻草来了:3D堆叠CMOS,摩尔定律又续10年?的详细内容。更多信息请关注PHP中文网其他相关文章!

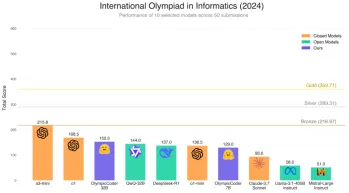

拥抱面部是否7B型号奥林匹克赛车击败克劳德3.7?Apr 23, 2025 am 11:49 AM

拥抱面部是否7B型号奥林匹克赛车击败克劳德3.7?Apr 23, 2025 am 11:49 AM拥抱Face的OlympicCoder-7B:强大的开源代码推理模型 开发以代码为中心的语言模型的竞赛正在加剧,拥抱面孔与强大的竞争者一起参加了比赛:OlympicCoder-7B,一种产品

4个新的双子座功能您可以错过Apr 23, 2025 am 11:48 AM

4个新的双子座功能您可以错过Apr 23, 2025 am 11:48 AM你们当中有多少人希望AI可以做更多的事情,而不仅仅是回答问题?我知道我有,最近,我对它的变化感到惊讶。 AI聊天机器人不仅要聊天,还关心创建,研究

Camunda为经纪人AI编排编写了新的分数Apr 23, 2025 am 11:46 AM

Camunda为经纪人AI编排编写了新的分数Apr 23, 2025 am 11:46 AM随着智能AI开始融入企业软件平台和应用程序的各个层面(我们必须强调的是,既有强大的核心工具,也有一些不太可靠的模拟工具),我们需要一套新的基础设施能力来管理这些智能体。 总部位于德国柏林的流程编排公司Camunda认为,它可以帮助智能AI发挥其应有的作用,并与新的数字工作场所中的准确业务目标和规则保持一致。该公司目前提供智能编排功能,旨在帮助组织建模、部署和管理AI智能体。 从实际的软件工程角度来看,这意味着什么? 确定性与非确定性流程的融合 该公司表示,关键在于允许用户(通常是数据科学家、软件

策划的企业AI体验是否有价值?Apr 23, 2025 am 11:45 AM

策划的企业AI体验是否有价值?Apr 23, 2025 am 11:45 AM参加Google Cloud Next '25,我渴望看到Google如何区分其AI产品。 有关代理空间(此处讨论)和客户体验套件(此处讨论)的最新公告很有希望,强调了商业价值

如何为抹布找到最佳的多语言嵌入模型?Apr 23, 2025 am 11:44 AM

如何为抹布找到最佳的多语言嵌入模型?Apr 23, 2025 am 11:44 AM为您的检索增强发电(RAG)系统选择最佳的多语言嵌入模型 在当今的相互联系的世界中,建立有效的多语言AI系统至关重要。 强大的多语言嵌入模型对于RE至关重要

麝香:奥斯汀的机器人需要每10,000英里进行干预Apr 23, 2025 am 11:42 AM

麝香:奥斯汀的机器人需要每10,000英里进行干预Apr 23, 2025 am 11:42 AM特斯拉的Austin Robotaxi发射:仔细观察Musk的主张 埃隆·马斯克(Elon Musk)最近宣布,特斯拉即将在德克萨斯州奥斯汀推出的Robotaxi发射,最初出于安全原因部署了一支小型10-20辆汽车,并有快速扩张的计划。 h

AI震惊的枢轴:从工作工具到数字治疗师和生活教练Apr 23, 2025 am 11:41 AM

AI震惊的枢轴:从工作工具到数字治疗师和生活教练Apr 23, 2025 am 11:41 AM人工智能的应用方式可能出乎意料。最初,我们很多人可能认为它主要用于代劳创意和技术任务,例如编写代码和创作内容。 然而,哈佛商业评论最近报道的一项调查表明情况并非如此。大多数用户寻求人工智能的并非是代劳工作,而是支持、组织,甚至是友谊! 报告称,人工智能应用案例的首位是治疗和陪伴。这表明其全天候可用性以及提供匿名、诚实建议和反馈的能力非常有价值。 另一方面,营销任务(例如撰写博客、创建社交媒体帖子或广告文案)在流行用途列表中的排名要低得多。 这是为什么呢?让我们看看研究结果及其对我们人类如何继续将

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

Video Face Swap

使用我们完全免费的人工智能换脸工具轻松在任何视频中换脸!

热门文章

热工具

SublimeText3 Linux新版

SublimeText3 Linux最新版

VSCode Windows 64位 下载

微软推出的免费、功能强大的一款IDE编辑器

MinGW - 适用于 Windows 的极简 GNU

这个项目正在迁移到osdn.net/projects/mingw的过程中,你可以继续在那里关注我们。MinGW:GNU编译器集合(GCC)的本地Windows移植版本,可自由分发的导入库和用于构建本地Windows应用程序的头文件;包括对MSVC运行时的扩展,以支持C99功能。MinGW的所有软件都可以在64位Windows平台上运行。

Dreamweaver Mac版

视觉化网页开发工具

DVWA

Damn Vulnerable Web App (DVWA) 是一个PHP/MySQL的Web应用程序,非常容易受到攻击。它的主要目标是成为安全专业人员在合法环境中测试自己的技能和工具的辅助工具,帮助Web开发人员更好地理解保护Web应用程序的过程,并帮助教师/学生在课堂环境中教授/学习Web应用程序安全。DVWA的目标是通过简单直接的界面练习一些最常见的Web漏洞,难度各不相同。请注意,该软件中