UCIe 2.0:透過 3D 封裝和可管理性推進開放式小晶片生態系統

- PHPz原創

- 2024-08-08 12:51:201123瀏覽

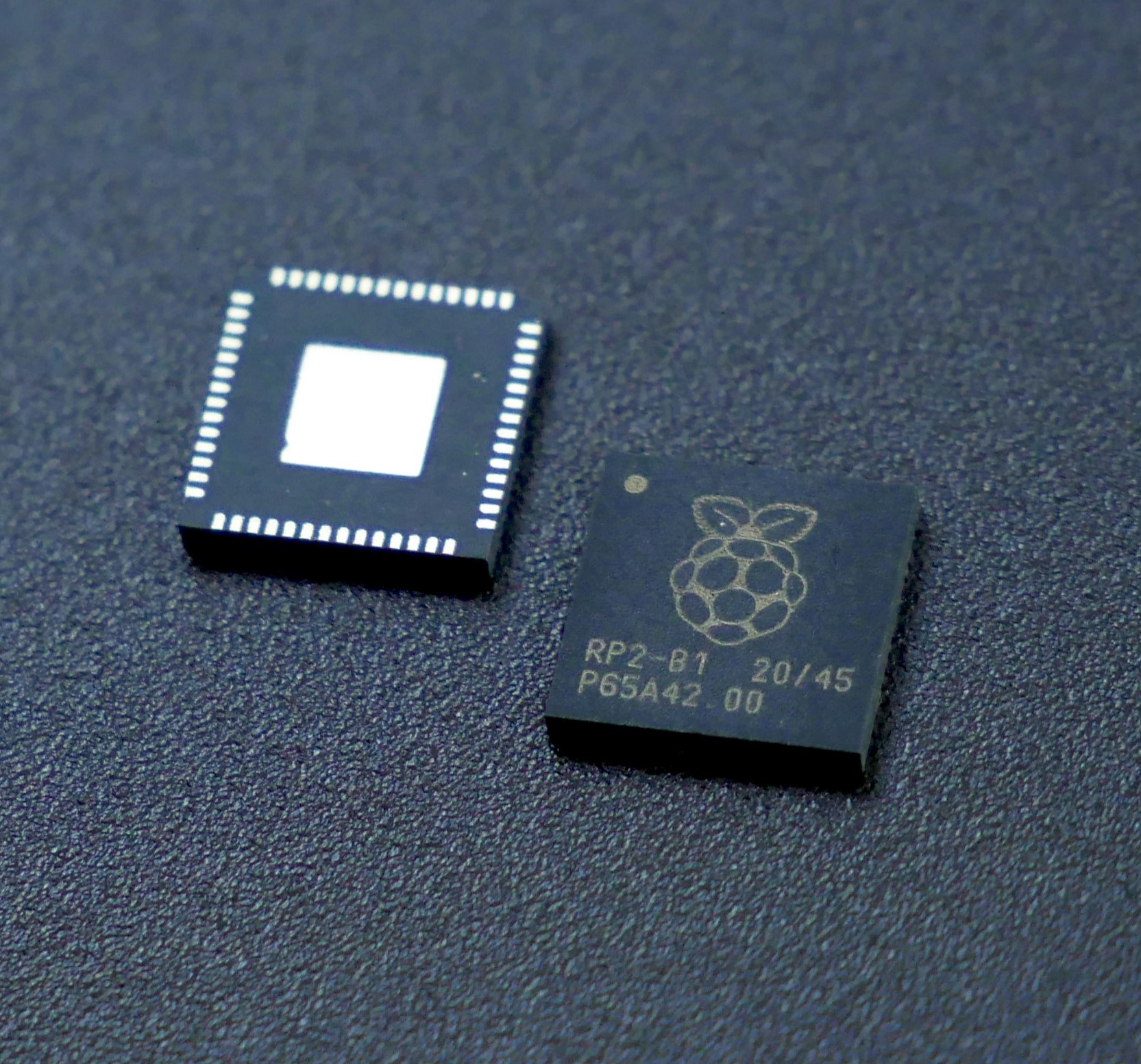

通用 Chiplet Interconnect Express (UCIe) 聯盟宣布發布 UCIe 2.0 規範,進一步推進開放式 Chiplet 生態系統。

最新規範引入了多項關鍵增強功能。首先,它增加了對標準化系統架構的支持,以實現整個系統級封裝 (SiP) 生命週期中跨多個晶片組的可管理性、可測試性和調試 (DFx)。其中包括可選的 UCIe DFx 架構 (UDA),該架構在每個小晶片內整合了供應商無關的管理結構,用於測試、遙測和偵錯功能。

此外,UCIe 2.0 也支援混合鍵結 3D 封裝。新的 UCIe-3D 標準支援小至 1 微米至大 25 微米的凸塊間距,與 2D 和 2.5D 架構相比,可實現更高的頻寬密度和更高的功率效率。

「UCIe 聯盟正在支援各種晶片組,以滿足快速變化的半導體行業的需求,」三星電子總裁兼企業副總裁 Cheolmin Park 說。

UCIe 2.0 規格以先前的迭代為基礎,開發了全面的解決方案堆疊並鼓勵晶片組解決方案之間的互通性。

該規範還包括最佳化的封裝設計,以促進互通性和合規性測試,使供應商能夠根據已知的參考實作來驗證其基於 UCIe 的裝置所支援的功能。

值得注意的是,UCIe 2.0 規範仍然完全向後相容 UCIe 1.1 和 1.0,確保現有基於 Chiplet 的設計的平穩過渡。

以上是UCIe 2.0:透過 3D 封裝和可管理性推進開放式小晶片生態系統的詳細內容。更多資訊請關注PHP中文網其他相關文章!

陳述:

本文內容由網友自願投稿,版權歸原作者所有。本站不承擔相應的法律責任。如發現涉嫌抄襲或侵權的內容,請聯絡admin@php.cn