Rumah >Peranti teknologi >AI >Bolehkah cip superkomputer Tesla mengatasi GPGPU?

Bolehkah cip superkomputer Tesla mengatasi GPGPU?

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBke hadapan

- 2023-04-12 22:43:011662semak imbas

Pengarang: Chen Wei, Ph.D. pakar dalam storan dan pengkomputeran/seni bina GPU dan AI, gelaran profesional kanan. Perikatan Industri Pengkomputeran Awan Zhongguancun, pakar Persatuan Kejuruteraan Optik China, ahli Persekutuan Komputer Antarabangsa (ACM), ahli profesional Persekutuan Komputer China (CCF). Beliau pernah berkhidmat sebagai ketua saintis syarikat AI dan ketua reka bentuk 3D NAND pengeluar cip memori utamanya termasuk seni bina produk storan dan pemproses pengkomputeran berkuasa tinggi domestik yang pertama (telah menyelesaikan ujian dalaman prototaip dalam sebuah. pengilang Internet utama), pemproses AI khusus Domain perubatan pertama (sudah digunakan), pengkompil pecutan AI serasi platform RISC-V/x86/ARM pertama (sudah digunakan dengan kerjasama Alibaba Pingtouge/Xinlai), cip NAND 3D pertama China seni bina dan reka bentuk Pasukan ini telah ditubuhkan (ditanda aras dengan Samsung) dan pengkompil memori kilat terbenam pertama di China (ditanda aras dengan TSMC dan telah digunakan pada peringkat platform).

Pada hari terakhir September 2022, Hari Kecerdasan Buatan Tesla, robot "Optimus Prime" Tesla secara rasminya memulakan kerjayanya. Menurut jurutera Tesla, Hari Kecerdasan Buatan 2022 adalah kali pertama robot Tesla telah "dilepaskan" tanpa sebarang sokongan luaran. “Beliau berjalan dengan bermaruah dan menyapa penonton ke arah umum. Kecuali untuk sedikit kelesuan pergerakan, segala-galanya adalah sangat semula jadi.

1 Adakah kuasa robot Tesla terletak pada "teras dalam"nya?

Tesla menunjukkan video robot "bekerja" di sekitar pejabat. Robot bernama Optimus Prime membawa barang, menyiram tumbuhan, dan juga bekerja secara autonomi di kilang untuk seketika. "Matlamat kami adalah untuk membina robot humanoid yang berguna secepat mungkin, " kata Tesla, sambil menambah bahawa matlamat mereka adalah untuk menjadikan robot kurang daripada $20,000, atau lebih murah daripada kereta elektrik Tesla.

Sebab Tesla Robot begitu berkuasa, sebagai tambahan kepada pengumpulan teknologi AI Tesla sendiri, terutamanya disebabkan oleh cip AI yang dibangunkan sendiri Tesla yang kukuh. Cip AI ini bukan CPU tradisional, apatah lagi GPU Ia adalah bentuk yang lebih sesuai untuk pengiraan AI yang kompleks.

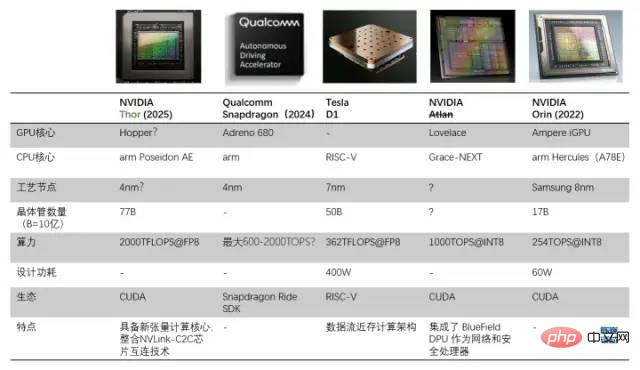

Perbandingan pemproses D1 dan pemproses pemanduan/robotik autonomi lain

1.1 Berdasarkan aliran data seni bina hampir memori untuk mencipta cip AI tujuan umum yang mengatasi GPU

Sebab mengapa Tesla membina cipnya sendiri ialah GPU tidak direka khusus untuk mengendalikan latihan pembelajaran mendalam, yang menjadikan GPU agak tidak cekap dalam tugasan pengkomputeran. Matlamat Tesla dan Dojo (Dojo ialah kedua-dua nama modul latihan dan nama seni bina kernel) adalah untuk "mencapai prestasi latihan AI terbaik. Membolehkan model rangkaian saraf yang lebih besar dan lebih kompleks untuk mencapai kecekapan tenaga yang tinggi dan kos- keberkesanan." Pengkomputeran." Piawaian Tesla adalah untuk membina komputer yang lebih baik dalam pengkomputeran kecerdasan buatan daripada mana-mana komputer lain supaya mereka tidak perlu menggunakan GPU pada masa hadapan.

Titik utama dalam membina superkomputer ialah cara menskalakan kuasa pengkomputeran sambil mengekalkan lebar jalur yang tinggi (sukar) dan kependaman rendah (sangat sukar). Penyelesaian yang diberikan oleh Tesla ialah seni bina 2D (planar) teragih yang terdiri daripada cip berkuasa dan struktur grid yang unik, atau aliran data seni bina pengkomputeran dekat memori.

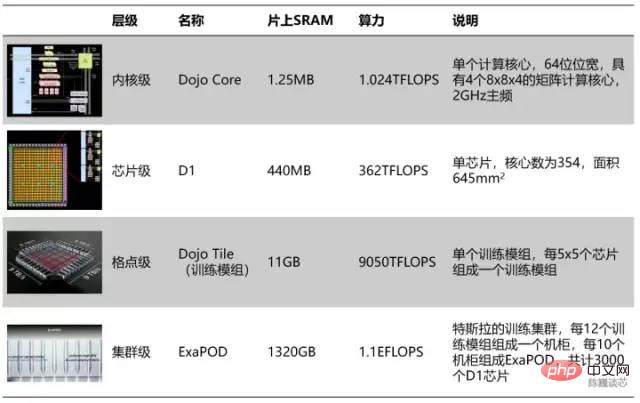

Pembahagian hierarki unit pengkomputeran Tesla

Dari segi hierarki, setiap 354 teras Dojo membentuk cip D1, dan setiap 25 cip membentuk modul latihan. 120 modul latihan terakhir membentuk satu set kluster pengkomputeran ExaPOD, dengan sejumlah 3,000 cip D1.

Modul latihan cip Tesla Dojo boleh mencapai prestasi 6 kumpulan pelayan GPU, tetapi kosnya kurang daripada satu kumpulan pelayan GPU. Kuasa pengkomputeran pelayan Dojo tunggal bahkan mencapai 54PFLOPS. Hanya 4 kabinet Dojo boleh menggantikan 72 rak GPU yang terdiri daripada 4,000 GPU. Dojo mengurangkan kerja pengkomputeran AI (latihan) yang biasanya mengambil masa berbulan-bulan hingga 1 minggu. Jenis "kuasa pengkomputeran besar boleh menghasilkan keajaiban" ini adalah selaras dengan gaya pemanduan autonomi Tesla. Jelas sekali, cip itu juga akan mempercepatkan kemajuan teknologi AI Tesla.

Sudah tentu, modul cip ini masih belum mencapai tahap "sempurna" Walaupun ia menggunakan idea aliran data pengkomputeran hampir memori, kuasa dan tenaga pengkomputerannya nisbah kecekapan tidak melebihi GPU. Pelayan tunggal menggunakan kuasa yang besar, dengan arus mencapai 2000A, dan memerlukan bekalan kuasa yang disesuaikan khas. Cip Tesla D1 sudah pun menjadi had struktur seni bina pengkomputeran memori hampir. Jika Tesla menggunakan seni bina "pengkomputeran dalam memori" atau "logik dalam memori", mungkin prestasi cip atau nisbah kecekapan tenaga akan bertambah baik.

Pelayan cip Tesla Dojo terdiri daripada 12 modul latihan Dojo (2 lapisan, 6 modul setiap lapisan)

1.2 Falsafah reka bentuk seni bina Dojo Tesla

Teras Dojo ialah teras penyahkodan 8-hala dengan daya pemprosesan tinggi dan unit pengiraan matriks 4-hala (8x8) dan 1.25 MB SRAM Tempatan. Walau bagaimanapun, saiz teras Dojo tidak besar Sebagai perbandingan, A64FX Fujitsu menduduki lebih daripada dua kali luas pada nod proses yang sama.

Melalui struktur teras Dojo, kita dapat melihat falsafah reka bentuk Tesla pada pemproses AI umum:

- Pengurangan kawasan: Tesla menyepadukan sejumlah besar teras pengkomputeran ke dalam cip untuk memaksimumkan daya pemprosesan pengkomputeran AI Oleh itu, adalah perlu untuk menjadikan kawasan teras tunggal sekecil mungkin sambil memastikan kuasa pengkomputeran, yang merupakan kompromi yang lebih baik untuk superkomputer. Percanggahan antara susunan kuasa pengkomputeran dan kelewatan dalam sistem.

- Pengurangan cache dan kependaman: Untuk memaksimumkan kecekapan pengkomputeran kawasannya, teras Dojo berjalan pada 2 GHz yang agak konservatif (litar jam konservatif cenderung untuk menduduki kawasan yang kurang), hanya menggunakan asas peramal cawangan dan cache arahan kecil, dalam seni bina yang diperkemas yang hanya mengekalkan komponen yang diperlukan. Kawasan selebihnya dibiarkan sebanyak mungkin kepada pengiraan vektor dan unit pengiraan matriks. Sudah tentu, jika program kernel mempunyai jejak kod yang besar atau mempunyai banyak cawangan, strategi ini mungkin mengorbankan beberapa prestasi.

- Pengurangan ciri: Kurangkan lagi kuasa dan penggunaan kawasan dengan memotong ciri pemproses yang tidak diperlukan untuk menjalankan pengiraan dalaman. Teras Dojo tidak melakukan caching sisi data, tidak menyokong memori maya dan tidak menyokong pengecualian yang tepat.

Bagi Tesla dan Musk, Dojo bukan sahaja berbentuk dan disusun seperti dojo, tetapi falsafah reka bentuknya juga berkait rapat dengan semangat dojo, menjelma sepenuhnya " less is more" estetika reka bentuk pemproses "Berbilang".

2 Adakah teras D1 seni bina RISC-V?

Mari kita lihat dahulu struktur dan ciri setiap Dojo.

Setiap teras Dojo ialah pemproses dengan keupayaan pengiraan vektor/matriks, dengan komponen pengambilan arahan, penyahkodan dan pelaksanaan yang lengkap. Teras Dojo mempunyai gaya seperti CPU yang nampaknya lebih mudah disesuaikan dengan algoritma dan kod percabangan yang berbeza daripada GPU. Set arahan D1 adalah serupa dengan RISC-V Pemproses berjalan pada 2GHz dan mempunyai empat set unit pengiraan matriks 8x8. Ia juga mempunyai satu set arahan vektor tersuai yang memfokuskan pada mempercepatkan pengiraan AI.

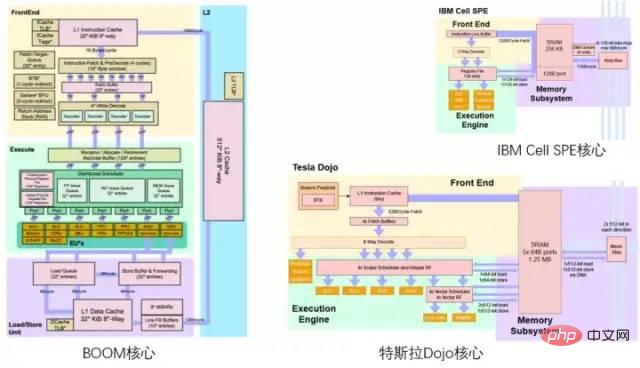

Mereka yang biasa dengan medan RISC-V mungkin boleh memberitahu bahawa skema warna gambarajah seni bina Dojo Tesla nampaknya memberi penghormatan kepada gambarajah seni bina pemproses BOOM Berkeley, dengan kuning di atasnya, hijau di bahagian bawah ungu.

Perbandingan antara teras Tesla Dojo dan teras Berkeley BOOM/IBM Cell

2.1 D1 seni bina keseluruhan teras

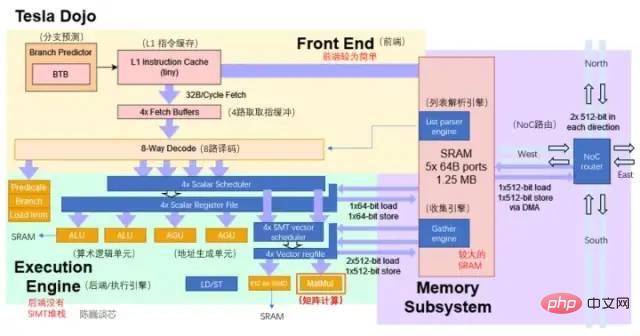

struktur teras D1 (bahagian biru ialah butiran yang ditambah/diubah suai)

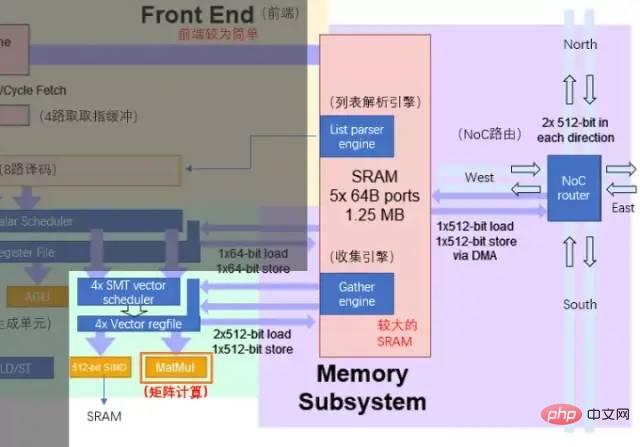

Berdasarkan gambar rajah seni bina semasa, teras Dojo terdiri daripada 4 bahagian: bahagian hadapan, unit pelaksanaan, penghalaan SRAM dan NoC Ia mempunyai komponen kawalan yang lebih sedikit daripada kedua-dua CPU dan GPU idea serupa dengan tensor GPU Unit pengkomputeran matriks teras (Tensor teras).

Struktur teras Dojo lebih diperkemas daripada BOOM Ia tidak mempunyai komponen seperti Namakan semula untuk meningkatkan penggunaan komponen pelaksanaan, dan ia juga sukar untuk menyokong memori maya. Walau bagaimanapun, kelebihan reka bentuk ini ialah ia mengurangkan kawasan yang diduduki oleh bahagian kawalan dan boleh memperuntukkan lebih banyak kawasan pada cip kepada unit pelaksanaan pengiraan. Setiap teras Dojo menyediakan 1.024TFLOPS kuasa pengkomputeran. Dapat dilihat bahawa hampir semua kuasa pengkomputeran setiap unit disediakan oleh unit pengkomputeran matriks. Oleh itu, unit pengkomputeran matriks dan SRAM bersama-sama menentukan nisbah kecekapan tenaga pengkomputeran pemproses D1.

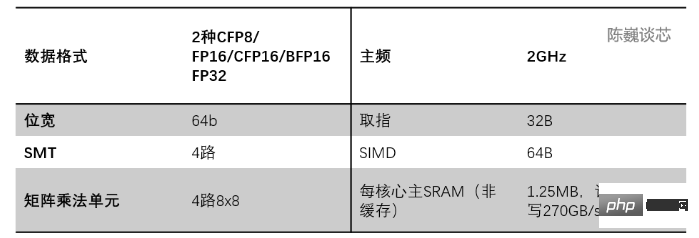

Parameter utama teras Dojo

- Ramalan cawangan: Berbanding dengan seni bina SIMT seperti GPU, teras Dojo tidak mempunyai teras tindanan SIMT untuk memperuntukkan tugas cawangan berbilang benang. Tetapi teras Dojo mempunyai BTB (penampan sasaran cawangan), jadi D1 boleh meningkatkan prestasi melalui ramalan cawangan mudah.

BTB menyimpan alamat arahan cawangan yang berjaya dan alamat sasaran cawangannya dalam penimbal dikenal pasti melalui alamat arahan cawangan. Penalti prestasi cawangan dalam pemproses saluran paip boleh dikurangkan dengan meramalkan laluan cawangan dan menyimpan cache maklumat yang digunakan oleh cawangan. - Cache arahan: Cache arahan L1 yang lebih kecil disambungkan terus ke SRAM dalam teras untuk mendapatkan arahan pengkomputeran.

- Pengambilan arahan: Setiap kernel Dojo mempunyai tetingkap pengambilan arahan 32B, yang boleh memuatkan sehingga 8 arahan.

- Penyahkod: Penyahkod 8 hala boleh mengendalikan dua utas setiap kitaran. Fasa penyahkodan memperoleh arahan daripada penimbal pengambilan dan menyahkodnya, dan memperuntukkan sumber pelaksanaan yang diperlukan mengikut keperluan setiap arahan.

- Penjadualan benang: Selepas penyahkodan 8 hala yang lebih luas, terdapat penjadual vektor (Penjadual) dan fail daftar (Fail Daftar). Nampaknya tiada pertimbangan topeng untuk pengagregatan cawangan di sini, dan kecekapan pelaksanaan cawangan sebenar mungkin lebih rendah sedikit daripada GPU. Semoga Tesla mempunyai penyusun yang berkuasa.

- Unit pelaksanaan: dengan ALU 2 hala dan AGU 2 hala, serta SIMD 512-bit dan unit pengiraan matriks untuk pengiraan vektor/matriks (melaksanakan pengiraan vektor 512-bit dan Matriks 4-hala 8x8 masing-masing pendaraban). Unit pengkomputeran matriks ialah kuasa pengkomputeran utama cip D1. (Diperkenalkan secara terperinci dalam bahagian seterusnya)

- ALU dan AGU bertanggungjawab terutamanya untuk sejumlah kecil pengiraan logik selain daripada pengiraan matriks. AGU ialah unit penjanaan alamat, yang digunakan terutamanya untuk menjana alamat yang diperlukan untuk mengendalikan SRAM dan mengakses alamat teras lain. Dengan menjalankan pengiraan alamat selari dengan seluruh CPU.

Apabila melakukan pelbagai operasi, CPU biasa perlu mengira alamat memori yang diperlukan untuk mengambil data daripada memori (atau SRAM). Sebagai contoh, lokasi memori elemen tatasusunan mesti dikira sebelum teras CPU boleh mendapatkan data daripada lokasi memori sebenar. Pengiraan penjanaan alamat ini melibatkan operasi aritmetik integer yang berbeza seperti penambahan, penolakan, aritmetik modulo atau peralihan bit. Mengira alamat memori boleh menyusun berbilang arahan mesin am, atau ia boleh dilaksanakan terus melalui litar perkakasan AGU seperti Tesla Dojo. Dengan cara ini, pelbagai pengiraan penjanaan alamat boleh dimuat turun daripada ALU, mengurangkan bilangan kitaran CPU yang diperlukan untuk melaksanakan pengiraan AI, dengan itu meningkatkan prestasi pengkomputeran. - SIMD bertanggungjawab terutamanya untuk pengiraan fungsi khas seperti pengaktifan dan pengumpulan data.

- Unit pengiraan matriks ialah komponen kuasa pengkomputeran utama Dojo Ia bertanggungjawab untuk pengiraan matriks dua dimensi dan kemudian melaksanakan pengiraan konvolusi, Transformer dan lain-lain.

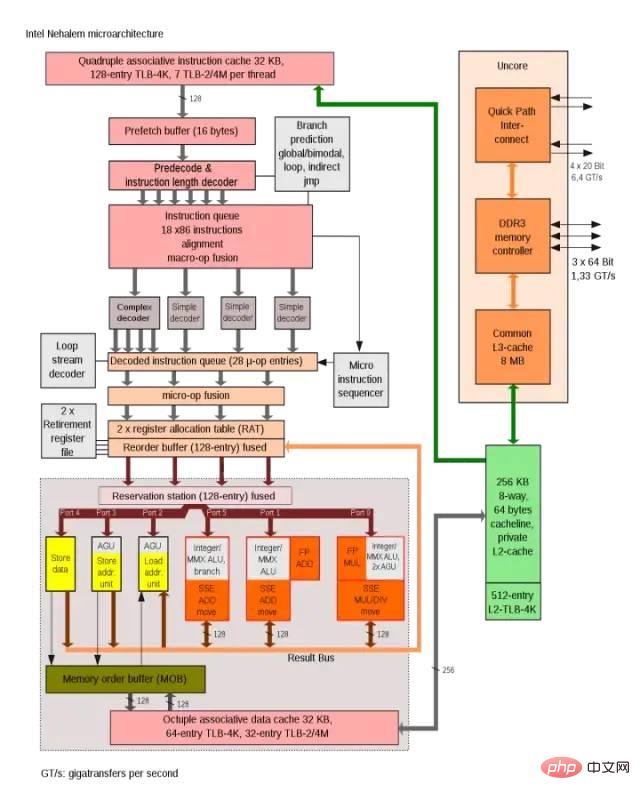

Seni bina Intel Nehalem menggunakan AGU untuk meningkatkan kecekapan akses alamat kitaran tunggal

Kaedah sambungan kernel Dojo lebih serupa dengan kaedah sambungan kernel SPE dalam pemproses Sel IBM. Persamaan utama termasuk:

- Kod yang dijalankan pada D1 atau SPE tidak mempunyai akses terus kepada memori sistem, aplikasi ini berfungsi terutamanya dalam SRAM tempatan

- Jika data daripada memori utama (DDR atau HBM) diperlukan, operasi DMA mesti digunakan untuk membacanya dalam

- SPE D1 mahupun Cell tidak menyokong memori maya.

Berikut akan memperkenalkan storan pengiraan dan modul darab matriks dan kernel.

2.2 Pengkomputeran unit pengkomputeran matriks teras dan storan pada cip

Teras peningkatan kuasa pengkomputeran seni bina Dojo ialah unit pengkomputeran matriks. Interaksi data antara unit pengkomputeran matriks dan teras SRAM membentuk penggunaan kuasa pengendalian data teras utama.

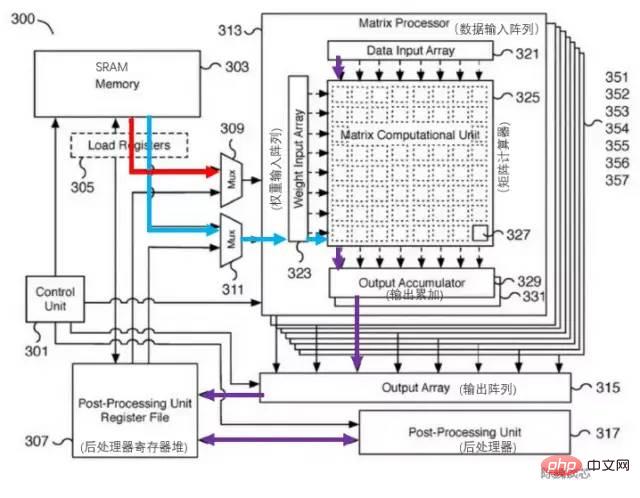

Paten sepadan unit pengkomputeran matriks Tesla adalah seperti yang ditunjukkan di bawah. Komponen utama modul ini ialah unit pendaraban matriks-matriks 8x8 (dipanggil kalkulator matriks dalam rajah). Input ialah tatasusunan input data dan tatasusunan input berat Selepas mengira pendaraban matriks, output dikumpul secara langsung. Setiap teras Dojo termasuk unit pendaraban matriks 8x8 4 hala.

Paten Unit Pengkomputeran Tesla Matrix

Memandangkan hanya terdapat satu cache L1 dan SRAM pada rajah seni bina, adalah berani membuat spekulasi bahawa Tesla telah memperkemas struktur cache RISC-V untuk menjimatkan kawasan cache dan mengurangkan kependaman. Blok SRAM 1.25MB setiap teras boleh menyediakan bacaan 2x512-bit (bersesuaian dengan berat dan data pengiraan AI) dan lebar jalur tulis 512-bit untuk unit pengkomputeran SIMD dan matriks, serta keupayaan baca dan tulis 64-bit untuk integer fail daftar. Aliran data utama pengiraan adalah dari SRAM ke SIMD dan unit pendaraban matriks.

Aliran pemprosesan utama unit pengiraan matriks ialah:

Muatkan pemberat dari SRAM ke tatasusunan input berat melalui pemultipleks (Mux) (Susun atur input berat), dan pada masa yang sama memuatkan data dalam SRAM ke tatasusunan input data (tatasusunan input data).

Data input dan pemberat didarab dalam kalkulator matriks (unit pengiraan matriks) (hasil dalam atau hasil luar?)

Pendaraban keputusan pengiraan adalah output kepada penumpuk keluaran (Output accumulator) untuk pengumpulan. Apabila mengira di sini, pengiraan matriks melebihi 8x8 boleh dilakukan dengan pembahagian matriks dan penyambungan.

Output terkumpul dihantar ke dalam fail daftar pasca pemproses untuk caching, dan kemudian pasca pemprosesan (operasi seperti pengaktifan, pengumpulan, padding, dll. boleh dilakukan).

Keseluruhan proses pengiraan dikawal secara langsung oleh unit kawalan (Control unit) tanpa campur tangan CPU.

Interaksi data antara unit pelaksanaan dan SRAM/NoC

Teras Dojo SRAM di dalam mempunyai lebar jalur baca dan tulis yang sangat besar dan boleh memuatkan pada 400 GB/saat dan menulis pada 270 GB/saat. Set arahan teras Dojo mempunyai arahan pemindahan rangkaian khusus, dihalakan melalui NoC, yang boleh memindahkan data terus ke dalam atau keluar dari memori SRAM teras lain dalam cip D1 atau bahkan dalam modul latihan Dojo.

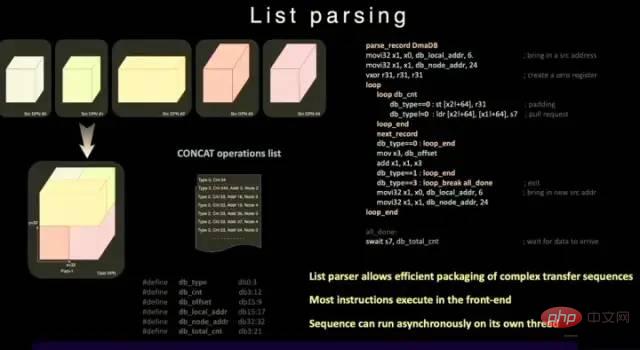

Berbeza daripada SRAM biasa, SRAM Dojo termasuk enjin parser senarai dan enjin kumpul. Fungsi penghuraian senarai adalah salah satu ciri utama cip D1 Enjin penghuraian senarai boleh membungkus urutan penghantaran kompleks jenis data yang berbeza untuk meningkatkan kecekapan penghantaran.

Fungsi penghuraian senarai

Untuk mengurangkan lagi kelewatan operasi, kawasan dan Kerumitan, D1 tidak menyokong memori maya. Dalam pemproses biasa, alamat memori yang digunakan oleh atur cara tidak terus mengakses alamat memori fizikal, tetapi ditukar kepada alamat fizikal oleh CPU menggunakan struktur paging yang ditetapkan oleh sistem pengendalian.

Dalam teras D1, fungsi SMT 4 hala membenarkan keselarian yang jelas dalam pengiraan, memudahkan AGU dan menangani kaedah pengiraan untuk membolehkan Tesla mengakses SRAM dengan kependaman yang cukup rendah bahawa ia mengelakkan kelewatan cache data L1 perantaraan.

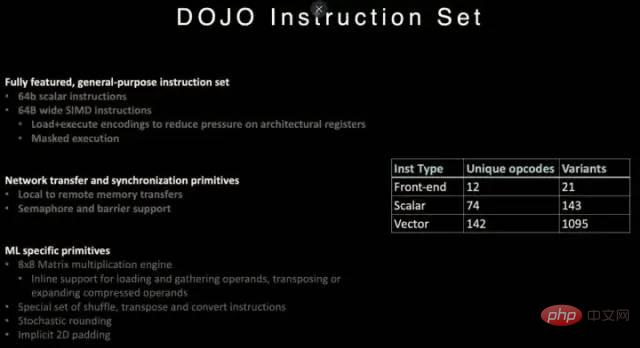

Set Arahan 2.3 Dojo

Set Arahan Pemproses D1

Rujukan D1 RISC -Arahan seni bina V diperkenalkan, dan beberapa arahan disesuaikan, terutamanya yang berkaitan dengan pengiraan vektor.

Set arahan D1 menyokong arahan skalar 64-bit dan arahan SIMD 64-bait, dan rangkaian menghantar primitif khusus yang berkaitan dengan primitif penyegerakan dan pembelajaran mesin/pembelajaran mendalam (seperti matriks 8x8 pengiraan).

Dari segi penghantaran data rangkaian dan primitif penyegerakan, ia menyokong primitif arahan (Primitives) untuk menghantar data dari storan tempatan (SRAM) ke storan jauh, serta semaphore (Semaphore) dan halangan. Ini membolehkan D1 menyokong multi-threading, dan arahan operasi memorinya boleh dijalankan pada berbilang teras D1.

Untuk pembelajaran mesin dan pembelajaran mendalam, Tesla mentakrifkan arahan termasuk operasi matematik seperti shuffle, transpose dan tukar, serta arahan yang berkaitan dengan pembundaran stokastik dan padding.

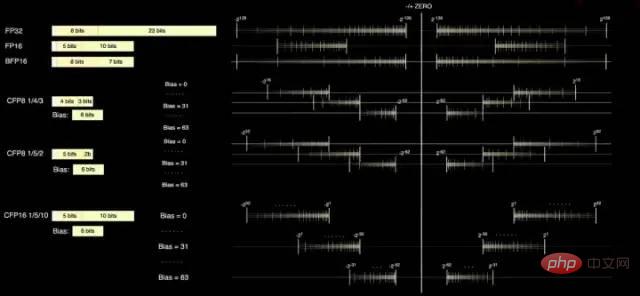

2.4 Format data

Teras D1 mempunyai dua format pengiraan standard, FP32 dan FP16, dan juga mempunyai format BFP16 yang lebih sesuai untuk Inferens. Untuk mencapai peningkatan prestasi pengkomputeran ketepatan campuran, D1 juga menggunakan format CFP8 8-bit untuk ketepatan yang lebih rendah dan daya pemprosesan yang lebih tinggi.

Kelebihan menggunakan CFP8 ialah ia dapat menjimatkan lebih banyak ruang pengganda untuk mencapai kuasa pengkomputeran yang hampir sama, yang sangat membantu untuk meningkatkan ketumpatan kuasa pengkomputeran D1.

Pengkompil Dojo boleh meluncur di sekeliling ketepatan mantissa untuk merangkumi julat dan ketepatan yang lebih luas. Sehingga 16 format vektor berbeza boleh digunakan pada bila-bila masa, memberikan anda fleksibiliti untuk meningkatkan kuasa pengkomputeran.

Format data pemproses D1

Menurut Tesla Maklumat boleh dikira menggunakan CFP8 di dalam unit pendaraban matriks (disimpan dalam format CFP16).

3 Bolehkah pemproses seni bina Dojo mengatasi GPU?

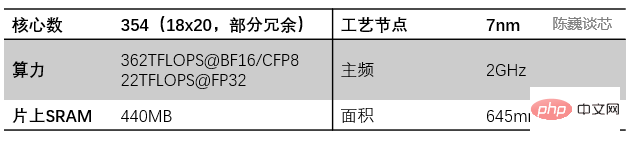

Pemproses D1 dihasilkan oleh TSMC dan menggunakan proses pembuatan 7-nanometer Ia mempunyai 50 bilion transistor dan luas cip 645mm², yang lebih kecil daripada NVIDIA A100 (826 mm²) dan. AMD Arcturus (750 mm²).

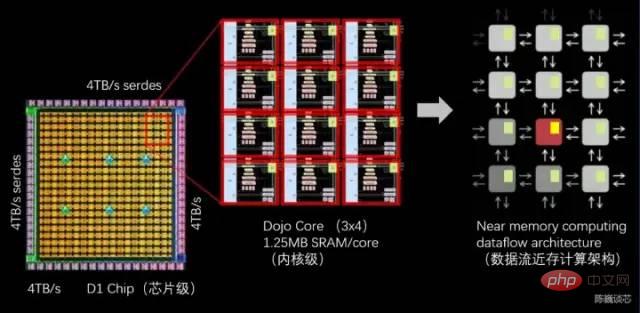

3.1 Aliran data Dojo seni bina pengkomputeran dekat memori

Struktur pemproses D1

Setiap pemproses D1 terdiri daripada sambungan teras Dojo 18 x 20. Terdapat 354 teras Dojo tersedia dalam setiap pemproses D1. (Sebab mengapa hanya 354 daripada 360 teras digunakan adalah untuk pertimbangan kestabilan teras hasil dan setiap pemproses) Ia dihasilkan oleh TSMC, menggunakan proses pembuatan 7nm, dengan 50 bilion transistor dan kawasan cip 645mm².

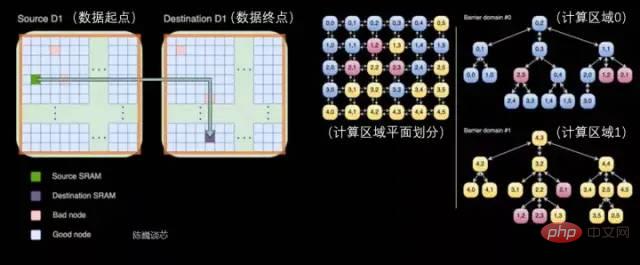

Setiap teras Dojo mempunyai 1.25MB SRAM sebagai berat utama dan storan data. Teras Dojo yang berbeza disambungkan melalui penghalaan rangkaian pada cip (penghalaan NoC), dan teras Dojo yang berbeza melakukan penyegerakan data melalui rangkaian NoC yang kompleks dan bukannya berkongsi cache data. NoC boleh mengendalikan 8 paket dalam 4 arah (tenggara, barat laut) merentasi sempadan nod pada 64 B/setiap kitaran jam dalam setiap arah, iaitu satu paket masuk dan satu paket keluar ke dalam mesh dalam keempat-empat arah Setiap teras Dojo bersebelahan. Penghala NoC juga boleh melakukan bacaan dan tulis dwiarah 64B ke SRAM dalam teras sekali setiap kitaran.

Pemindahan silang pemproses dan pembahagian tugas dalam pemproses D1

Setiap teras Dojo adalah seperti CPU yang agak lengkap dengan keupayaan pengkomputeran matriks (kerana setiap teras mempunyai unit pengkomputeran matriks yang berasingan dan bahagian hadapannya agak kecil, ia dipanggil seperti CPU di sini seni bina aliran datanya agak serupa Disebabkan kepada struktur grid aliran data dua dimensi SambaNova, data mengalir terus antara setiap teras pemprosesan tanpa kembali ke ingatan.

Cip D1 berjalan pada 2GHz dan mempunyai 440MB SRAM yang besar. Tesla memfokuskan reka bentuknya pada SRAM yang diedarkan dalam grid pengkomputeran, mengurangkan kekerapan akses kepada memori melalui sejumlah besar storan pada cip yang lebih pantas dan lebih dekat dan pemindahan antara storan pada cip, dengan itu meningkatkan prestasi keseluruhan sistem, yang mempunyai ciri-ciri jelas penyimpanan aliran data dan pengkomputeran seni bina bersepadu (pengkomputeran hampir memori aliran data).

Setiap cip D1 mempunyai 576 saluran SerDes dwiarah yang diedarkan di sekelilingnya untuk menyambung kepada cip D1 lain dengan lebar jalur satu sisi 4 TB/saat.

Parameter utama cip pemproses D1

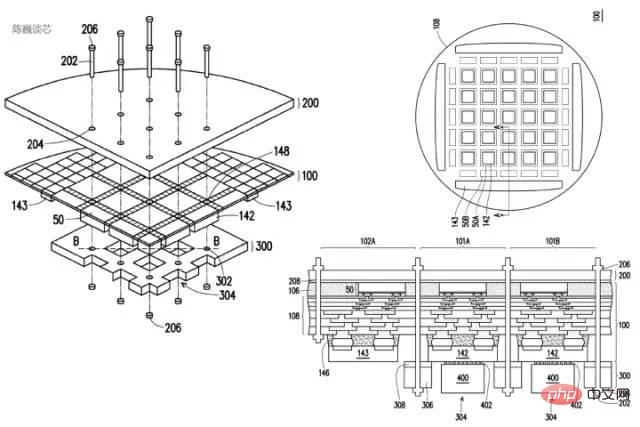

3.2 Dojo Chiplet teknologi sambung pembungkusan modul latihan

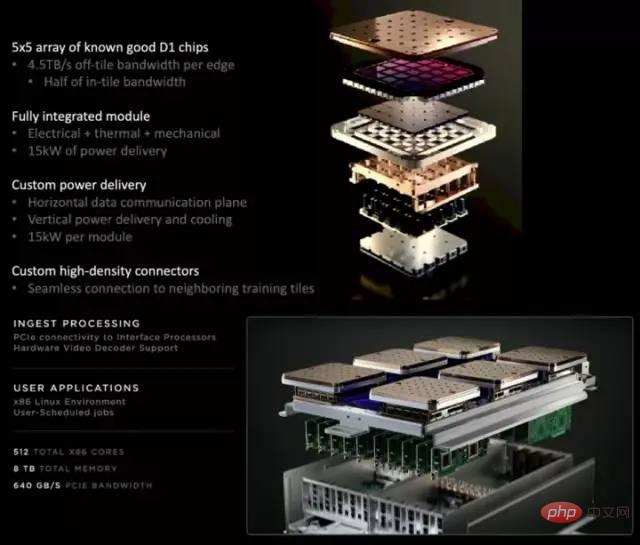

Setiap modul latihan D1 disusun dalam susunan cip D1 5x5 dan disambungkan dalam struktur Mesh dua dimensi. SRAM teras silang pada cip mencapai 11GB yang menakjubkan, dan sudah tentu penggunaan kuasa juga mencapai 15kW yang menakjubkan. Nisbah kecekapan tenaga ialah 0.6TFLOPS/W@BF16/CFP8. (Saya harap saya salah mengira, jika tidak nisbah kecekapan tenaga ini memang tidak ideal). Memori HBM kongsi 32GB luaran. (HBM2e atau HBM3)

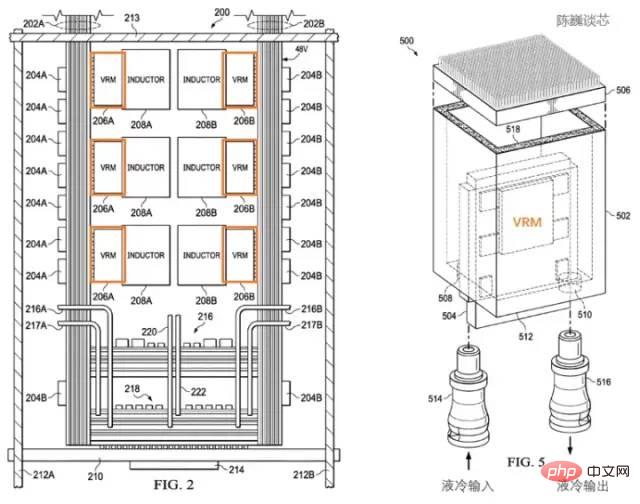

Struktur pelesapan haba yang dipatenkan bagi pemproses Tesla D1

Tesla menggunakan modul peraturan Kuasa khusus (VRM ) dan struktur terma untuk menguruskan penggunaan kuasa. Terdapat dua tujuan utama pengurusan kuasa di sini:

Untuk mengurangkan kehilangan kuasa yang tidak perlu dan meningkatkan nisbah kecekapan tenaga.

Kurangkan kegagalan modul pemproses yang disebabkan oleh ubah bentuk terma.

Menurut paten Tesla, kita dapat melihat bahawa modul pengawalan kuasa berserenjang dengan cip itu sendiri, yang sangat mengurangkan kawasan yang diduduki oleh satah pemproses dan boleh disejukkan melalui penyejukan cecair. Mengimbangi suhu pemproses dengan cepat.

Penyelesapan haba berpaten dan struktur pembungkusan pemproses Tesla D1

The modul latihan menggunakan pembungkusan InFO_SoW (Silicon on Wafer) untuk meningkatkan ketumpatan interkoneksi antara cip. Sebagai tambahan kepada teknologi INFO_SoW TSMC, pakej ini juga menggunakan struktur pembungkusan mekanikal Tesla sendiri untuk mengurangkan kegagalan modul pemproses.

40 cip I/O di pinggir luar setiap modul latihan mencapai lebar jalur agregat 36 TB/s, atau lebar jalur rentang 10 TB/s. Setiap lapisan modul latihan disambungkan kepada sistem storan ultra-pantas: 640GB memori berjalan boleh menyediakan lebih daripada 18TB/s lebar jalur, ditambah lebih daripada 1TB/s lebar jalur pensuisan rangkaian.

Arah penghantaran data adalah selari dengan satah cip, dan arah bekalan kuasa serta penyejukan cecair berserenjang dengan satah cip. Ini adalah reka bentuk struktur yang sangat cantik, dan modul latihan yang berbeza boleh disambungkan. Melalui struktur tiga dimensi, kawasan bekalan kuasa modul cip disimpan dan jarak antara cip pengkomputeran dikurangkan sebanyak mungkin.

Kabinet Dojo POD terdiri daripada dua lapisan dulang pengiraan dan sistem storan. Setiap tahap palet mempunyai 6 modul latihan D1. Kabinet yang terdiri daripada 12 modul latihan di dua tingkat boleh memberikan 108PFLOPS kuasa pengkomputeran pembelajaran mendalam.

Modul Dojo dan kabinet POD Dojo

3.3 Pengurusan kuasa dan kawalan pelesapan haba

Penyelesapan haba platform pengkomputeran super sentiasa menjadi dimensi penting untuk mengukur tahap sistem pengkomputeran super.

Kuasa reka bentuk terma cip D1

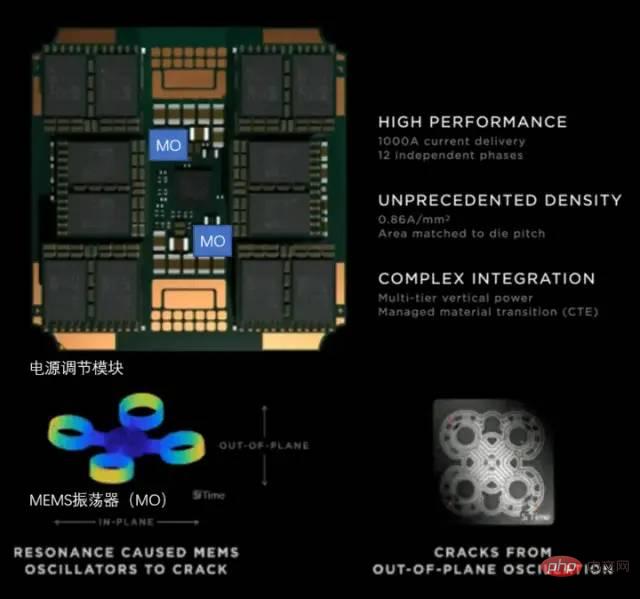

Tesla menggunakan VRM (Modul Peraturan Voltan) yang dibangunkan sendiri sepenuhnya pada POD Dojo , satu VRM boleh memberikan voltan 52V dan arus besar lebih daripada 1000A pada litar kurang daripada luas syiling 25 sen Sasaran semasa ialah 0.86A setiap milimeter persegi, dengan jumlah 12 fasa bekalan kuasa bebas.

Modul penyaman kuasa Tesla

Untuk ketumpatan tinggi Dari segi cip pelesapan haba, tumpuan adalah untuk mengawal pekali pengembangan haba (CTE). Ketumpatan cip sistem Dojo sangat tinggi Jika CTE berada di luar kawalan, ia boleh menyebabkan ubah bentuk/kegagalan struktur, mengakibatkan kegagalan sambungan.

VRM yang dibangunkan sendiri oleh Tesla telah mengulangi 14 versi dalam tempoh 2 tahun yang lalu, menggunakan pengayun MEMS (MO) untuk merasakan ubah bentuk terma modul pengawalan kuasa, dan akhirnya memenuhi sepenuhnya keperluan dalaman untuk penunjuk CTE. Kaedah melaraskan bekalan kuasa secara aktif melalui teknologi MEMS adalah serupa dengan kaedah pelarasan aktif mengawal getaran badan roket.

3.4 Ekosistem Kompilasi Pemproses Seni Bina Dojo

Timbunan Perisian Pemproses D1

Untuk cip AI seperti D1, ekologi kompilasi tidak kurang pentingnya daripada cip itu sendiri.

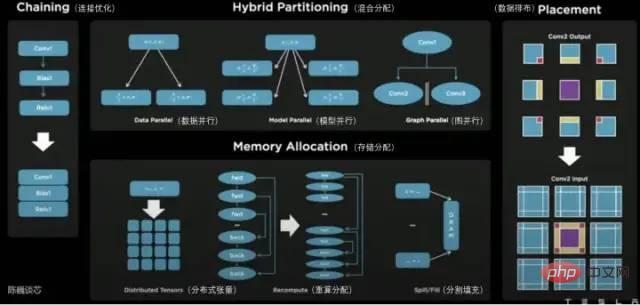

Pada satah pemproses D1, D1 dibahagikan kepada unit pengkomputeran matriks. Rantaian alat penyusunan bertanggungjawab untuk membahagikan tugas dan mengkonfigurasi storan data, dan melaksanakan pengkomputeran selari yang terperinci dalam pelbagai cara dan mengurangkan penggunaan storan.

Kaedah selari yang disokong oleh pengkompil Dojo termasuk keselarian data, keselarian model dan keselarian graf. Kaedah peruntukan storan yang disokong termasuk tensor teragih, peruntukan dikira semula dan isian berpecah.

Pengkompil itu sendiri boleh mengendalikan aliran kawalan dinamik yang biasa digunakan dalam pelbagai CPU, termasuk algoritma pengoptimuman gelung dan graf. Dengan pengkompil Dojo, pengguna boleh menganggap sistem teragih berskala besar Dojo sebagai pemecut untuk reka bentuk dan latihan keseluruhan.

Lapisan atas keseluruhan ekosistem perisian adalah berdasarkan PyTorch, lapisan bawah adalah berdasarkan pemacu Dojo, dan pengkompil Dojo dan LLVM digunakan di tengah untuk membentuk lapisan kompilasi . Selepas menambah LLVM di sini, Tesla boleh menggunakan lebih baik pelbagai ekosistem kompilasi yang sudah ada pada LLVM untuk pengoptimuman kompilasi.

Tesla Dojo Compiler

4 Kesimpulan

Melalui Hari AI Tesla, kami melihat bentuk sebenar robot Tesla dan mempelajari lebih lanjut tentang "teras dalam" yang berkuasa.

Teras Dojo Tesla berbeza daripada seni bina CPU dan GPU sebelumnya Ia boleh dikatakan sebagai GPU yang diperkemas yang menggabungkan ciri-ciri CPU. Saya percaya ia juga akan disusun dengan CPU. Terdapat perbezaan besar dengan GPU. Untuk meningkatkan ketumpatan pengkomputeran, Tesla telah membuat pengoptimuman yang sangat diperkemas dan menyediakan mekanisme pengurusan kuasa yang diselaraskan secara aktif.

Seni bina Tesla Dojo bukan sahaja dipanggil dojo, tetapi reka bentuknya sememangnya berdasarkan kesederhanaan dan kurang. Adakah seni bina ini akan menjadi satu lagi bentuk seni bina cip pengkomputeran yang tipikal selepas CPU dan GPU? Sama-sama kita tunggu dan lihat.

Atas ialah kandungan terperinci Bolehkah cip superkomputer Tesla mengatasi GPGPU?. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Artikel berkaitan

Lihat lagi- Aliran teknologi untuk ditonton pada tahun 2023

- Cara Kecerdasan Buatan Membawa Kerja Baharu Setiap Hari kepada Pasukan Pusat Data

- Bolehkah kecerdasan buatan atau automasi menyelesaikan masalah kecekapan tenaga yang rendah dalam bangunan?

- Pengasas bersama OpenAI ditemu bual oleh Huang Renxun: Keupayaan penaakulan GPT-4 belum mencapai jangkaan

- Bing Microsoft mengatasi Google dalam trafik carian terima kasih kepada teknologi OpenAI