ホームページ >テクノロジー周辺機器 >AI >Tesla Dojo スーパーコンピューティング アーキテクチャの詳細が初公開!自動運転は「ばらばら」

Tesla Dojo スーパーコンピューティング アーキテクチャの詳細が初公開!自動運転は「ばらばら」

- PHPz転載

- 2023-04-11 21:46:251340ブラウズ

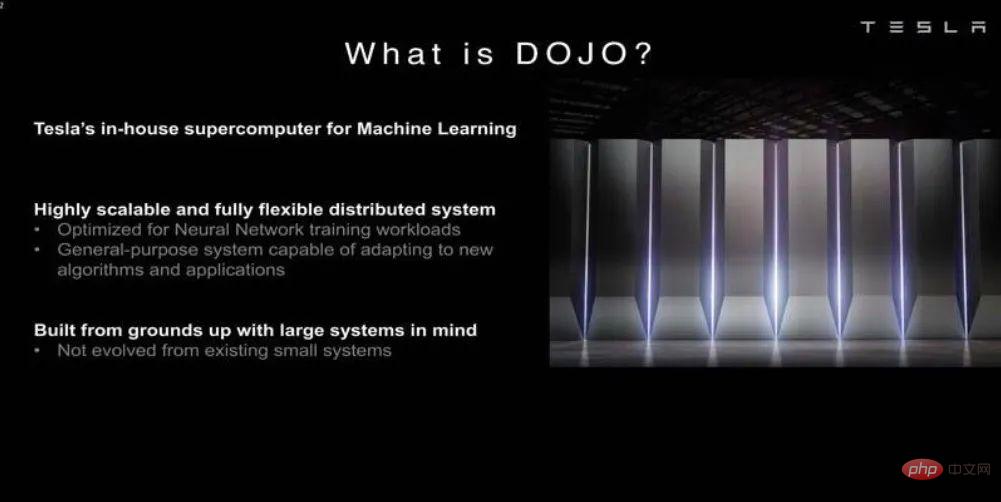

人工知能と機械学習モデルに対する需要の高まりに応えるため、テスラはテスラ車に自動運転を教えるための独自の人工知能テクノロジーを開発しました。

最近、テスラは Hot Chips 34 カンファレンスで、Dojo スーパーコンピューティング アーキテクチャに関する多くの詳細を明らかにしました。

本質的に、Dojo は、計算、ネットワーキング、入出力 (I/O) チップから命令セット アーキテクチャまでをカバーする完全なカスタム アーキテクチャから構築された巨大なコンポーザブル スーパーコンピュータです。 (ISA)、電力供給、パッケージング、冷却。これらはすべて、カスタムの特定の機械学習トレーニング アルゴリズムを大規模に実行するために行われます。

Ganesh Venkataramanan は、Tesla の自動運転ハードウェア担当シニア ディレクターであり、Dojo プロジェクトと AMD の CPU 設計チームの責任者です。 Hot Chips 34 カンファレンスで、彼とチップ、システム、ソフトウェア エンジニアのグループは、マシンのアーキテクチャ上の機能の多くを初めて発表しました。

データセンター「サンドイッチ」

一般的に言えば、チップを製造するプロセスは、チップをパッケージ上に配置し、そのパッケージをプリント基板上に配置することです。それからシステムに入り、システムはラックに入ります」とヴェンカタラマナン氏は語った。

しかし、このプロセスには問題があります。データがチップからパッケージに移動し、パッケージの外に移動するたびに、遅延と帯域幅の損失が発生します。

これらの制限を回避するために、Venkataramanan と彼のチームはゼロから始めることにしました。

こうして、Dojo のトレーニング タイルが誕生しました。

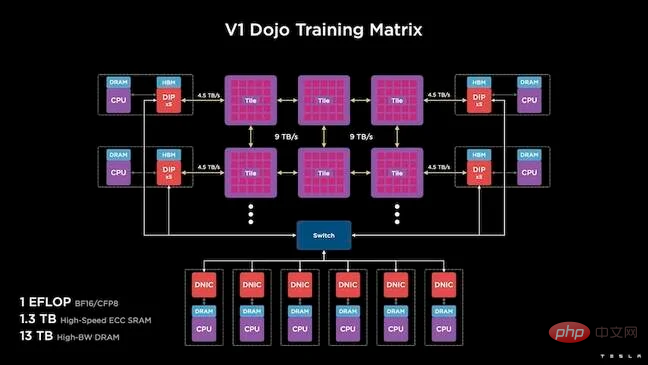

これは、半分立方フィートを占有し、15kW の水冷パッケージで 556TFLOPS の FP32 パフォーマンスが可能な自己完結型コンピューティング クラスターです。

各タイルには 11 GB の SRAM が搭載されており、スタック全体でカスタム トランスポート プロトコルを使用して 9 TB/秒のファブリック経由で接続されています。

Venkataramanan 氏は次のように述べています。「このトレーニング ボードは、追加のスイッチを必要とせずに、コンピュータからメモリ、電力供給、通信に至るまで、比類のないレベルの統合を実現しています。」

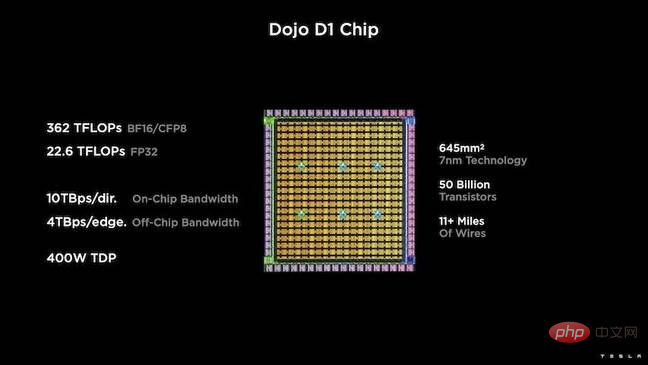

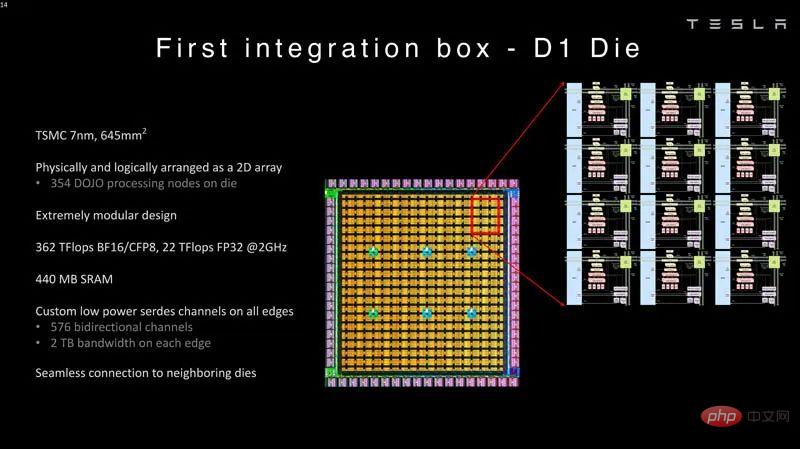

トレーニング タイルのコアは、TSMC の 7nm プロセスに基づく 500 億個のトランジスタ チップである Tesla の D1 です。テスラによれば、各 D1 は 400W の TDP で 22TFLOPS の FP32 パフォーマンスを達成できるという。

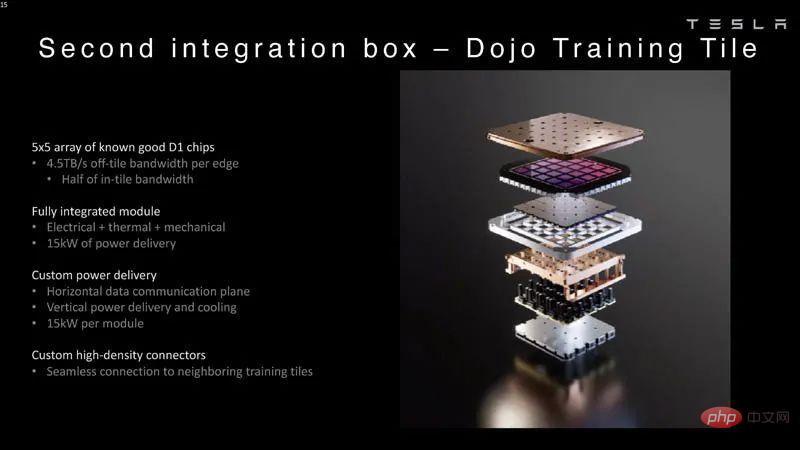

テスラは 25 個の D1 を使用し、既知の良好な金型に分割し、TSMC のオンウェーハ システム テクノロジを使用してそれらをまとめて大規模なコンピューティングを可能にしました。非常に低い遅延と非常に高い帯域幅を備えた統合。

ただし、チップ上のシステム設計と垂直スタック アーキテクチャにより、電力供給に課題が生じます。

Venkataramanan 氏によると、現在の加速器のほとんどは電源をシリコン ウェーハのすぐ隣に配置しています。同氏は、このアプローチは効果的ではあるものの、アクセラレータの大部分をこれらのコンポーネント専用に費やす必要があることを意味し、これは Dojo にとって現実的ではないと説明しました。したがって、テスラはチップの底部から直接電力を供給することを選択しました。

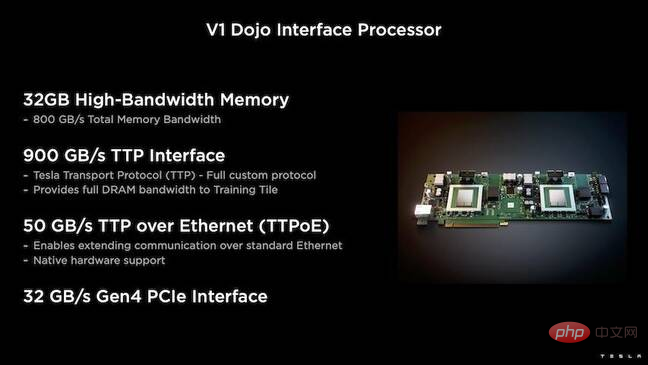

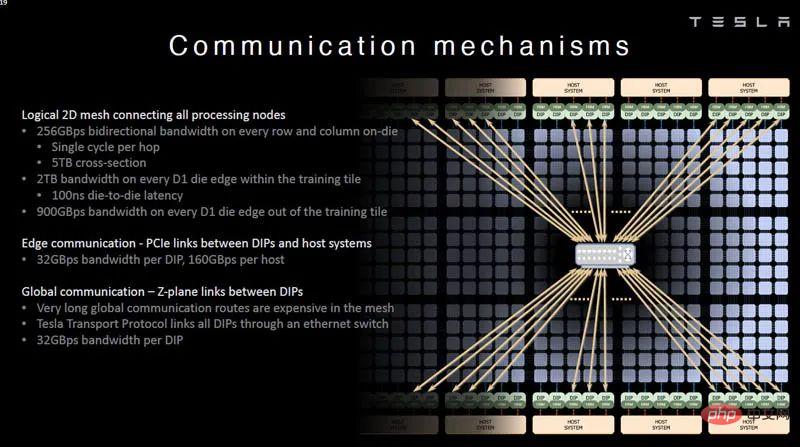

さらに、Tesla は、ホスト CPU とトレーニング プロセッサ間のブリッジとなる Dojo Interface Processor (DIP) も開発しました。

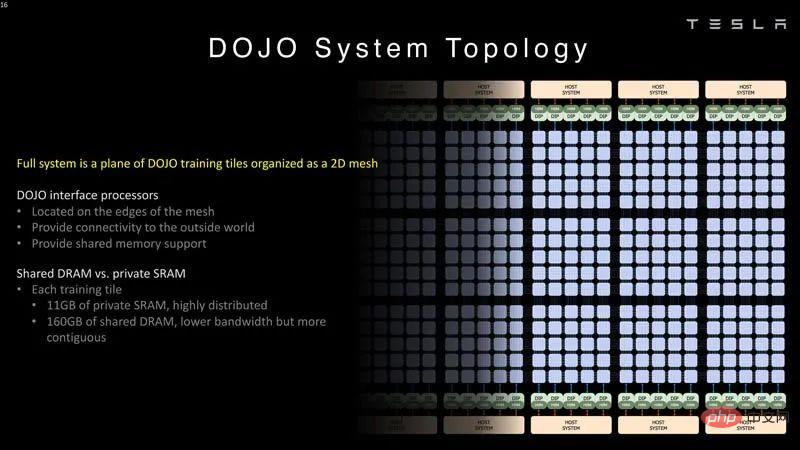

各 DIP には 32 GB の HBM があり、これらのカードのうち最大 5 枚を 900 GB/秒でトレーニング タイルに接続でき、合計 4.5 TB/秒の量になります。各タイルには、合計 160GB HBM。

Tesla の V1 構成は、これらのタイル (または 150 個の D1 ダイ) をアレイ内でペアにして、ホスト CPU ごとに 5 つの DIP カードを備えた 4 つのホスト CPU をサポートします。主張されている BF16 または CFP8 のパフォーマンスのエクサフロップを達成します。

ソフトウェア

このような特殊なコンピューティング アーキテクチャには、特殊なソフトウェア スタックが必要です。しかし、Venkataramanan と彼のチームは、プログラマビリティが Dojo の成功か失敗かを決定することを認識していました。

「これらのシステムを設計するとき、ソフトウェア仲間によるプログラムの容易さが最も重要です。研究者は、実行したい新しいアルゴリズムに対応するためにソフトウェア担当者が手書きのカーネルを作成するのを待ちません。」

これを行うために、Tesla はカーネルを使用するという考えを放棄し、コンパイラーを中心に Dojo のアーキテクチャを設計しました。

「私たちが行っているのは、PiTorch を使用することです。中間層を作成して、その下にあるハードウェアを並列化して拡張するのに役立ちます。その下にはすべてコンパイルされたコードがあります。」ソフトウェアを作成するには将来のあらゆるワークロードに適応できるスタックを構築するには、これが唯一の方法です。

Venkataramanan 氏は、ソフトウェアの柔軟性を強調しながらも、現在研究室で実行されているプラットフォームは Tesla に限定されていると指摘しました。

Dojo アーキテクチャの概要

上記を読んだ後、Dojo アーキテクチャを詳しく見てみましょう。

テスラは、機械学習用のエクサスケール人工知能システムを備えています。テスラには従業員を雇用し、テスラの車載システムと同様に自社アプリケーション専用のチップやシステムを構築するのに十分な資本がある。

テスラは、独自の AI チップだけでなく、スーパーコンピューターも開発しています。

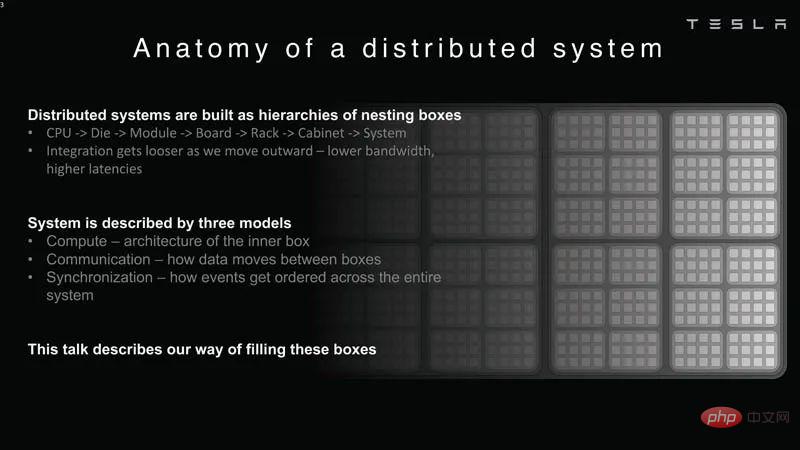

#分散システム分析

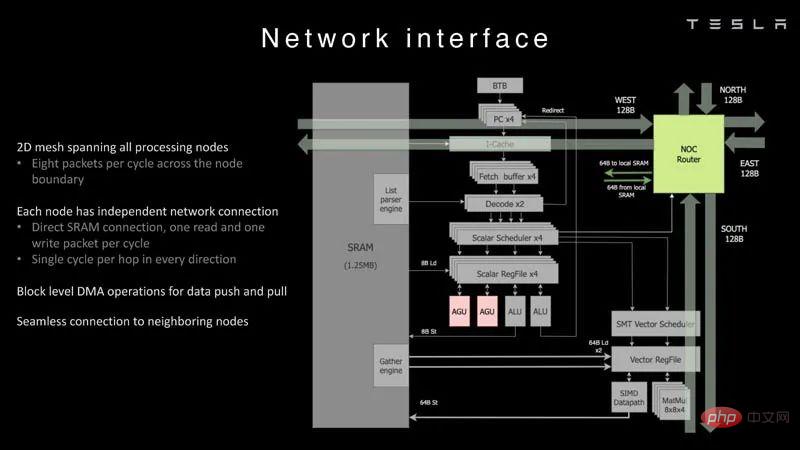

Dojo の各ノードには独自の CPU があり、メモリと通信インターフェイス。

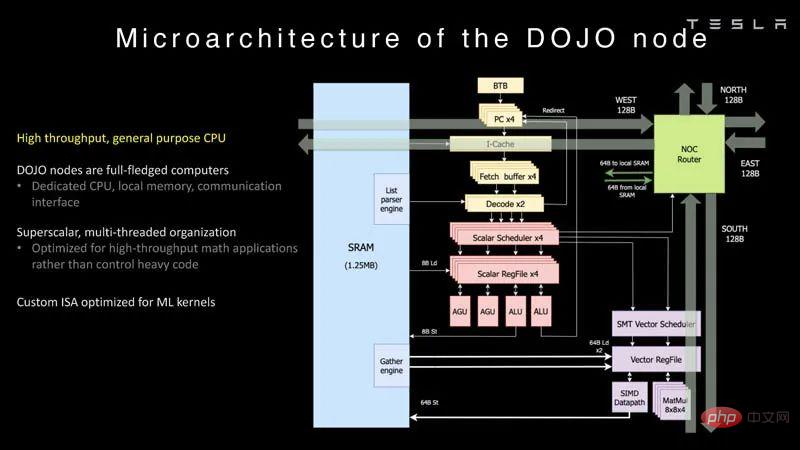

#Dojo ノード

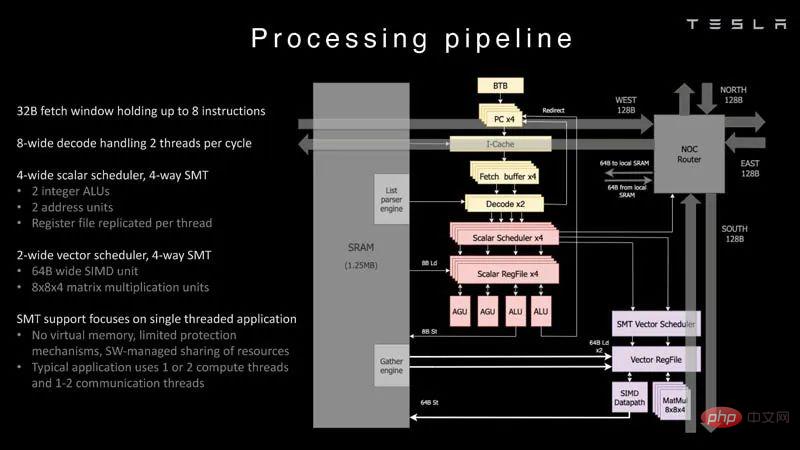

これは、Dojo プロセッサーの処理パイプラインです。 。

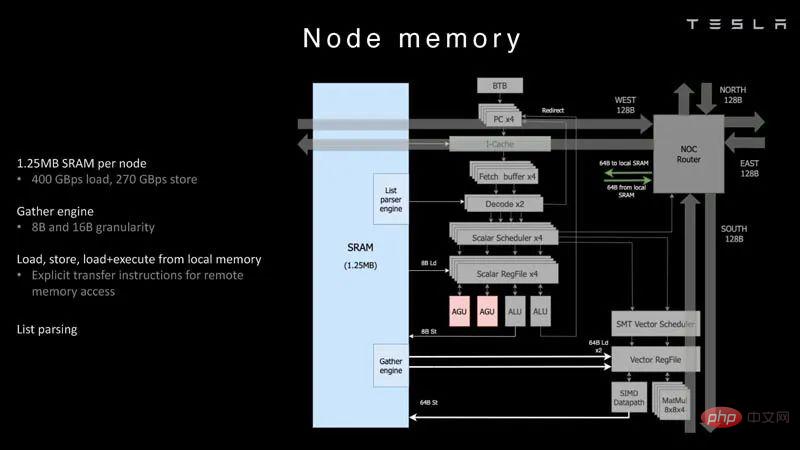

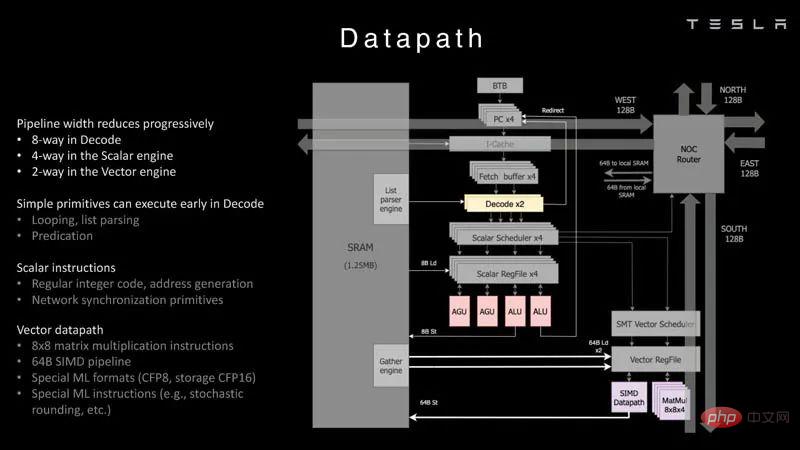

各ノードには 1.25MB の SRAM があります。 AI トレーニングおよび推論チップにおける一般的な手法は、メモリと計算を同じ場所に配置してデータ転送を最小限に抑えることですが、これは電力とパフォーマンスの観点から非常に高価です。

#ノード メモリ

#ノード メモリ

次に、各ノードが 2D グリッドに接続されます。 。

#ネットワーク インターフェイス

これは、データ パスの概要です。

データ パス

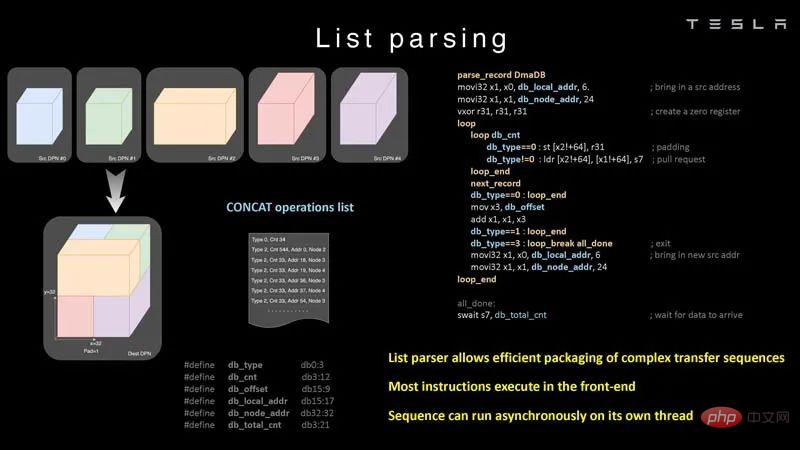

チップができることの例を次に示します。リストの解析を行います。

#リスト解析

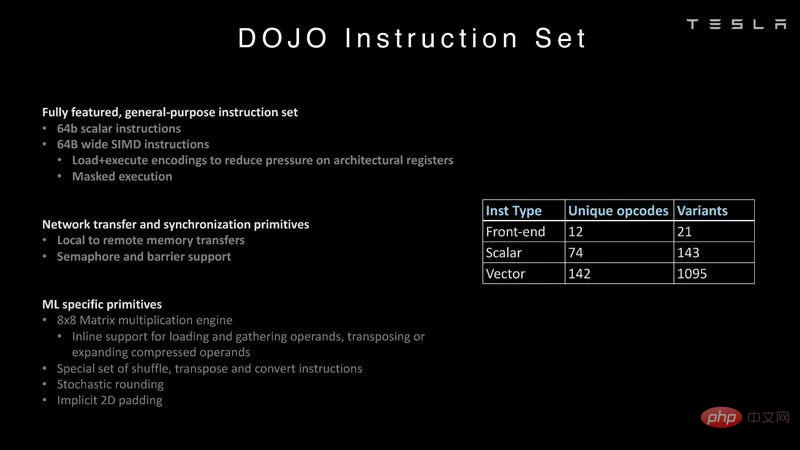

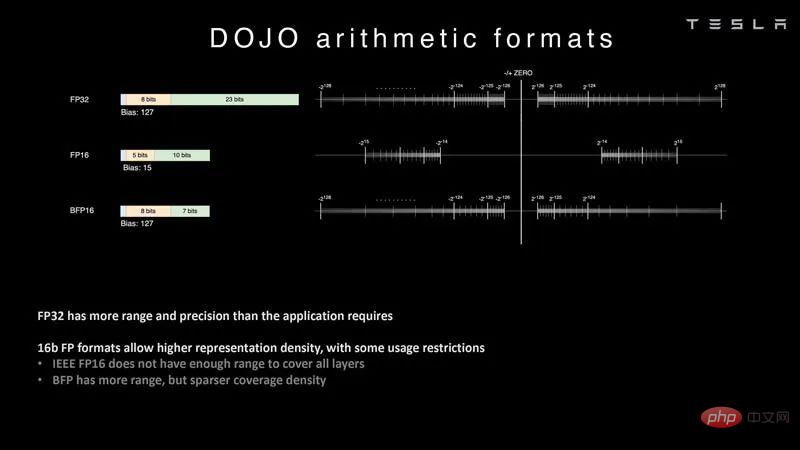

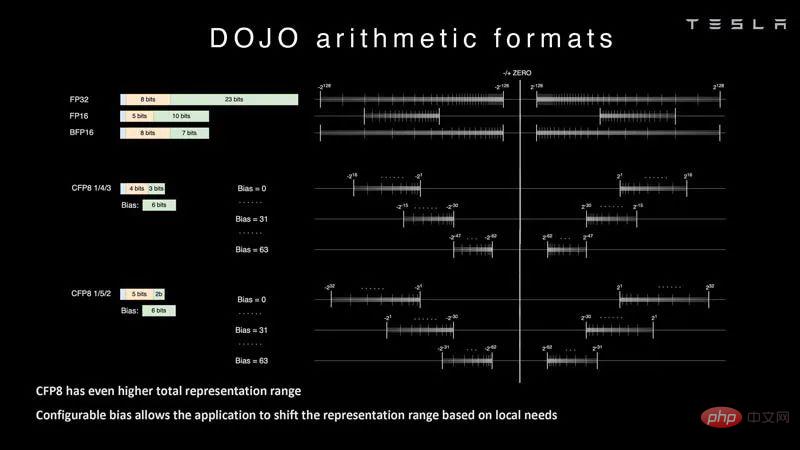

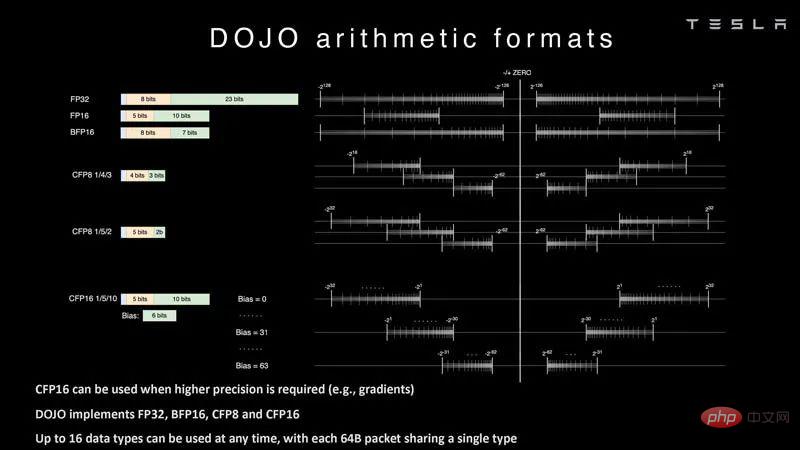

命令セットの詳細については、こちらをご覧ください。一般的な Intel、Arm、NVIDIA、AMD CPU/GPU 命令セットではなく、Tesla オリジナル。 命令セット 人工知能では、算術形式、特にチップがサポートする形式が非常に重要です。フォーマット。 Tesla は DOJO を使用して、FP32、FP16、BFP16 などの一般的なフォーマットを学習できます。これらは一般的な業界形式です。 #算術フォーマット Tesla は構成可能な FP8 または CFP8 にも取り組んでいます。 4/3 と 5/2 の範囲オプションがあります。これは、FP8 の NVIDIA H100 ホッパー構成に似ています。また、さまざまな FP8 タイプに焦点を当てた Untether.AI Boqueria 1458 RISC-V コア AI アクセラレータも確認できます。 #算術フォーマット 2

これらのコアは、製造されたコアに統合されます。型の中で。 TeslaのD1チップはTSMCによって7nmプロセスを使用して製造されています。各チップには 354 個の Dojo 処理ノードと 440MB の SRAM が搭載されています。

これらの D1 チップは、道場の練習タイルに。 D1 チップはテストされ、5×5 タイルに組み立てられます。これらのタイルの帯域幅はエッジごとに 4.5 TB/秒です。また、モジュールあたり 15kW、または 40 個の I/O ダイで使用される電力を差し引いた D1 チップあたり約 600W の電力供給エンベロープもあります。この比較は、企業がそのようなものを設計したくない場合に、Lightmatter Passage のようなものがより魅力的になる理由を示しています。

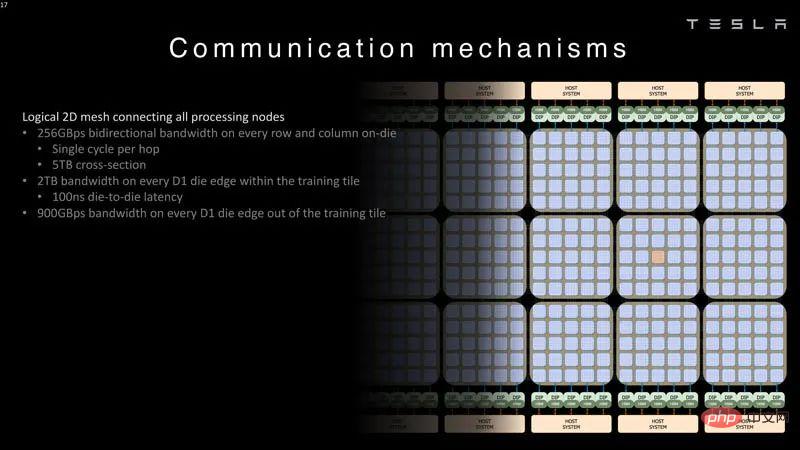

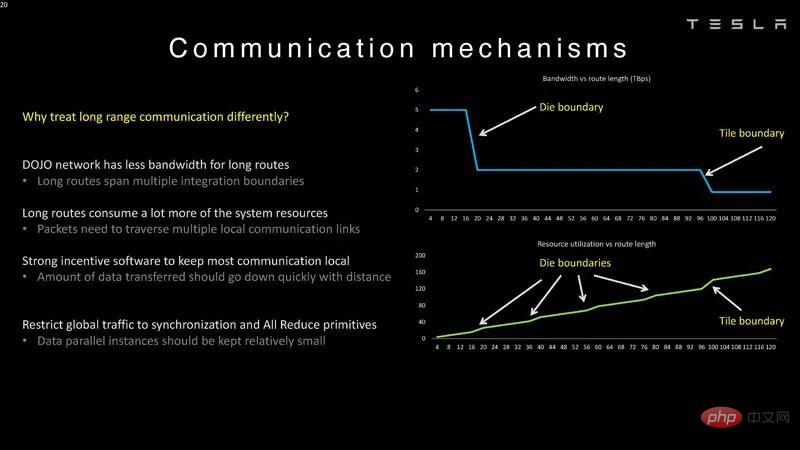

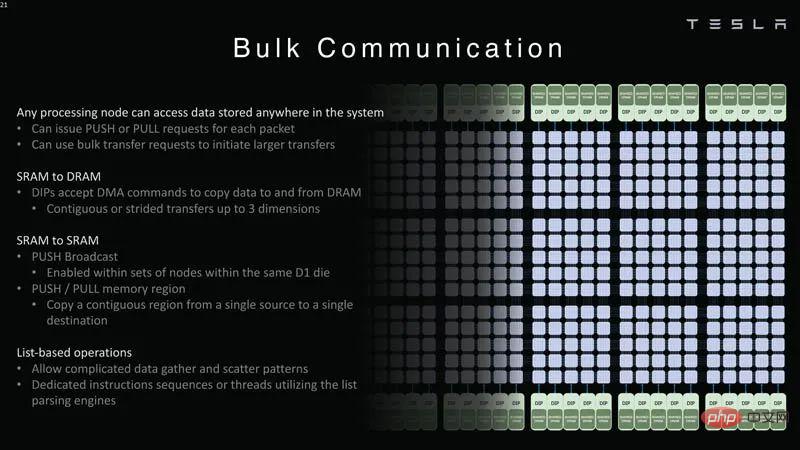

#セカンダリ統合ボックス Dojo トレーニング タイル Dojo インターフェイス プロセッサーは2D グリッドの端に位置します。各トレーニング ブロックには 11 GB の SRAM と 160 GB の共有 DRAM があります。 #Dojo システム トポロジ 以下は、Dojo システムを接続する 2D ネットワークです。処理ノード グリッド帯域幅データ。 #Dojo システム通信ロジックの 2 次元グリッド 各 DIP が提供するものホスト システムへの 32GB/秒のリンク。 ##Dojo システム通信 PCIe リンク DIP およびホスト テスラには、長距離ルート用の Z プレーン リンクもあります。講演の残りの部分で、テスラはシステムレベルのイノベーションについて語った。 #通信メカニズム これはダイとタイルの遅延境界です, そのため、Dojo では扱いが異なります。 Z プレーン リンクが必要な理由は、長いパスはコストがかかるためです。 #Dojo システム通信メカニズム

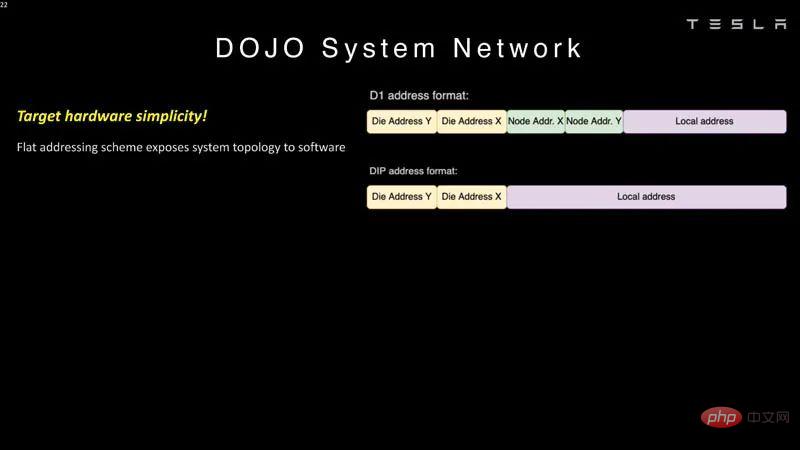

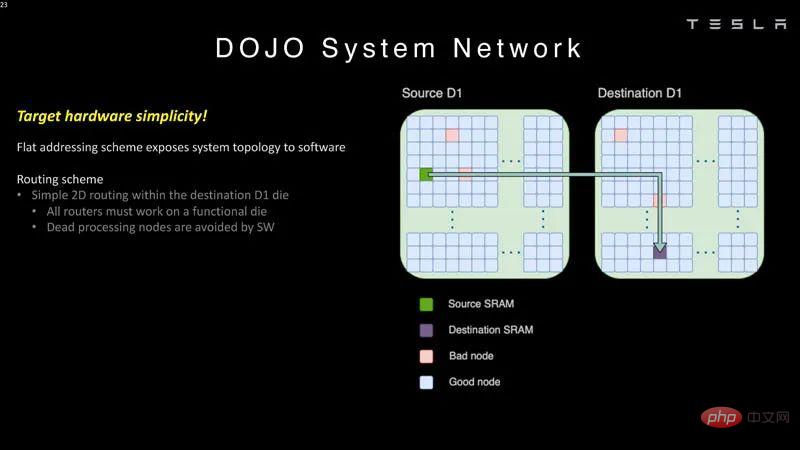

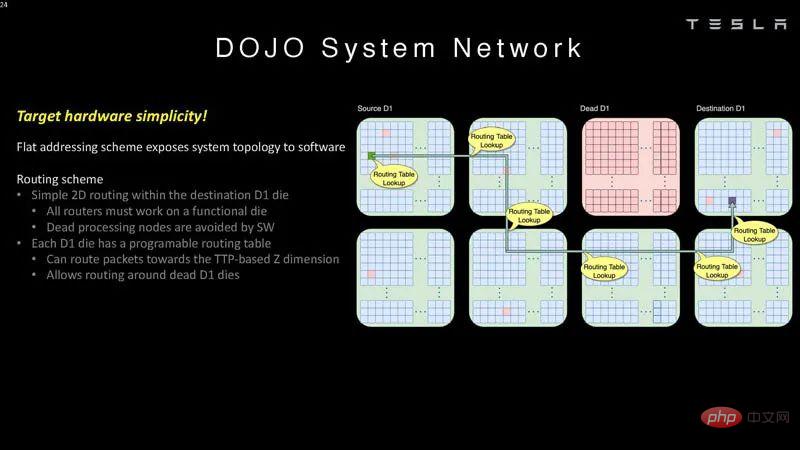

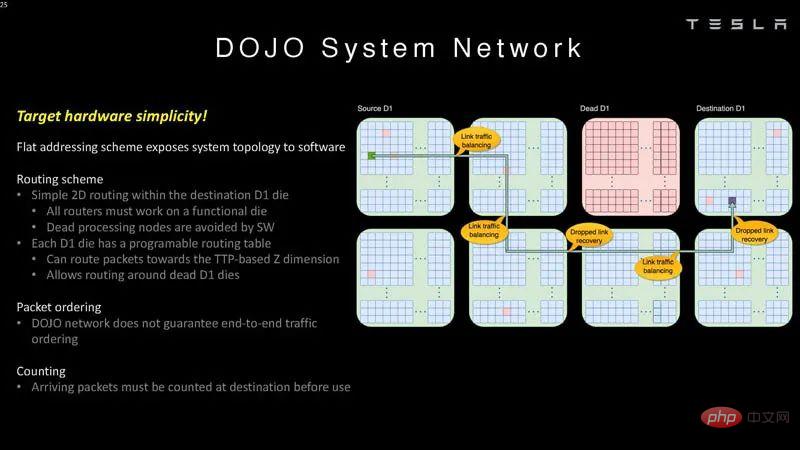

Dojo はフラット アドレッシング スキーム通信を使用します。

これらのチップはソフトウェアでバイパスできます 間違っています処理ノード。

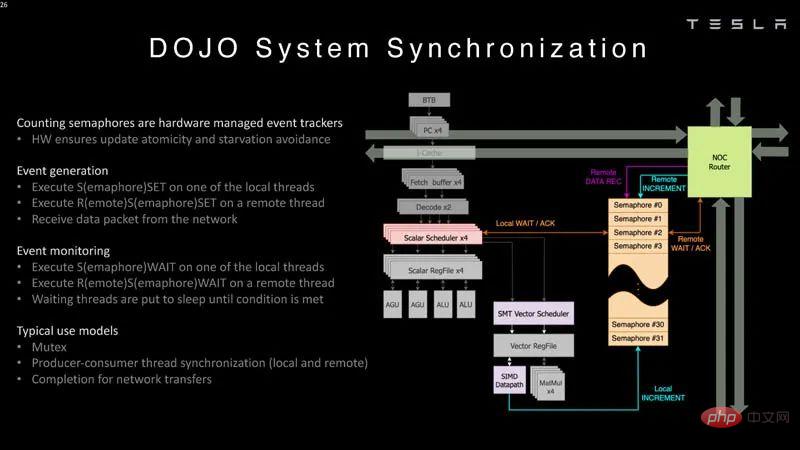

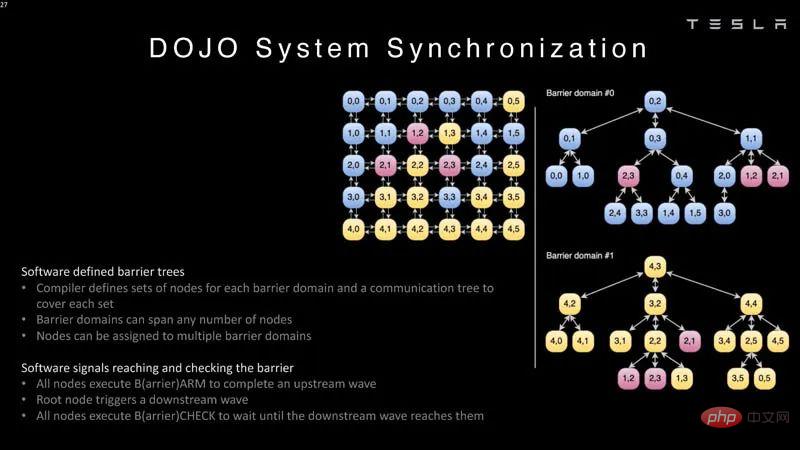

#システム ネットワーク 2 これは、ソフトウェアが次のことを理解する必要があることを意味します。システムトポロジ。 #システム ネットワーク 3 Dojo はエンドツーエンドを保証しません。トラフィックの順序付けが終了するため、宛先でパケットをカウントする必要があります。 #システム ネットワーク 4 システムへのパケットのカウント方法は次のとおりです。同期の一部。 #システム同期 。 システム同期 2

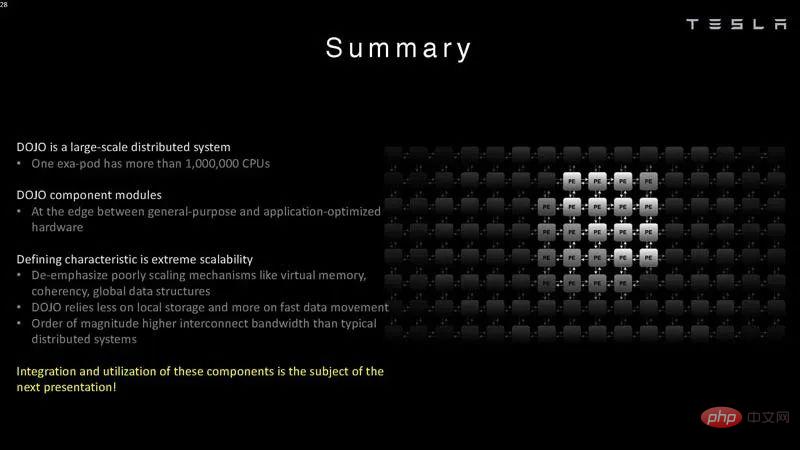

概要 Tesla は、特に大規模な作業を目的として Dojo を構築しました。通常、スタートアップ企業はシステムごとに 1 つまたはいくつかの AI チップを構築しようとします。明らかに、テスラはより大きな規模に焦点を当てています。 テスラが巨大な AI トレーニング場を持つことは、多くの意味で理にかなっています。さらに興味深いのは、市販のシステムを使用しているだけでなく、独自のチップとシステムも構築していることです。スカラー側の一部の ISA は RISC-V から借用していますが、ベクトル側と Tesla がカスタマイズしたアーキテクチャの多くは、多くの作業を必要とします。

#最初の統合ボックス D1 モールド

#最初の統合ボックス D1 モールド

#システム ネットワーク 1

#システム ネットワーク 1

以上がTesla Dojo スーパーコンピューティング アーキテクチャの詳細が初公開!自動運転は「ばらばら」の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。