ホームページ >テクノロジー周辺機器 >AI >テスラの自社開発チップ アーキテクチャからのインスピレーション

テスラの自社開発チップ アーキテクチャからのインスピレーション

- PHPz転載

- 2023-04-08 22:51:021113ブラウズ

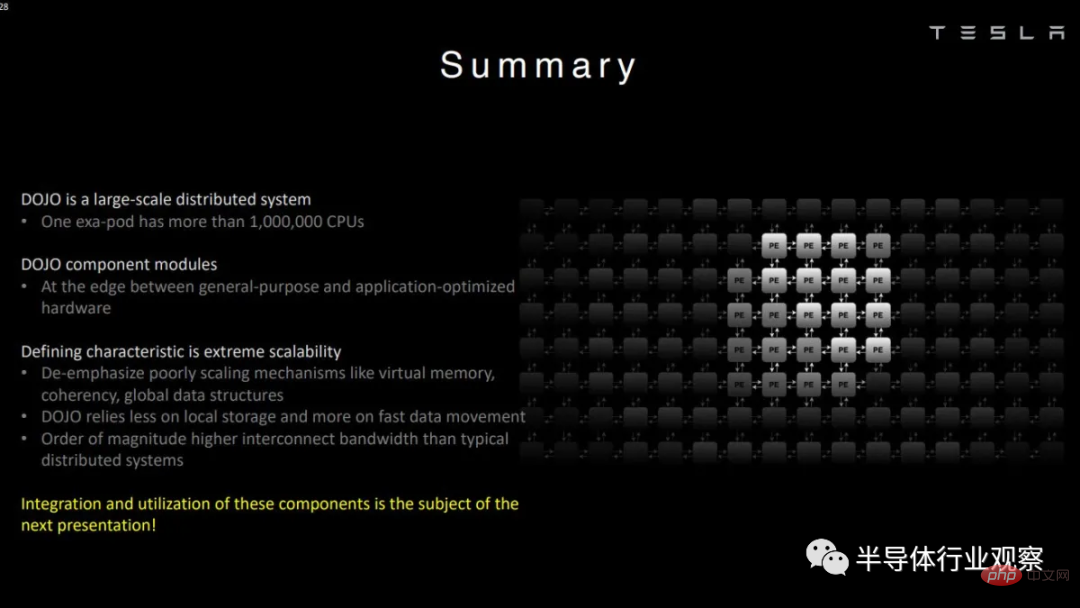

テスラが機械学習だけに興味があると言っても過言ではありません。実際、この電気自動車メーカーは、機械学習モデルのトレーニングに最適化された Dojo と呼ばれる社内スーパーコンピューターを構築しました。

他の多くのスーパーコンピューターとは異なり、Dojo は AMD、Intel、Nvidia などの既製の CPU や GPU を使用しません。 Tesla はニーズに基づいてマイクロアーキテクチャを設計し、より汎用的なアーキテクチャでは不可能なトレードオフを可能にしました。

この記事では、Hot Chips での Tesla のデモに基づいたアーキテクチャを見ていきます。アーキテクチャーには別の名前がないため、わかりやすくするために、以下で Dojo に言及するときは常に、アーキテクチャーについて話します。

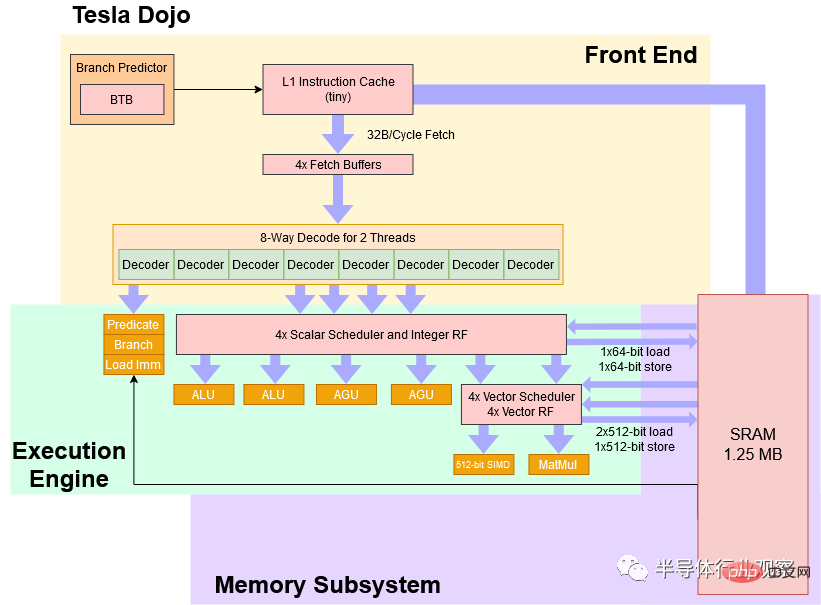

ブロック図

大まかに言えば、Dojo は控えめな 2 GHz で動作する 4 ウェイ SMT を備えた 8 幅のコアであり、CPU スタイルのパイプラインを備えているため、さまざまなアルゴリズムに対する耐性が高くなります。 GPU とブランチコード。 Dojo の命令セットはスカラーの点では RISC-V に似ていますが、Tesla のエンジニアは機械学習の高速化に重点を置いたベクトル命令のカスタム セットを追加しました。

Tesla Dojo コアの簡略ブロック図

Tesla は、Dojo を「高スループットの汎用 CPU」と説明しています。パフォーマンスの観点から見ると、これには確かにある程度の真実があります。しかし、コンピューティング密度を高めるために、Tesla は犠牲を払いました。デスクトップ、ラップトップ、スマートフォンで使い慣れた CPU と比較して、Dojo コアは非常に使いにくいものです。ある意味、Dojo カーネルは、従来の汎用 CPU カーネルよりも、IBM の Cell の SPE に似た処理を行います。

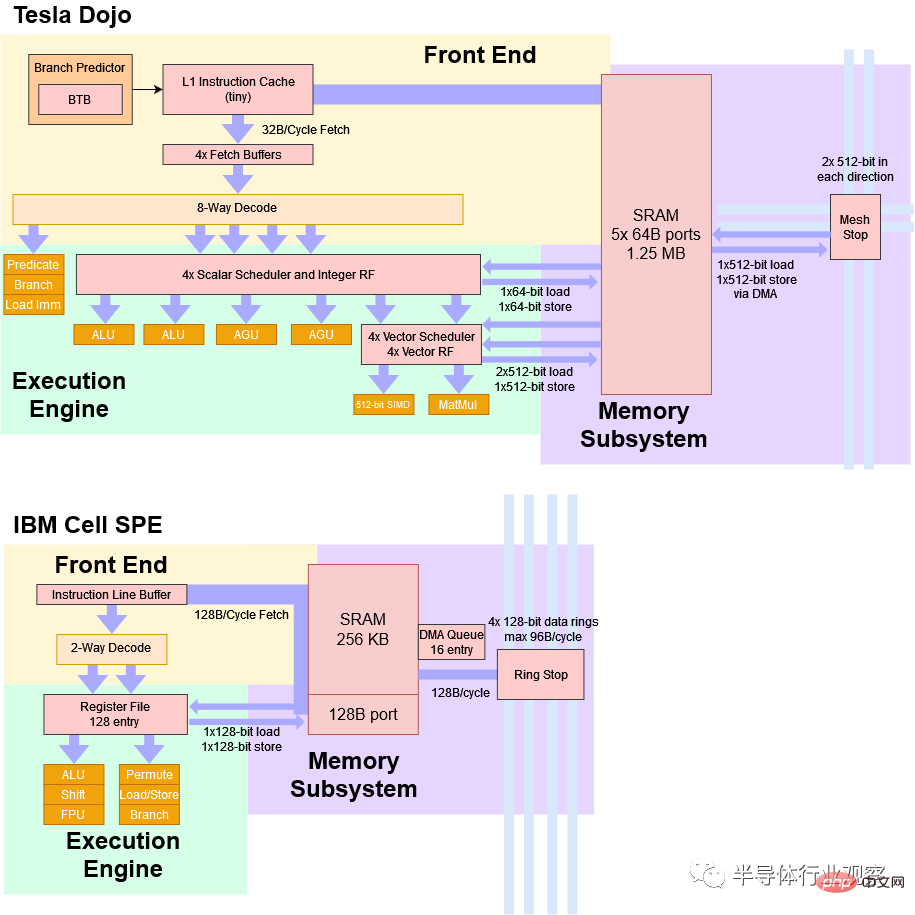

Cell の SPE は好きですか?

2000 年代半ばに導入された IBM Cell プロセッサーは、完全に機能する CPU コア (「パワー プロセッシング エレメント」または PPE: パワー プロセッシング エレメント) 制御で構成される 8 つの「シナジスティック プロセッシング エレメント」または SPE を備えています。一見すると、Dojo は SPE と多くの類似点があります。

Dojo と SPE はどちらもベクトル処理用に最適化されており、作業分散には個別のホスト プロセッサーに依存します。 Dojo または SPE で実行されるコードは、システム メモリに直接アクセスできません。代わりに、アプリケーションは主にローカル SRAM の小さな部分で動作することが期待されます。このローカル SRAM はソフトウェアによって管理されており、キャッシュとして使用することはできません。メイン メモリからのデータが必要な場合は、DMA 操作を使用してデータを取り込む必要があります。

最後に、Dojo と Cell の SPE はどちらも仮想メモリをサポートしていません。これが何を意味するかについては後ほど詳しく説明しますが、簡単に言うと、マルチタスクが非常に困難になります。

Tesla Dojo と IBM Cell SPE の非常に単純化された比較

Dojo はいくつかの重要な点で異なります。 Dojo は小規模なデプロイメントを念頭に置いて設計されていないため、ホスト・プロセッサーは別のホスト・システム上に常駐します。これらのホスト システムにはインターフェイス プロセッサーを備えた PCIe カードが搭載されており、高速ネットワーク リンクを介して Dojo チップに接続されます。対照的に、Cell のメインプロセッサは同じチップ上にあります。これにより、Dojo では不可能な、個々の Cell チップを個別にデプロイすることが可能になります。

Dojo の 1.25 MB の SRAM ローカル ブロックは、256 KB の SRAM しか搭載していない Cell SPE よりもはるかに大きく、より高い帯域幅を備えています。 Cell の 256 KB SRAM にはポートが 1 つだけあり、サイクルあたり 128B を供給できます。 Dojo の SRAM には 5 つの 64B ポートがあります。もちろん、アーキテクチャ上の目標は大きく異なります。 Dojo はワイドクロックとロークロックを備えていますが、Cell SPE は高クロック向けに設計された狭くて深いパイプラインを備えています。

フロントエンド: CPU の快適さなど

フロントエンドから始めて Dojo パイプラインを簡単に紹介しましょう。 Teslaの図にBTB(分岐ターゲットバッファ:分岐ターゲットバッファ)が示されているように、ある種の分岐予測器があります。 Dojo はベクター実行にダイ領域を優先的に費やす必要があるため、その予測機能は、AMD、ARM、Intel の高性能コアで見られるレベルに達しない可能性があります。ただし、基本的な分岐予測機能であっても、予測機能を使用しない場合に比べて大幅に改善されており、Dojo の分岐予測機能は、分岐コードやより大きな命令フットプリントを処理する場合に GPU よりも優れたパフォーマンスを提供するはずです。

分岐予測子が次の命令フェッチ ポインターを生成すると、Dojo は「小さな」命令キャッシュからスレッドごとのフェッチ バッファーにサイクルごとに 32 バイトをフェッチできます。この命令キャッシュは、ローカル SRAM に対する命令帯域幅の圧力を軽減し、データ側が競合を最小限に抑えて SRAM にアクセスできるようにするのに役立ちます。さらに、命令キャッシュは一貫性がありません。新しいコードがローカル SRAM にロードされる場合、新しいコードに分岐する前に命令キャッシュをフラッシュする必要があります。

Tesla からのホットチップのプレゼンテーション

Dojo のデコーダーは、フェッチバッファーから、2 つのスレッドからサイクルごとに 8 つの命令を処理できます。 SMT を搭載した CPU は通常、サイクルごとに 1 つのスレッドを処理し、サイクル境界でスレッドを切り替えるため、「サイクルごとに 2 つのスレッド」が何を意味するのか少し混乱しています。おそらく、Dojo はデコーダーを 2 つのクラスターに分割し、各ループでデータを供給する 2 つのスレッドを選択します。これにより、選択された分岐に対するデコード スループット ペナルティが軽減される可能性があります。

デコード中に、特定の命令 (分岐、述語演算、即時ロード (「リスト解析」) など) がフロントエンドで実行され、パイプラインから削除されることがあります。これは、リネーム機能でレジスタ間のコピーを排除する新しい x86 CPU に似ています。しかし、聞いた通りです。Dojo は、順序どおりのリタイアメントを維持するために、パイプラインを介して「削除」命令を追跡しません。他のプロセッサは、終了するすべてのものを追跡して、任意の命令境界で停止し、実行を再開するために必要なすべての状態を維持できます。この機能は「正確な例外」と呼ばれ、最新のオペレーティング システムはこれを使用して、ディスクへのページングや、コードがどこで壊れているかを正確に通知するなど、あらゆる種類の機能を提供します。

テスラは厳密な例外を気にしません。 Dojo には、「より正確な」例外を提供するためにパイプラインを介してより多くの命令が渡されるデバッグ モードがありますが、通常のアウトオブオーダー CPU のような秩序ある終了ロジックはありません。

Dojo の実行エンジン

幅広いフロントエンドを見た後、2 つの ALU と 2 つの AGU だけを備えた 4 幅の整数実行エンジンを見るのは少し奇妙かもしれません。ただし、一部の命令はフロントエンドで実行され破棄されるため、このじょうご型のパイプラインは理にかなっています。

Dojo は、スカラー整数のパフォーマンスが重要なクライアント システムにも組み込まれません。したがって、整数側は、制御フローとアドレス生成を処理してベクトルおよび行列セルに供給し続けるのに十分なスループットを提供します。

Dojo のベクトルおよび行列の実行エンドは、コア パイプラインのスカラー実行エンジンの後に配置され、2 つの実行パイプラインがあります。 2 つのパイプラインというと大したことではないように聞こえるかもしれませんが、Dojo にはこれらのパイプラインの背後に非常に広範な実行ユニットがあります。 1 つのパイプラインは 512 ビット ベクトルの実行を実行でき、もう 1 つのパイプラインは 8x8x4 行列の乗算を実行します。したがって、命令が十分な明示的な並列処理を公開している限り、Dojo は、特に行列ユニットを使用する場合に、非常に高いスループットを達成できます。 Tesla は、354 個の Dojo コアを搭載したチップは 2 GHz で 362 BF16 TFLOPS を達成できると主張しており、これは各コアがサイクルごとに 512 BF16 FLOPS を実行できることを示唆しています。

Dojo が完全に順番どおりに実行できるかどうかはわかりません。しかしテスラは、整数側はベクトル側よりはるかに先に実行できると述べ、スケジューラの 1 つがいっぱいになるまで停止していた命令を実行できることを示唆しました。順序付けられたリタイアメントの欠如は、アウトオブオーダーの実行機能も示しています。

一般に、アウトオブオーダー実行の実装には非常に複雑な作業が伴います。これは、CPU が命令を順番に実行する必要があるためです。 AMD、ARM、および Intel の高性能 CPU は、結果をプログラム順序でコミットできるように、大きなリオーダー バッファ (およびその他の構造) を使用して命令を追跡します。これは、プログラムがゼロ除算などの愚かなことを実行した場合、これらのコアはどの命令が間違っていたのかを正確に示すことができることを意味します。さらに、障害が発生する前ではなく、障害が発生した後ではないすべての命令のアクションを反映する CPU 状態を表示できます。これは、命令が間違った原因となったものを修正して、実行を再開できることを意味します。ドージョーはこの能力を放棄します。その代わり、Dojo はパイプラインを介して各命令を追跡することに伴う電力と領域のオーバーヘッドを回避し、結果がプログラムの順序で配信されることを保証します。

SRAM アクセス

通常、ここではキャッシュについて話します。ただし、Dojo はシステム メモリに直接アクセスできないため、SRAM の 1.25 MB ブロックについて説明します。サイクルあたり 2 つの 512 ビット ロードを処理できるため、AVX-512 対応 Intel CPU に匹敵するサイクルあたりの帯域幅が得られます。テスラによると、SRAMには512ビットポートが5つ(ロードポート2つ、ストアポート1つ、ストップツーグリッドポート2つ)あるという。しかし、スカラー側には AGU が 2 つしかないため、おそらくコアがサイクルごとに 2 つの 512 ビット ロードと 1 つの 512 ビット ストアを処理できないことを意味します。

Dojo のローカル SRAM ブロックはキャッシュされないため、データとともに保存されるタグやステータス ビットは必要ありません。また、SRAM にはその前に L1D キャッシュがないため、L2 キャッシュに近いサイズであっても、ボトルネックを引き起こすことなくすべてのロードおよびストア命令を処理できる十分な速度が必要です。 SRAM をキャッシュとして実装しないのは、レイテンシーを低く抑えるための Tesla の方法かもしれません。昔の AMD の Hammer アーキテクチャを振り返ると、L1D ミスの検出後に L2 の 1 MB にアクセスするのに 8 サイクルかかったことがわかります (合計レイテンシは 12 サイクル)。 1 MB の SRAM がキャッシュとして使用されるのではなく直接アドレス指定された場合、3 つのステージが削除され、レイテンシが 5 サイクルに短縮される可能性があります:

L2 キャッシュ アクセスに関係するパイプライン ステージを示す以前の Hot Chips プレゼンテーションのスライド。 L2 がキャッシュではない場合、スキップできるステージは赤色でマークされます。

何十年にもわたるプロセス ノードの改善と、Athlon よりもさらに低いクロック速度の目標を考慮すると、Tesla がどのようにして L1 のようなレイテンシで L2 サイズの SRAM ブロックにアクセスできたかは簡単にわかります。 L1 キャッシュをスキップすると、確実に面積と電力が節約されます。

レイテンシー、エリア、コアの複雑さをさらに軽減するために、Dojo は仮想メモリーをサポートしていません。したがって、TLB やページ ウォーク メカニズムはありません。最新のオペレーティング システムは仮想メモリを利用して、各プロセスに独自のメモリ ビューを与えます。プログラムが使用するメモリ アドレスは、物理メモリ アドレスに直接アクセスするのではなく、オペレーティング システムによって設定されたページング構造を使用して CPU によって物理アドレスに変換されます。これは、最新のオペレーティング システムがプログラムを相互に分離し、1 つの不正な動作を行うアプリケーションがシステム全体をダウンさせることを防ぐ方法です。

仮想メモリは、物理メモリよりも多くのプログラムを実行できる方法でもあります。実メモリが不足すると、オペレーティング システムはページのマップを解除してディスクに書き込み、プログラムに必要なメモリを与えます。他のくだらないプログラムがそのメモリにアクセスしようとすると、CPU は仮想アドレスを物理アドレスに変換しようとしますが、その変換が存在しないことがわかります。 CPU はページ フォールト例外をスローします。オペレーティング システムは、追い出されたページを物理メモリに読み戻し、ページ テーブル エントリに記入することによって処理します。

Dojo ではこれはどれも不可能です。カーネルの 4-way SMT 機能は、マルチタスクのパフォーマンスを向上させるというよりも、単一のアプリケーションを明示的な並列処理にさらすことに重点を置いています。たとえば、あるスレッドがベクトル計算を実行している間に、別のスレッドがシステム メモリから (DMA 経由で) データを SRAM に非同期的にロードできます。

設計をさらに簡素化するために、Dojo はわずか 21 アドレス ビットで SRAM をアドレス指定できるため、Dojo の AGU とアドレス指定バスを簡素化できます。これらのトレードオフにより、Tesla はこの SRAM の前に別の L1 データ キャッシュを実装する必要がなく、十分に低い遅延でこの SRAM にアクセスできるようになる可能性があります。

メモリアクセス

システムメモリと言えば、Dojo チップはメモリに直接接続されていません。代わりに、HBM を搭載したインターフェイス プロセッサに接続します。これらのインターフェイス プロセッサは、ホスト システムとの通信も担当します。

25 個の独立したチップを備えた Dojo タイルは、160 GB の HBM メモリにアクセスできます Tesla は、タイル境界を越えて各チップエッジから 900 GB/s を転送できると述べています。これは、4.5 TB/s のリンク帯域幅で転送できることを意味しますアクセス インターフェイス プロセッサとその HBM。 HBM へのアクセスは別のチップを経由するため、アクセスの待ち時間が非常に長くなる可能性があります。

は小さいですが、どうやって作るのですか?

Dojo は、少なくともある程度の OoO 実行機能、適切なベクトル スループット、および行列乗算ユニットを備えた 8 ワイド カーネルです。ただし、1.25 MB のローカル SRAM があっても、最終的には非常に小さなコアになります。比較すると、富士通の A64FX は、同じプロセス ノード上で 2 倍以上の面積を占めます。プロセッサーの設計では、適切なトレードオフを行うことが重要です。 Tesla は、チップ上に多数のコアを詰め込むことで機械学習のスループットを最大化したいと考えているため、個々のコアは小さくなければなりません。ゾーンの効率を高めるために、Dojo はいくつかの使い慣れたテクニックを使用します。控えめな 2 GHz で動作します。クロックが低い回路ほど占有面積が小さくなる傾向があります。基本的な分岐予測機能と小規模な命令キャッシュが含まれる場合があります。プログラムのコード フットプリントが大きい場合、または多くの分岐がある場合、パフォーマンスがある程度犠牲になります。

しかし、Tesla は、内部ワークロードの実行に必要のない機能を削除することで、電力とエリアの使用量をさらに削減します。データ側のキャッシュは行わず、仮想メモリもサポートせず、正確な例外もサポートしません。

その結果、最新の CPU コアのパフォーマンスの柔軟性を提供しながらも、多くの点で Intel 8086 よりもユーザーやプログラマにとって使いにくいプロセッサ コアが誕生しました。コアに加えて、Tesla は導入専用に Dojo チップを設計することでチップ面積を大規模に節約しています。

物理実装

縮小すると、Dojo コアは D1 と呼ばれる非常に大きな 645 mm2 ダイに実装されます。私たちがよく知っている他のチップとは異なり、単一の Dojo チップだけでは十分ではありません。 DDR または PCIe コントローラーはありません。ダイのエッジの周囲には IO インターフェイスがあり、ダイが約 100 ns の待ち時間で隣接するダイと通信できるようになります。

システム メモリにアクセスするには、Dojo D1 チップがオンボード HBM を備えたインターフェイス プロセッサと通信する必要があります。インターフェイス プロセッサは、PCIe 経由でホスト システムに接続されます (インターフェイス プロセッサは PCIe カードにインストールされます)。理論的には、最小限の機能を備えた Dojo デプロイメントには、Dojo チップ、インターフェース・プロセッサー・カード、およびホスト・システムが含まれます。しかし、テスラはスケール感を提供するために、それぞれ 25 個のダイを含むモジュールで Dojo ダイを展開しています。 Dojo D1 ダイは、スーパーコンピューターのビルディング ブロックとして特別に設計されたものであり、それ以上のものではありません。

この特殊化により、より多くのダイ領域を節約できます。 Dojo D1 は、DDR および PCIe コントローラーのスペースを無駄にしません。隣接するダイと接続するように設計された外側のカスタム IO コネクタを除き、ダイの大部分は大規模な Dojo コアによって占められています。

対照的に、より柔軟な展開を念頭に置いて設計されたチップは、IO に多くのスペースを費やします。 AMD の Zen 1「Zeppelin」チップは、これを非常によく示しています。 Zeppelin は、DDR4 メモリ、PCIe デバイス、SATA ドライブ、USB デバイスに直接接続できるため、顧客の要件に最適です。サーバーでは、IFOP インターフェイスを使用して隣接するチップと通信できます。 IFOP の近くにある SRAM の大きなチャンクはスヌープ フィルターである可能性があり、コア数の多い設定でキャッシュ コヒーレンスを効率的に維持するのに役立ちます。 Dojo はコア間でキャッシュの一貫性を維持しようとせず、スヌープ フィルタリングに SRAM を使用しません。

ISSCC 2021でのAMDのチップレットデモより

AMDは、この費用を支払うために「Zeppelin」ダイ領域の約44%をコアとキャッシュ以外のロジックに専用にすることでこれを達成しました柔軟性。 Dojo は、SRAM とコア以外にダイ領域の 28.9% のみを使用します。

最後の言葉

Tesla Dojo スーパーコンピューターの背後にあるマイクロアーキテクチャは、分岐コードを処理する CPU の能力を維持しながら、非常に高い計算密度を達成する方法を示しています。そこに到達するには、現代のコンピューティング体験を定義する快適さのほとんどを放棄する必要があります。仮に、Dojo コアを中心にデスクトップを構築できれば、MS-DOS を使用したことのある人なら誰でもその経験に親しみを感じるでしょう。複数のアプリケーションを同時に実行することはできません。アプリケーションが 1 つ不正に動作すると、システムの再起動が必要になる場合があります。プログラムを実行するのに十分な RAM がない場合は、(ディスクへのページングを行わずに) プログラムを実行することを完全に忘れてしまう可能性があります。

しかし、これらのトレードオフは、テスラのスーパーコンピューターでは完全に理にかなっています。 Tesla では、実行中の複数のアプリケーションを同時に処理するために Dojo コアを必要としません。Dojo 内で信頼できるコードを実行するだけで済みます。したがって、Tesla は仮想メモリのサポートを気にしていません。同様に、Dojo 上で実行される機械学習プログラムは、その特定のシステムを念頭に置いて作成されます。利用可能な以上のメモリを必要とする可能性のある任意のプログラムのバッチが作成されることはありません。これは、メモリのオーバーコミット、メモリ圧縮、ディスク間でのメモリ ページのスワップなどの手法を可能にするための正確な例外 (および仮想メモリ) が必要ないことを意味します。正確な例外はデバッグにも役立ちますが、Tesla では別のデバッグ モードを使用することでより安価な方法で例外を実行します。

Tesla が高い計算密度を達成するために採用しているトレードオフは、コンシューマやサーバーの CPU では不可能であると考えて間違いありません。しかし、実際に使ってみるととても楽しいので、時間をかけてホットチップスで披露してくれたテスラに感謝しなければなりません。過去 20 年間にわたり、プロセス ノードの改善は鈍化しており、その結果、シングルスレッドのパフォーマンスの進歩はさらに遅くなりました。過去 5 年間、電力と冷却の制約によりマルチスレッドのパフォーマンスが低下してきました。しかし、より多くのコンピューティング能力に対するニーズは衰えていないため、企業は対応するために、より特化したハードウェアに目を向けています。

Tesla の Dojo スーパーコンピューターのアーキテクチャは、計算密度を高めるためにどのようにトレードオフが行われるか、また現在の傾向がスループットに制約のあるアプリケーション向けに特殊なハードウェアの導入をどのように支持しているかを示す好例です。

以上がテスラの自社開発チップ アーキテクチャからのインスピレーションの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。