Maison >Périphériques technologiques >IA >Voici la bouée de sauvetage des transistors : CMOS empilé 3D, la loi de Moore va-t-elle perdurer encore 10 ans ?

Voici la bouée de sauvetage des transistors : CMOS empilé 3D, la loi de Moore va-t-elle perdurer encore 10 ans ?

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBavant

- 2023-04-14 16:13:031614parcourir

Le transistor est connu comme « la plus grande invention du 20ème siècle ».

Son émergence a jeté les bases de la production de circuits intégrés, de microprocesseurs et de mémoire informatique.

En 1965, la « loi de Moore » a été proposée et est devenue la règle d'or de l'industrie des semi-conducteurs pendant des décennies.

Cela montre que tous les 18 à 24 mois, le nombre de transistors emballés sur une puce doublera, et les performances de la puce doubleront également.

Cependant, avec l'introduction continue de nouveaux nœuds de processus, le nombre d'atomes dans les transistors est devenu de moins en moins et diverses limites physiques limitent le développement ultérieur de la loi de Moore.

Certaines personnes pensent même que la loi de Moore est révolue.

Par conséquent, afin de « sauver » la loi de Moore, les ingénieurs doivent modifier la structure du transistor, continuer à réduire la surface et la consommation d'énergie et améliorer ses performances.

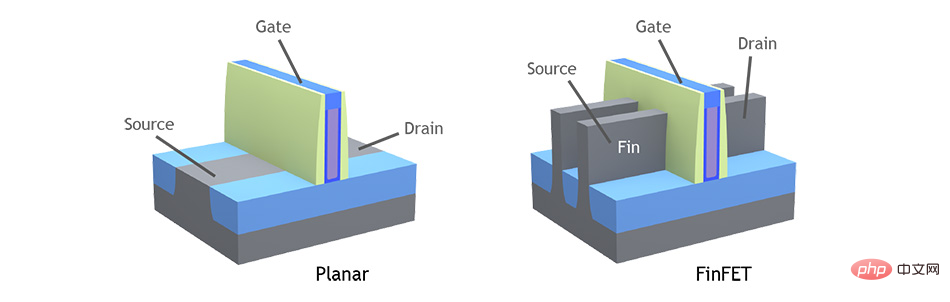

Dans la seconde moitié du 20e siècle, la conception de transistors planaires (Planar Transistor) était principalement populaire. À partir des années 2010, les appareils 3D en forme d’aileron ont progressivement remplacé les modèles plats.

Maintenant, une toute nouvelle structure de conception de transistor, le Gate All Around Transistor (GAA), est le successeur du FinFET et est sur le point d'entrer en production.

Mais, il faut regarder plus loin. Car même avec cette nouvelle architecture de transistor RibbonFET proposée par Intel, notre capacité à réduire la taille a des limites.

Croyez que les semi-conducteurs à oxyde métallique complémentaire (CMOS) ou CFET (transistors à effet de champ complémentaires) empilés en 3D seront la clé pour étendre la loi de Moore au cours de la prochaine décennie.

L'évolution des transistors

Chaque transistor à effet de champ à semi-conducteur à oxyde métallique (MOSFET) possède le même ensemble de composants de base :

pile de grille, région de canal (région de canal), source, drain

La source et le drain sont dopés chimiquement de sorte qu'ils soient soit riches en électrons mobiles (type n), soit dépourvus d'électrons (type p). La région du canal a le dopage opposé à celui de la source et du drain.

Dans la version planaire du transistor dans les microprocesseurs avancés avant 2011, la pile de grille du MOSFET se trouvait juste au-dessus de la zone du canal et était utilisée pour projeter le champ électrique dans la zone du canal.

L'application d'une tension suffisamment importante à la grille (par rapport à la source) formera une couche de porteurs de charge mobiles dans la zone du canal, permettant au courant de circuler entre la source et le drain.

Afin de réduire la taille des conceptions de transistors planaires, un "effet canal court" est devenu le centre d'intérêt des physiciens.

Étant donné que la technologie des processus continue de s'améliorer, la largeur de l'électrode de grille dans le transistor est de plus en plus réduite. Vous savez, lorsque la porte est inférieure à 20 nm, le courant sera hors de contrôle et le courant source pénétrera dans la porte et atteindra directement le drain.

À ce moment-là, une « fuite » se produira, ce qui entraînera une forte augmentation de la consommation d'énergie de la puce.

Afin de résoudre ce problème, une nouvelle technologie de transistor FinFET est proposée. Il enroule le portail autour d'un canal sur trois côtés pour offrir un meilleur contrôle statique.

FinFET réduit la consommation d'énergie d'environ 50 % au même niveau de performances que l'architecture planaire de la génération précédente. Les FinFET commutent également plus rapidement, offrant une amélioration des performances de 37 %.

En 2011, Intel a introduit FinFET sur le nœud 22 nm qu'il a lancé et l'a utilisé dans la production de ses processeurs Core de troisième génération.

Depuis lors, FinFET est devenu le cheval de bataille de la loi de Moore.

Cependant, nous avons également perdu quelque chose lorsque nous sommes passés à FinFET.

Dans les dispositifs planaires, la largeur du transistor est définie par photolithographie, c'est donc un paramètre très flexible.

Mais dans FinFET, la largeur du transistor se présente par incréments discrets, en ajoutant une ailette à la fois. Cette propriété est souvent appelée quantification des ailerons.

Malgré la flexibilité des FinFET, la quantification des ailettes reste une contrainte de conception importante. Les règles de conception qui l'entourent et le désir d'ajouter plus d'ailettes pour améliorer les performances, augmentent la surface globale de la cellule logique et compliquent la pile d'interconnexion qui transforme un seul transistor en un circuit logique complet.

Il augmente également la capacité du transistor, réduisant ainsi sa vitesse de commutation. Ainsi, même si FinFET nous a bien servi en tant que bête de somme de l’industrie, une nouvelle approche plus raffinée est nécessaire.

C'est cette approche qui a conduit les physiciens à inventer le prochain transistor 3D - RibbonFET.

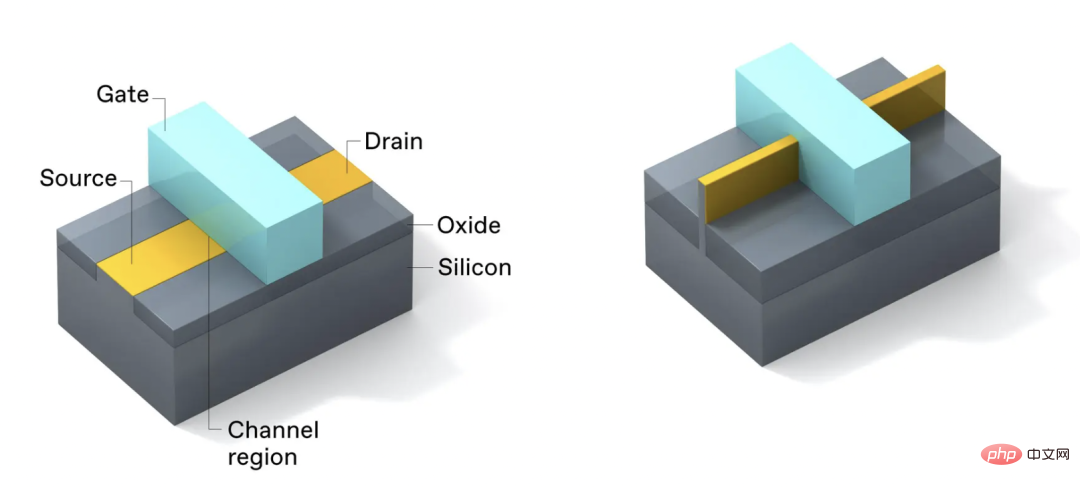

Dans RibbonFET, la grille entoure la zone du canal du transistor pour améliorer le contrôle des porteurs de charge. La nouvelle structure permet également de meilleures performances et une optimisation plus raffinée.

Plus précisément, la grille entoure complètement les canaux, permettant un contrôle plus strict des porteurs de charge dans les canaux, qui sont désormais formés de rubans de silicium à l'échelle nanométrique.

Grâce à ces nanorubans (nanosheets), il est possible de modifier la largeur du transistor à volonté en utilisant à nouveau la photolithographie.

Après avoir supprimé les contraintes de quantification, il est possible de générer une largeur de taille appropriée pour l'application. Cela nous permet d’équilibrer puissance, performances et coût.

Plus important encore, en s'empilant et en fonctionnant en parallèle, les appareils peuvent générer plus de courant et améliorer les performances sans augmenter la surface.

Par conséquent, Intel estime que RibbonFET est le meilleur choix pour obtenir des performances plus élevées à une puissance raisonnable.

Ils introduiront la structure RibbonFET sur le processus Intel 20A en 2024.

CMOS empilé 3D

Une chose que les transistors planaires, FinFET et RibbonFET ont en commun est qu'ils utilisent tous la technologie CMOS Comme mentionné précédemment, le CMOS est composé de transistors de type n et de type p. . Cette technologie est devenue courante dans les années 1980 car elle consomme beaucoup moins de courant que les autres alternatives. Moins de courant signifie des fréquences de fonctionnement plus élevées et une densité de transistors plus élevée.

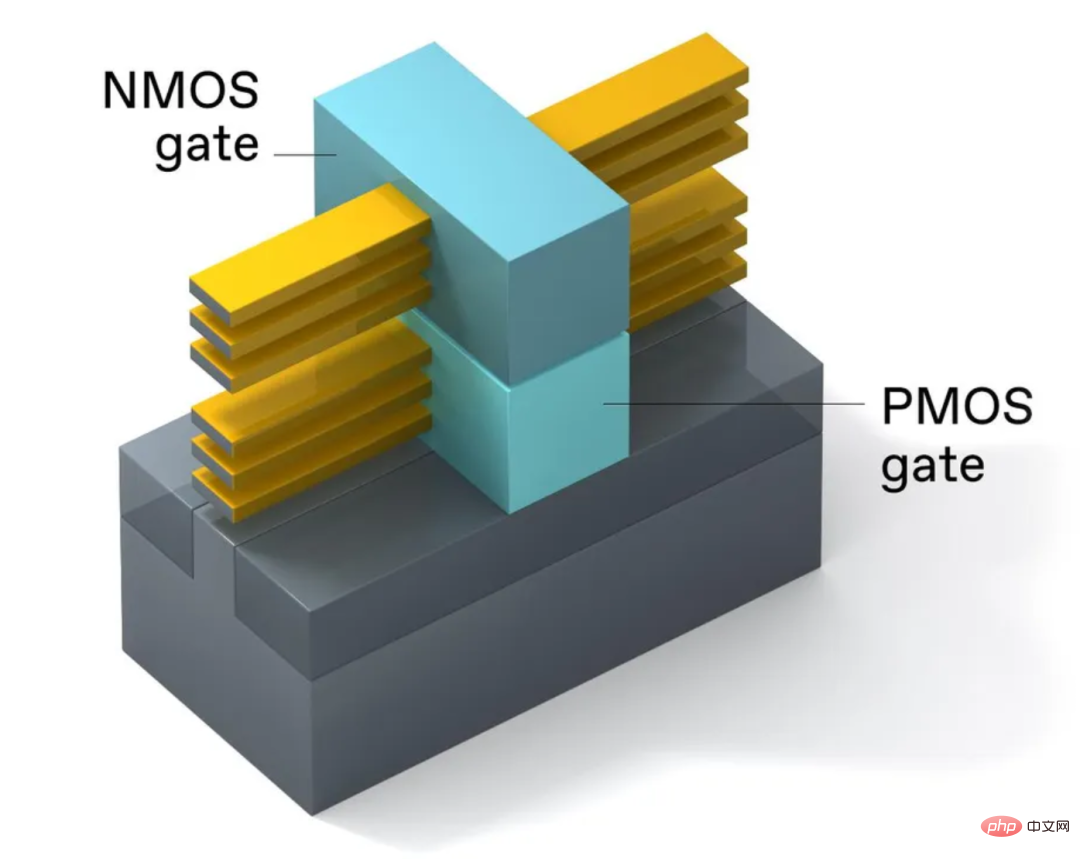

À ce jour, toutes les technologies CMOS ont placé côte à côte des paires standards de transistors NMOS et PMOS. Cependant, dans le discours d'ouverture de la Conférence internationale sur les composants électroniques (IEDM) de l'IEEE 2019, un concept de transistors « empilés en 3D » a été proposé, plaçant des transistors NMOS au-dessus des transistors PMOS.

Lors de l'IEDM 2020, le premier onduleur conçu à partir de circuits logiques utilisant cette technologie 3D a été présenté. Le CMOS empilé 3D réduit efficacement de moitié l'encombrement de l'onduleur, doublant la densité de la surface du transistor et repoussant encore les limites de la loi de Moore.

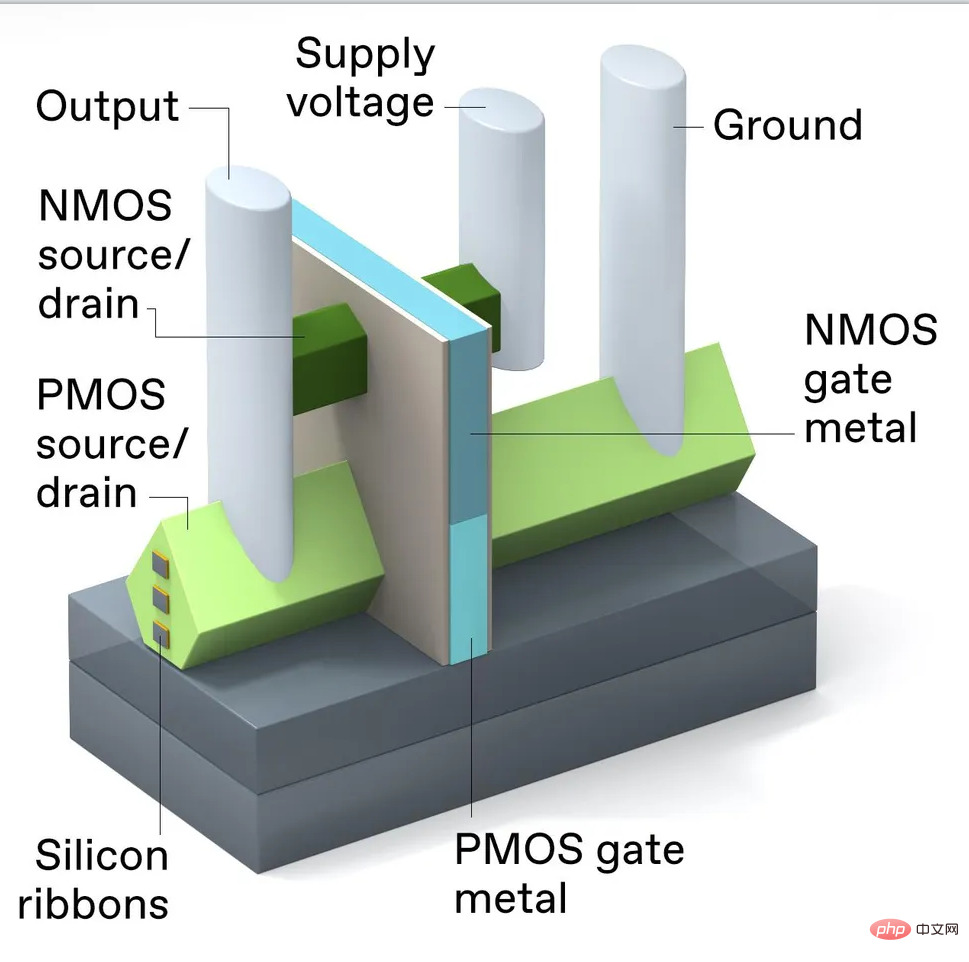

Structure CMOS empilée 3D, plaçant le périphérique PMOS au-dessus du périphérique NMOS, avec une zone totale identique à une zone RibbonFET. Les portes NMOS et PMOS utilisent différents matériaux métalliques

Pour utiliser le CMOS empilé en 3D, il existe de nombreux défis d'intégration de processus à résoudre, dont certains impliquent les limites du traitement et de la fabrication du CMOS.

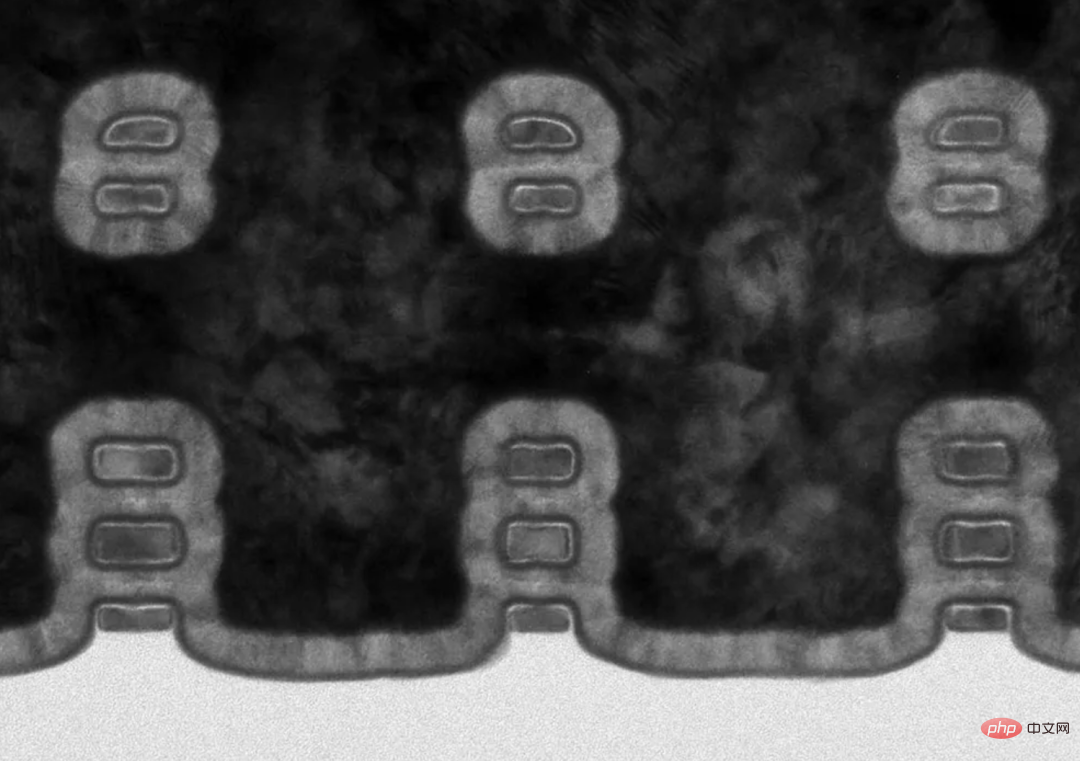

Comment y parvenir ? La fabrication de CMOS 3D auto-alignés commence par des tranches de silicium. Sur la tranche, nous déposons couche après couche de silicium et de silicium germanium, une structure appelée « super-réseau ». Des motifs photolithographiques sont ensuite utilisés pour découper une partie du super-réseau, laissant une structure en forme d'aileron. Les cristaux de super-réseau fournissent une structure de support solide pour les processus de développement ultérieurs.

Ensuite, un "faux" polysilicium est placé sur le super-réseau pour protéger le premier de la prochaine opération. Cette étape, connue sous le nom de processus double source/drain empilé verticalement, fait croître du silicium dopé au phosphore aux deux extrémités du nanoruban supérieur (futur site NMOS) tout en faisant croître sélectivement du silicium dopé sur le nanoruban inférieur (futur site PMOS silicium-germanium). Ensuite, un diélectrique est placé autour des sources d’énergie pour les isoler les unes des autres par décharge électrique.

L'empilement 3D double efficacement la densité des transistors CMOS par millimètre carré, la densité réelle dépendant de la complexité des cellules logiques impliquées.

Vient enfin la construction de la porte. Retirez d’abord la fausse porte précédemment installée pour exposer les nanorubans de silicium. Ensuite, seul le silicium-germanium est gravé, libérant un empilement de nanorubans de silicium parallèles, qui constitue la région du canal du transistor.

Ensuite, une très fine couche isolante est recouverte sur les quatre côtés du nanoruban. Cette couche isolante a une constante diélectrique élevée. Les canaux des nanorubans sont si petits qu'ils ne peuvent pas être recouverts chimiquement aussi efficacement que les transistors planaires.

Utilisez un métal pour entourer le nanoruban inférieur afin de former un canal dopé p, et le nanoruban supérieur forme un canal dopé n avec un autre nanoruban. De cette façon, la pile de grilles est construite et les deux transistors sont installés.

Ce processus peut paraître compliqué, mais il est meilleur qu'une autre technique (Sequential 3D Stacking). Si ce dernier est utilisé, le dispositif NMOS et le dispositif PMOS sont montés sur des tranches séparées, puis les deux sont réunis et la couche PMOS est transférée sur la tranche NMOS. La méthode d’empilement 3D auto-alignée comporte moins d’étapes de traitement et permet de contrôler plus strictement les coûts de fabrication.

Et plus important encore, cette méthode d'auto-alignement évite également les erreurs d'alignement pouvant survenir lors de la connexion de deux wafers. Établir toutes les connexions requises au CMOS empilé 3D est très difficile. Des connexions électriques seront requises à partir de la pile de périphériques ci-dessous. De par leur conception, le dispositif NMOS [en haut] et le dispositif PMOS [en bas] ont des contacts source/drain séparés, mais les deux appareils partagent une porte commune.

Il est à noter que l'espacement vertical entre NMOS et PMOS est à optimiser : s'il est trop court, cela augmentera la capacité parasite, s'il est trop long, cela augmentera la résistance de l'interconnexion entre les deux appareils. L’une ou l’autre situation extrême entraînera un ralentissement du circuit et consommera plus d’énergie.

De nombreuses études de conception, comme celle présentée par le centre de recherche américain TEL lors de la conférence IEDM 2021, proposent de fournir toutes les interconnexions nécessaires dans l'espace limité du CMOS 3D, sans augmenter significativement les unités logiques qu'elles constituent. La recherche montre qu'il existe de nombreuses possibilités d'innovation pour trouver les meilleures options d'interconnexion.

L'avenir de la loi de Moore

Avec les transistors à effet de champ en bande et le CMOS 3D, nous avons une voie claire pour prolonger la durée de vie de la loi de Moore, au moins jusqu'en 2024 et au-delà.

Dans une interview en 2005, Gordon Moore, le proposant de la loi de Moore, a admis que « je suis surpris de temps en temps par les progrès qui ont été réalisés ».

Il a déclaré : "Il y a eu des moments en cours de route où je pensais que nous avions atteint la fin, mais nos ingénieurs créatifs ont trouvé des moyens de surmonter les difficultés." est passé par FinFET, et avec une optimisation continue, est arrivé à l'ère RibbonFET, et a finalement évolué vers le processus CMOS empilé 3D. Nous prévoyons que la surprise laissée à M. Gordon Moore viendra bientôt.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Tendances technologiques à surveiller en 2023

- Comment l'intelligence artificielle apporte un nouveau travail quotidien aux équipes des centres de données

- L'intelligence artificielle ou l'automatisation peuvent-elles résoudre le problème de la faible efficacité énergétique des bâtiments ?

- Co-fondateur d'OpenAI interviewé par Huang Renxun : les capacités de raisonnement de GPT-4 n'ont pas encore atteint les attentes

- Bing de Microsoft surpasse Google en termes de trafic de recherche grâce à la technologie OpenAI