Maison >Périphériques technologiques >IA >La puce de supercalcul Tesla peut-elle surpasser le GPGPU ?

La puce de supercalcul Tesla peut-elle surpasser le GPGPU ?

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBavant

- 2023-04-12 22:43:011658parcourir

Auteur : Chen Wei, Ph.D., expert en stockage et architecture informatique/GPU et IA, titre professionnel senior. Zhongguancun Cloud Computing Industry Alliance, expert de la China Optical Engineering Society, membre de la Fédération internationale de l'informatique (ACM) et membre professionnel de la China Computer Federation (CCF). Il a déjà été scientifique en chef d'une société d'IA et responsable de la conception 3D NAND chez un important fabricant de puces mémoire. Ses principales réalisations incluent la première architecture nationale de produit de stockage et de processeur informatique reconfigurable de haute puissance (il a réalisé des tests internes de prototype dans un laboratoire). grand fabricant Internet), le premier processeur d'IA spécifique au domaine médical (déjà appliqué), le premier compilateur d'accélération d'IA compatible avec la plate-forme RISC-V/x86/ARM (déjà appliqué en coopération avec Alibaba Pingtouge/Xinlai), la première puce NAND 3D de Chine architecture et conception L'équipe a été créée (évaluée avec Samsung) et le premier compilateur de mémoire flash embarquée en Chine (évalué avec TSMC et a été appliqué au niveau de la plate-forme).

Le dernier jour de septembre 2022, Journée de l'intelligence artificielle de Tesla, le robot « Optimus Prime » de Tesla a officiellement fait ses débuts. Selon les ingénieurs de Tesla, la Journée de l'intelligence artificielle 2022 est la première fois que des robots Tesla sont « lancés » sans aucun support externe. "Il marchait dignement et saluait le public dans une direction générale. Hormis la légère lenteur des mouvements, tout le reste est très naturel.

1 La puissance du robot Tesla réside dans son « noyau interne » ?

Tesla présente une vidéo de robots « travaillant » dans le bureau. Un robot nommé Optimus Prime transportait des objets, arrosait des plantes et travaillait même de manière autonome dans une usine pendant un certain temps. "Notre objectif est de construire des robots humanoïdes utiles le plus rapidement possible", a déclaré Tesla, ajoutant que son objectif était de fabriquer des robots à moins de 20 000 dollars, soit moins cher que les voitures électriques de Tesla.

La raison pour laquelle les robots Tesla sont si puissants n'est pas seulement la propre accumulation de technologie d'IA par Tesla, mais aussi principalement en raison des puissantes puces d'IA développées par Tesla. Cette puce IA n'est pas un CPU traditionnel, encore moins un GPU. C'est une forme plus adaptée aux calculs d'IA complexes.

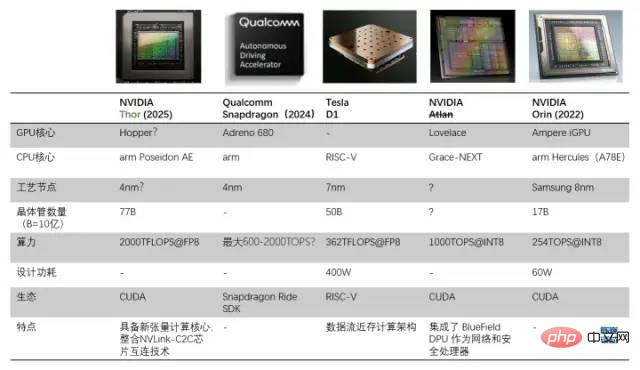

Comparaison entre le processeur D1 et d'autres processeurs de conduite/robot autonomes

1.1 Basé sur une architecture de flux de données proche de la mémoire pour créer une puce IA universelle qui surpasse le GPU

Tesla construit la sienne La raison pour la puce est que le GPU n'est pas spécifiquement conçu pour gérer la formation en apprentissage profond, ce qui rend le GPU relativement inefficace dans les tâches informatiques. L'objectif de Tesla et Dojo (Dojo est à la fois le nom du module de formation et le nom de l'architecture du noyau) est « d'obtenir les meilleures performances de formation en IA ». Permettre des modèles de réseaux neuronaux plus grands et plus complexes pour atteindre une efficacité énergétique et un coût élevés. " L'informatique. " La norme de Tesla est de construire un ordinateur qui est meilleur en matière d'intelligence artificielle que n'importe quel autre ordinateur afin qu'ils n'aient pas besoin d'utiliser un GPU à l'avenir.

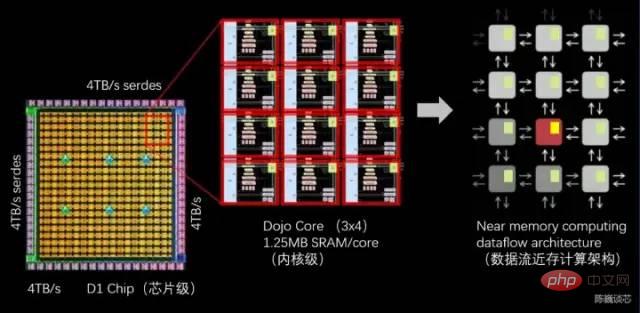

Un point clé dans la construction de superordinateurs est de savoir comment faire évoluer la puissance de calcul tout en maintenant une bande passante élevée (difficile) et une faible latence (très difficile). La solution proposée par Tesla est une architecture 2D distribuée (planaire) composée de puces puissantes et d'une structure de grille unique, ou une architecture informatique de flux de données proche de la mémoire.

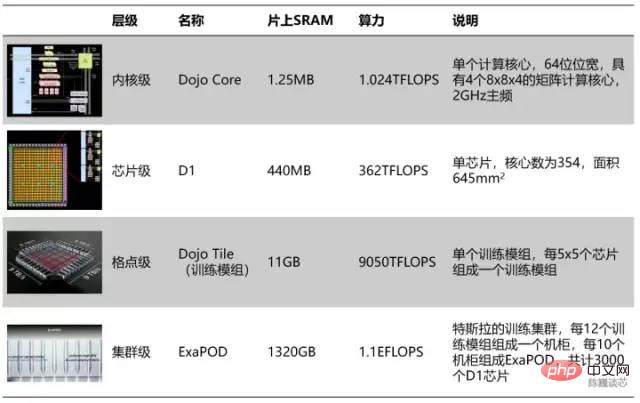

Division hiérarchique des unités de calcul Tesla

Selon la division hiérarchique, tous les 354 cœurs Dojo forment une puce D1 et tous les 25 puces forment un module de formation. Les 120 derniers modules de formation forment un ensemble de clusters informatiques ExaPOD, avec un total de 3 000 puces D1.

Un module de formation sur puce Tesla Dojo peut atteindre les performances de 6 groupes de serveurs GPU, mais le coût est inférieur à celui d'un seul groupe de serveurs GPU. La puissance de calcul d'un seul serveur Dojo a même atteint 54PFLOPS. Seules 4 armoires Dojo peuvent remplacer 72 racks GPU composés de 4 000 GPU. Dojo réduit le travail de calcul (formation) de l'IA qui prend normalement des mois à 1 semaine. Ce type de « grande puissance de calcul peut produire des miracles » est conforme au style de conduite autonome de Tesla. De toute évidence, la puce accélérera également considérablement les progrès de la technologie IA de Tesla.

Bien entendu, ce module à puce n'a pas encore atteint le niveau "parfait". Bien qu'il adopte l'idée du calcul de flux de données proche de la mémoire, son rapport puissance de calcul et efficacité énergétique ne dépasse pas celui du. GPU. Un seul serveur consomme énormément d’énergie, le courant pouvant atteindre 2 000 A, et nécessite une alimentation spécialement adaptée. La puce Tesla D1 constitue déjà la limite structurelle de l’architecture informatique quasi-mémoire. Si Tesla adopte une architecture « informatique en mémoire » ou « logique en mémoire », les performances de la puce ou le rapport d'efficacité énergétique seront peut-être considérablement améliorés.

Le serveur de puces Tesla Dojo se compose de 12 modules de formation Dojo (2 couches, 6 par couche) unité de calcul matricielle (8x8) et 1,25 Mo de SRAM locale. Cependant, la taille du cœur Dojo n'est pas grande. En comparaison, l'A64FX de Fujitsu occupe plus de deux fois la surface sur le même nœud de processus.

Réduction de la surface : Tesla intègre un grand nombre de cœurs de calcul dans la puce pour maximiser le débit de l'IA informatique, il est nécessaire de rendre la surface d'un cœur unique aussi petite que possible tout en garantissant la puissance de calcul, et de mieux compromettre la contradiction entre l'empilement de la puissance de calcul et le retard dans les systèmes de calcul intensif.

Caching et rationalisation de la latence : afin de maximiser son efficacité de calcul de zone, le noyau Dojo fonctionne à une fréquence relativement conservatrice de 2 GHz (les circuits d'horloge conservateurs ont tendance à occuper moins de surface), en utilisant uniquement un prédicteur de branche de base et de petites instructions de mise en cache, dans une architecture aussi rationalisée qui ne conserve que les composants nécessaires. La surface restante est laissée autant que possible aux unités de calcul vectoriel et de calcul matriciel. Bien entendu, si le programme du noyau a une empreinte de code importante ou comporte de nombreuses branches, cette stratégie peut sacrifier certaines performances.

Rationalisation des fonctionnalités : réduisez davantage la consommation d'énergie et de surface en supprimant les fonctionnalités du processeur qui ne sont pas nécessaires pour exécuter des calculs internes. Le cœur de Dojo n'effectue pas de mise en cache côté données, ne prend pas en charge la mémoire virtuelle et ne prend pas en charge les exceptions précises.

- Pour Tesla et Musk, Dojo n'est pas seulement façonné et aménagé comme un dojo, mais sa philosophie de conception est également étroitement liée à l'esprit du dojo, incarnant pleinement l'esthétique de conception du processeur « moins c'est plus ».

- 2 Le cœur D1 est-il une architecture RISC-V ? Jetons d’abord un coup d’œil à la structure et aux caractéristiques de chaque Dojo.

- Chaque cœur Dojo est un processeur doté de capacités de calcul vectoriel/calcul matriciel et possède des composants complets de récupération, de décodage et d'exécution d'instructions. Le cœur de Dojo a un style de type CPU qui semble être plus adaptable aux différents algorithmes et codes de branchement que le GPU. Le jeu d'instructions de D1 est similaire à RISC-V. Le processeur fonctionne à 2 GHz et dispose de quatre ensembles d'unités de calcul de multiplication matricielle 8x8. Il dispose également d'un ensemble d'instructions vectorielles personnalisées axées sur l'accélération des calculs d'IA.

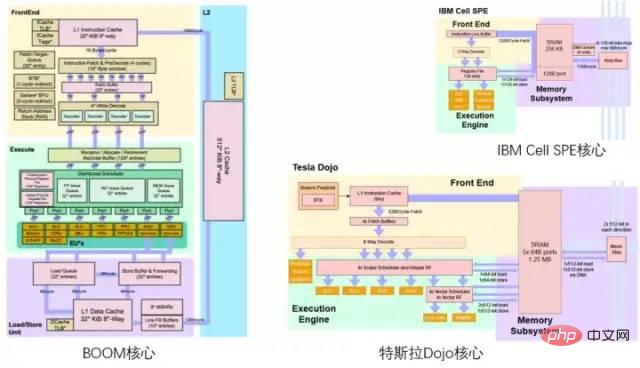

Ceux qui connaissent le domaine RISC-V peuvent probablement dire que la palette de couleurs du diagramme d'architecture Dojo de Tesla semble rendre hommage au diagramme d'architecture du processeur BOOM de Berkeley, avec du jaune en haut, du vert en bas et du violet en bas. le bas.

comparaison entre Tesla Dojo Core et Berkeley Boom / IBM Cell Core

2.1 D1 Core Global Architecture

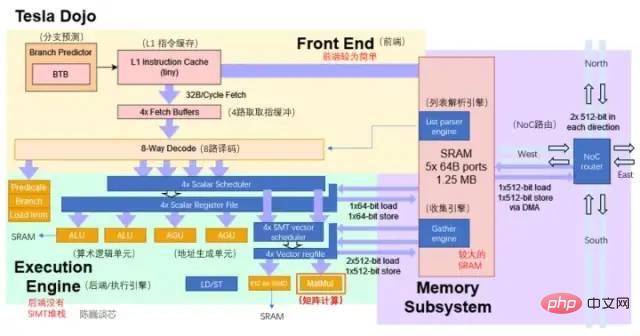

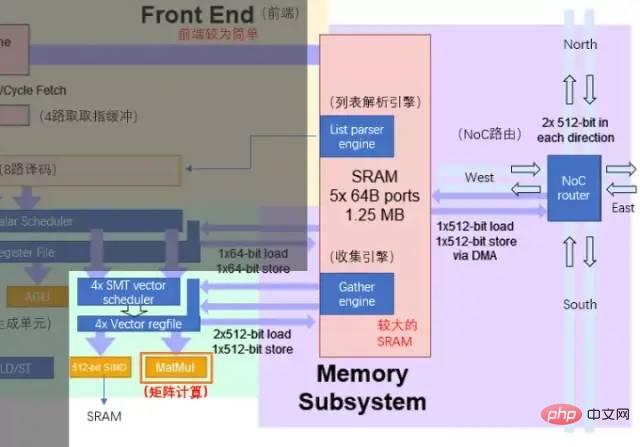

À en juger par le schéma d'architecture actuel, le noyau Dojo se compose de 4 parties : le frontal, l'unité d'exécution, le routage SRAM et NoC. Il a moins de composants de contrôle que le CPU et le GPU. Il possède un AGU de type CPU et. une idée de type GPU. L'unité de calcul matricielle du cœur Tensor.

La structure de base de Dojo est plus rationalisée que celle de BOOM. Elle ne dispose pas de composants tels que Rename pour améliorer l'utilisation des composants d'exécution, et il est également difficile de prendre en charge la mémoire virtuelle. Cependant, l'avantage de cette conception est qu'elle réduit la surface occupée par la partie contrôle et permet d'allouer plus de surface sur la puce à l'unité d'exécution des calculs. Chaque cœur Dojo fournit 1 024 TFLOPS de puissance de calcul. On constate que la quasi-totalité de la puissance de calcul de chaque unité est fournie par l'unité de calcul matricielle. Par conséquent, l'unité de calcul matricielle et la SRAM déterminent conjointement le rapport d'efficacité énergétique de calcul du processeur D1.

Paramètres principaux du noyau Dojo

BTB enregistre l'adresse de l'instruction de branchement réussie et son adresse cible de branchement dans un tampon. Le tampon est identifié par l'adresse de l'instruction de branchement. La dégradation des performances des branches dans les processeurs pipeline peut être réduite en prédisant le chemin de la branche et en mettant en cache les informations utilisées par la branche.

Lorsqu'un processeur ordinaire effectue diverses opérations, il doit calculer l'adresse mémoire requise pour récupérer les données de la mémoire (ou SRAM). Par exemple, l'emplacement mémoire d'un élément du tableau doit être calculé avant que le cœur du processeur puisse obtenir les données de l'emplacement mémoire réel. Ces calculs de génération d'adresses impliquent différentes opérations arithmétiques sur les nombres entiers telles que l'addition, la soustraction, l'arithmétique modulo ou le décalage de bits. Le calcul de l'adresse mémoire peut compiler plusieurs instructions machine générales, ou il peut être directement exécuté via le circuit matériel AGU comme Tesla Dojo. De cette manière, divers calculs de génération d'adresses peuvent être déchargés de l'ALU, réduisant ainsi le nombre de cycles CPU requis pour effectuer les calculs d'IA, améliorant ainsi les performances informatiques.

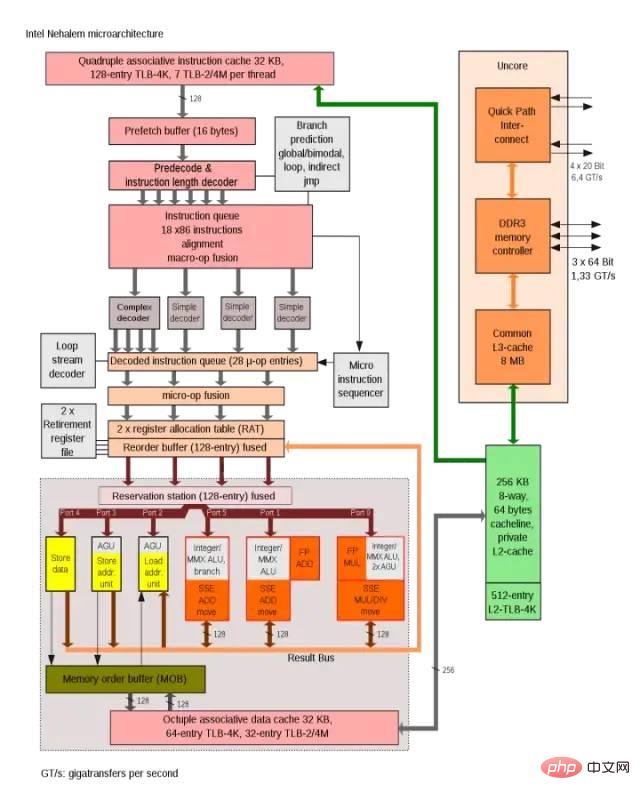

L'architecture Intel Nehalem utilise AGU pour améliorer l'efficacité de l'accès aux adresses à cycle unique

La méthode de connexion du cœur Dojo ressemble plus à la méthode de connexion du cœur SPE dans le processeur Cell d'IBM. Les principales similitudes incluent :

- Ni le code exécuté sur D1 ni sur SPE n'a d'accès direct à la mémoire système, les applications fonctionnent principalement dans la SRAM locale

- Si les données de la mémoire principale (DDR ou HBM) sont requises, les opérations DMA doivent être utilisé pour lire. Ni D1 ni le SPE de Cell ne prennent en charge la mémoire virtuelle.

- Ce qui suit présentera le stockage des modules et noyaux de calcul et de multiplication matricielle.

2.2 Unité de calcul matricielle de base et stockage sur puce

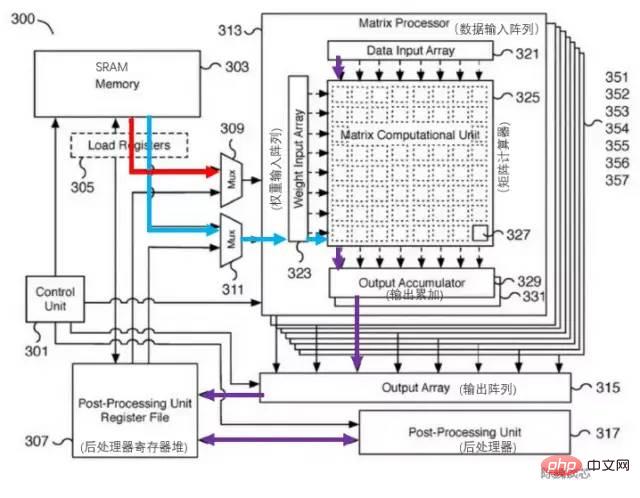

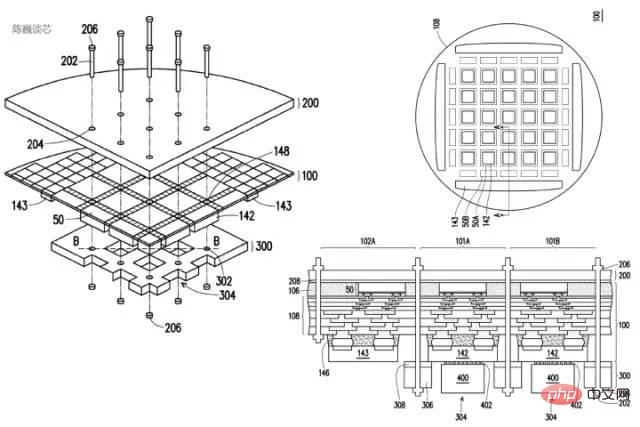

Le cœur de l'amélioration de la puissance de calcul de l'architecture Dojo est l'unité de calcul matricielle. L'interaction des données entre l'unité de calcul matricielle et la SRAM centrale constitue la principale consommation d'énergie du transfert de données centrales.Le brevet correspondant de l'unité de calcul matricielle Tesla est présenté ci-dessous. Le composant clé de ce module est une unité de multiplication matrice-matrice 8x8 (appelée calculatrice matricielle sur la figure). L'entrée est le tableau d'entrée de données et le tableau d'entrée de poids. Après avoir calculé la multiplication matricielle, la sortie est directement accumulée. Chaque noyau Dojo comprend des unités de multiplication matricielle 8x8 à 4 voies.

Brevet de l'unité de calcul matriciel Tesla

Brevet de l'unité de calcul matriciel Tesla

Comme il n'y a qu'un seul cache L1 et SRAM sur le schéma d'architecture, il est audacieux de supposer que Tesla a rationalisé la structure du cache de RISC-V afin d'économiser de la zone de cache et de réduire la latence. Le bloc SRAM de 1,25 Mo par cœur peut fournir 2 x 512 bits en lecture (correspondant au poids et aux données des calculs d'IA) et une bande passante d'écriture de 512 bits pour les unités SIMD et de calcul matriciel, ainsi que des capacités de lecture et d'écriture de 64 bits pour l'entier. enregistrer le fichier. Le principal flux de données de calcul va de la SRAM au SIMD et aux unités de multiplication matricielle.

Le flux de traitement principal de l'unité de calcul matriciel est le suivant :

charger les poids de la SRAM vers le tableau d'entrée de poids (matrice d'entrée de poids) via un multiplexeur (Mux), et charger les données de la SRAM vers le tableau d'entrée de données (entrée de données tableau).

Les données d'entrée et les poids sont multipliés dans la calculatrice matricielle (unité de calcul matricielle) (produit interne ou produit externe ?)

Les résultats du calcul de multiplication sont envoyés à l'accumulateur de sortie (accumulateur de sortie) pour accumulation. Lors du calcul ici, les calculs matriciels dépassant 8x8 peuvent être effectués par division matricielle et épissage.

La sortie accumulée est transmise au fichier de registre du post-processeur pour le cache, puis post-traitée (des opérations telles que l'activation, le pooling, le remplissage, etc. peuvent être effectuées).

L'ensemble du processus de calcul est directement contrôlé par l'unité de contrôle (Control unit) sans intervention du CPU.

Interaction des données entre l'unité d'exécution et SRAM/NoC

La SRAM au sein du cœur Dojo a une très grande bande passante de lecture et d'écriture et peut charger à 400 Go/s et charger à 270 Go/s. vitesse d'écriture. Le jeu d'instructions de base Dojo comporte des instructions de transfert réseau dédiées, acheminées via le NoC, qui peuvent déplacer des données directement vers ou depuis la mémoire SRAM d'autres cœurs de la puce D1 ou même dans le module de formation Dojo.

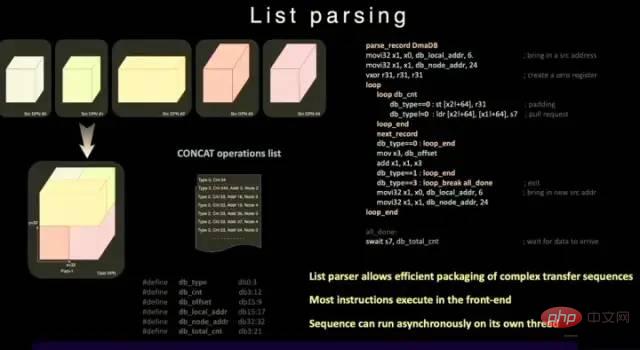

Différent de la SRAM ordinaire, la SRAM de Dojo comprend un moteur d'analyse de liste et un moteur de collecte. La fonction d'analyse de liste est l'une des fonctionnalités clés de la puce D1. Le moteur d'analyse de liste peut regrouper des séquences de transmission complexes de différents types de données pour améliorer l'efficacité de la transmission.

Fonction d'analyse de liste

Afin de réduire davantage le délai, la surface et la complexité des opérations, D1 ne prend pas en charge la mémoire virtuelle. Dans un processeur normal, l'adresse mémoire utilisée par le programme n'accède pas directement à l'adresse mémoire physique, mais est convertie en adresse physique par le processeur à l'aide de la structure de pagination définie par le système d'exploitation.

Dans le noyau D1, la fonction SMT à 4 voies permet un parallélisme explicite dans les calculs, simplifiant l'AGU et adressant les méthodes de calcul pour permettre à Tesla d'accéder à la SRAM avec une latence suffisamment faible. Son avantage est qu'elle peut éviter la mise en cache intermédiaire des données L1. latence.

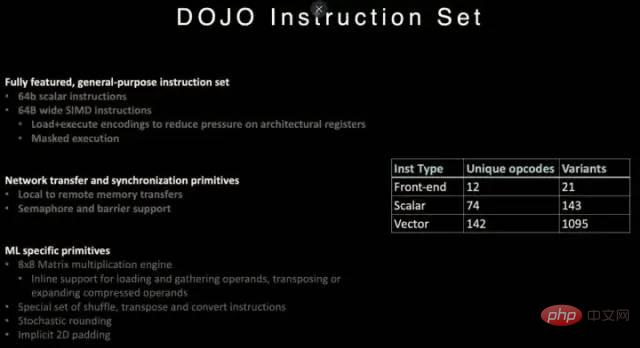

2.3 Jeu d'instructions Dojo

Jeu d'instructions du processeur D1

D1 fait référence aux instructions de l'architecture RISC-V et personnalise certaines instructions, notamment celles liées aux calculs vectoriels.

Le jeu d'instructions D1 prend en charge les instructions scalaires 64 bits et les instructions SIMD 64 octets, la transmission réseau avec primitives de synchronisation et primitives spécialisées liées à l'apprentissage automatique/apprentissage profond (telles que les calculs matriciels 8x8).

En termes de primitives de transmission et de synchronisation de données réseau, il prend en charge les primitives d'instructions (Primitives) pour transmettre des données du stockage local (SRAM) au stockage distant, ainsi que les sémaphores (Semaphore) et les contraintes de barrière (Contraintes de barrière). Cela permet à D1 de prendre en charge le multithreading et ses instructions d'opération de mémoire peuvent s'exécuter sur plusieurs cœurs D1.

Pour l'apprentissage automatique et l'apprentissage profond, Tesla a défini des instructions comprenant des opérations mathématiques telles que la lecture aléatoire, la transposition et la conversion, ainsi que des instructions liées à l'arrondi stochastique et au remplissage.

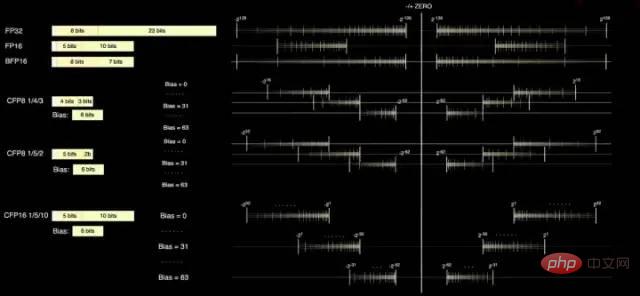

2.4 Format de données

Le noyau D1 dispose de deux formats de calcul standards, FP32 et FP16, et dispose également du format BFP16 qui est plus adapté à l'inférence. Afin d'améliorer les performances du calcul de précision mixte, D1 adopte également le format CFP8 8 bits pour une précision inférieure et un débit plus élevé.

L'avantage de l'utilisation de CFP8 est qu'il permet d'économiser plus d'espace multiplicateur pour atteindre presque la même puissance de calcul, ce qui est très utile pour augmenter la densité de puissance de calcul de D1.

Le compilateur Dojo peut glisser autour de la précision de la mantisse pour couvrir une plage et une précision plus larges. Jusqu'à 16 formats vectoriels différents peuvent être utilisés à tout moment, vous offrant ainsi la flexibilité nécessaire pour augmenter la puissance de calcul.

Format de données du processeur D1

Selon les informations fournies par Tesla, CFP8 peut être utilisé pour les calculs à l'intérieur de l'unité de multiplication matricielle (stockée au format CFP16).

3 Le processeur de l'architecture Dojo peut-il surpasser le GPU ?

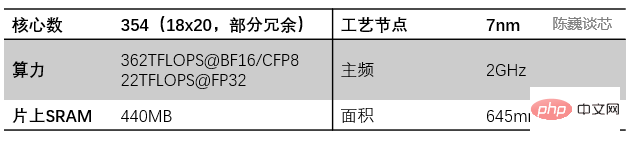

Le processeur D1 est fabriqué par TSMC et utilise un processus de fabrication de 7 nanomètres. Il possède 50 milliards de transistors et une surface de puce de 645 mm², ce qui est plus petit que l'A100 (826 mm²) de NVIDIA et l'AMD Arcturus (750 mm²). .

3.1 Architecture informatique proche de la mémoire du flux de données Dojo

Structure du processeur D1

Chaque processeur D1 est composé de 18 x 20 cœurs Dojo. Il y a 354 cœurs Dojo disponibles dans chaque processeur D1. (La raison pour laquelle seulement 354 des 360 cœurs sont utilisés est pour des raisons de rendement et de stabilité du cœur par processeur) Il est fabriqué par TSMC, en utilisant un processus de fabrication de 7 nm, avec 50 milliards de transistors et une surface de puce de 645 mm².

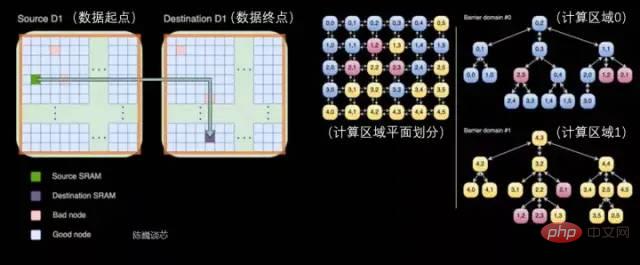

Chaque cœur Dojo dispose d'une SRAM de 1,25 Mo comme poids principal et stockage de données. Différents cœurs Dojo sont connectés via un routage réseau sur puce (routage NoC), et différents cœurs Dojo effectuent la synchronisation des données via des réseaux NoC complexes au lieu de partager des caches de données. Le NoC peut gérer 8 paquets dans 4 directions (sud-est, nord-ouest) à travers les limites des nœuds à 64 B/par cycle d'horloge dans chaque direction, c'est-à-dire une entrée de paquet et une sortie de paquet dans le maillage dans les quatre directions pour chaque cœur Dojo adjacent. Le routeur NoC peut également effectuer une lecture et une écriture bidirectionnelles de 64 B dans la SRAM au sein du cœur une fois par cycle.

Transmission entre processeurs et division des tâches au sein du processeur D1

Chaque cœur Dojo est un processeur relativement complet avec des capacités de calcul matriciel (car chaque cœur a une unité de calcul matricielle distincte, et le frontal est relativement petit, c'est pourquoi on l'appelle ici de type CPU). Son architecture de flux de données est quelque peu similaire à la structure de grille de flux de données bidimensionnelle de SambaNova. Les données circulent directement entre chaque cœur de traitement sans retourner à la mémoire.

La puce D1 fonctionne à 2 GHz et dispose d'une énorme SRAM de 440 Mo. Tesla concentre sa conception sur la SRAM distribuée dans la grille informatique, réduisant la fréquence d'accès à la mémoire grâce à un grand nombre de stockage sur puce plus rapides et plus proches et au transfert entre le stockage sur puce, améliorant ainsi les performances de l'ensemble du système, ce qui présente des caractéristiques évidentes de l'architecture intégrée de stockage et de calcul des flux de données (informatique proche de la mémoire des flux de données).

Chaque puce D1 dispose de 576 canaux SerDes bidirectionnels répartis autour d'elle et peut être connecté à d'autres puces D1 avec une bande passante unilatérale de 4 To/sec.

Principaux paramètres de la puce du processeur D1

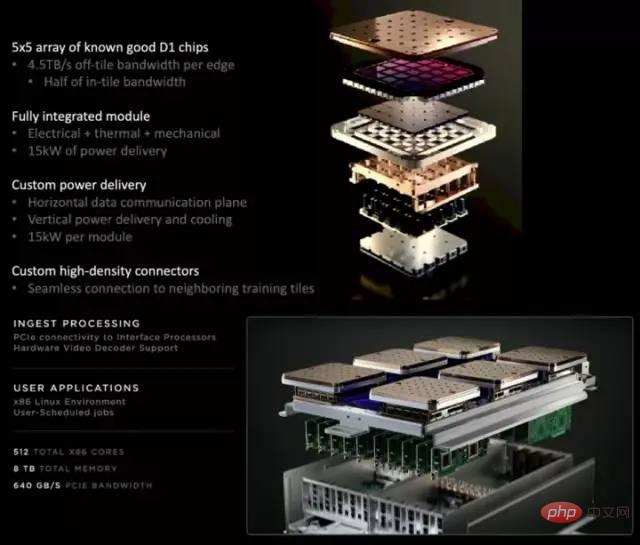

3.2 Technologie d'interconnexion d'emballage de chiplets du module de formation Dojo

Chaque module de formation D1 est organisé par un réseau de puces 5x5 D1 interconnectés en deux. Structure maillée dimensionnelle. La SRAM cross-core sur puce atteint un étonnant 11 Go, et bien sûr, la consommation électrique atteint également un étonnant 15 kW. Le ratio d'efficacité énergétique est de 0,6TFLOPS/W@BF16/CFP8. (J'espère que je l'ai mal calculé, sinon ce ratio d'efficacité énergétique n'est effectivement pas idéal). Mémoire HBM partagée externe de 32 Go. (HBM2e ou HBM3)

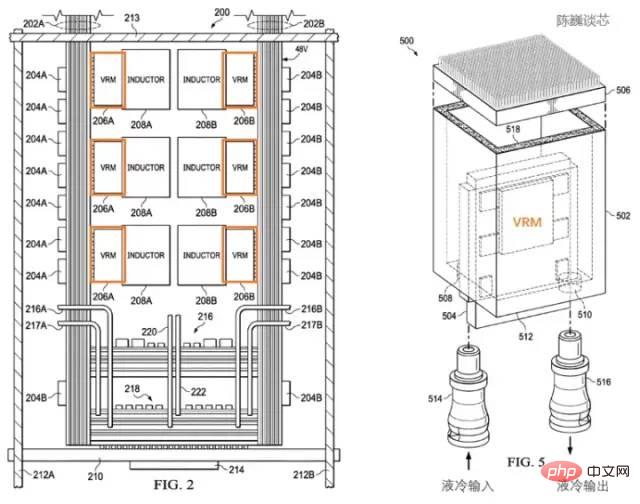

Structure de dissipation thermique brevetée du processeur Tesla D1

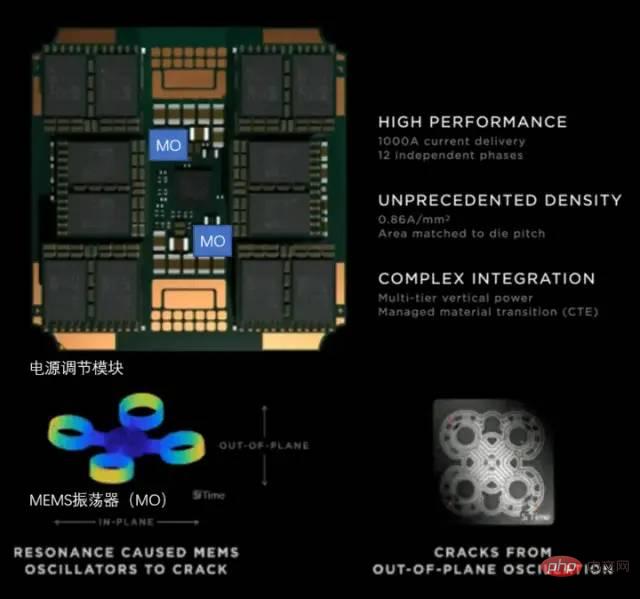

Tesla utilise un module de régulation de puissance (VRM) dédié et une structure de dissipation thermique pour gérer la consommation d'énergie. La gestion de l'énergie a ici deux objectifs principaux :

Réduire les pertes de puissance inutiles et améliorer le rapport d'efficacité énergétique.

Réduire les pannes du module processeur causées par la déformation thermique.

Selon le brevet de Tesla, nous pouvons voir que le module de régulation de puissance est perpendiculaire à la puce elle-même, ce qui réduit considérablement la surface occupée par le plan du processeur et peut rapidement équilibrer la température du processeur grâce au refroidissement liquide.

Dissipation thermique et structure d'emballage brevetées du processeur Tesla D1

Le module de formation utilise l'emballage InFO_SoW (Silicon on Wafer) pour augmenter la densité d'interconnexion entre les puces. En plus de la technologie INFO_SoW de TSMC, ce package utilise également la propre structure d'emballage mécanique de Tesla pour réduire les pannes du module processeur.

40 puces d'E/S situées sur le bord extérieur de chaque module de formation atteignent une bande passante globale de 36 To/s, ou une bande passante étendue de 10 To/s. Chaque couche de modules de formation est connectée à un système de stockage ultra-rapide : 640 Go de mémoire en cours d'exécution peuvent fournir plus de 18 To/s de bande passante, plus plus de 1 To/s de bande passante de commutation réseau.

La direction de transmission des données est parallèle au plan de la puce, et les directions d'alimentation et de refroidissement liquide sont perpendiculaires au plan de la puce. Il s'agit d'une très belle conception structurelle, et différents modules de formation peuvent être interconnectés. Grâce à la structure tridimensionnelle, la zone d'alimentation du module de puce est économisée et la distance entre les puces informatiques est réduite autant que possible.

Une armoire Dojo POD se compose de deux couches de plateaux informatiques et de systèmes de stockage. Chaque niveau de palette dispose de 6 modules de formation D1. Une armoire composée de 12 modules de formation répartis sur deux étages peut fournir 108PFLOPS de puissance de calcul de deep learning.

Module Dojo et armoire Dojo POD

3.3 Gestion de l'alimentation et contrôle de la dissipation thermique

La dissipation thermique des plates-formes de calcul intensif a toujours été une dimension importante pour mesurer le niveau des systèmes de calcul intensif.

Puissance de conception thermique de la puce D1

Tesla utilise un VRM (module de régulation de tension) entièrement développé sur le Dojo POD. Un seul VRM peut fournir une tension de 52 V et un courant énorme dépassant 1 000 A, l'objectif de courant est de 0,86. Un par millimètre carré, avec un total de 12 phases d'alimentation indépendantes.

Module de conditionnement d'énergie de Tesla

Pour la dissipation thermique des puces haute densité, l'accent est mis sur le contrôle du coefficient de dilatation thermique (CTE). La densité de puces du système Dojo est extrêmement élevée. Si le CTE est légèrement hors de contrôle, cela peut provoquer une déformation/défaillance structurelle, entraînant une défaillance de la connexion.

Le VRM développé par Tesla a itéré 14 versions au cours des 2 dernières années. Il utilise un oscillateur MEMS (MO) pour détecter la déformation thermique du module de régulation de puissance et répond enfin pleinement aux exigences internes des indicateurs CTE. Cette méthode de réglage actif de l'alimentation électrique via la technologie MEMS est similaire à la méthode de réglage actif de contrôle des vibrations du corps de la fusée.

3.4 Écologie de compilation du processeur d'architecture Dojo

Pile logicielle du processeur D1

Pour les puces IA telles que D1, l'écologie de compilation n'est pas moins importante que la puce elle-même.

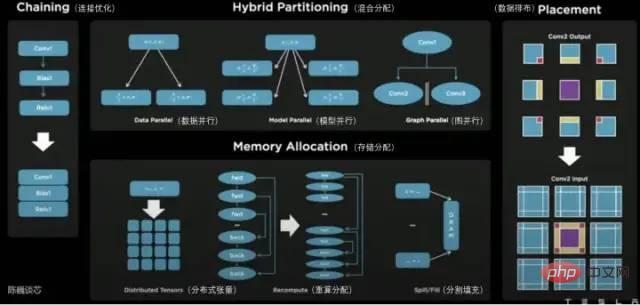

Sur le plan du processeur D1, D1 est divisé en unités de calcul matricielles. La chaîne d'outils de compilation est responsable de la division des tâches et de la configuration du stockage des données, et effectue un calcul parallèle précis de diverses manières et réduit l'utilisation du stockage.

Les méthodes parallèles prises en charge par le compilateur Dojo incluent le parallélisme des données, le parallélisme des modèles et le parallélisme des graphiques. Les méthodes d'allocation de stockage prises en charge incluent les tenseurs distribués, l'allocation recalculée et le remplissage fractionné.

Le compilateur lui-même peut gérer le flux de contrôle dynamique couramment utilisé dans divers processeurs, y compris les boucles et les algorithmes d'optimisation de graphiques. Avec le compilateur Dojo, les utilisateurs peuvent traiter les systèmes distribués à grande échelle Dojo comme un accélérateur pour la conception et la formation globales.

La couche supérieure de l'ensemble de l'écosystème logiciel est basée sur PyTorch, la couche inférieure est basée sur le pilote Dojo et le compilateur Dojo et LLVM sont utilisés au milieu pour former la couche de compilation. Après avoir ajouté LLVM ici, Tesla peut mieux utiliser les différents écosystèmes de compilation déjà sur LLVM pour l'optimisation de la compilation.

Tesla Dojo Compiler

4 Conclusion

Grâce à la Journée Tesla AI, nous avons vu le véritable corps du robot Tesla et son puissant "noyau interne" avec plus de conscience.

Le cœur Dojo de Tesla est différent des architectures CPU et GPU précédentes. On peut dire qu'il s'agit d'un GPU rationalisé qui combine les caractéristiques du CPU. Je pense que sa compilation sera également assez différente de celle du CPU et du GPU. Afin d'augmenter la densité de calcul, Tesla a procédé à des optimisations extrêmement rationalisées et fourni un mécanisme de gestion de l'énergie activement ajusté.

L'architecture du Tesla Dojo ne s'appelle pas seulement un dojo, mais sa conception est en effet basée sur la simplicité et le moins. Cette architecture deviendra-t-elle une autre forme typique d’architecture de puce informatique après le CPU et le GPU ? Attendons et voyons.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Tendances technologiques à surveiller en 2023

- Comment l'intelligence artificielle apporte un nouveau travail quotidien aux équipes des centres de données

- L'intelligence artificielle ou l'automatisation peuvent-elles résoudre le problème de la faible efficacité énergétique des bâtiments ?

- Co-fondateur d'OpenAI interviewé par Huang Renxun : les capacités de raisonnement de GPT-4 n'ont pas encore atteint les attentes

- Bing de Microsoft surpasse Google en termes de trafic de recherche grâce à la technologie OpenAI