Maison >outils de développement >VSCode >Comment configurer l'environnement Verilog dans VSCode ? Invites de code + instanciation automatique + partage de plug-in de formatage

Comment configurer l'environnement Verilog dans VSCode ? Invites de code + instanciation automatique + partage de plug-in de formatage

- 青灯夜游avant

- 2022-11-28 20:19:445227parcourir

VSCodeComment configurer l'environnement Verilog ? L'article suivant recommande trois plug-ins à tout le monde pour permettre à VSCode d'écrire Verilog en douceur. Les trois plug-ins peuvent réaliser des invites de code + une instanciation automatique + un formatage.

【Apprentissage recommandé : Tutoriel vscode, Vidéo de programmation】

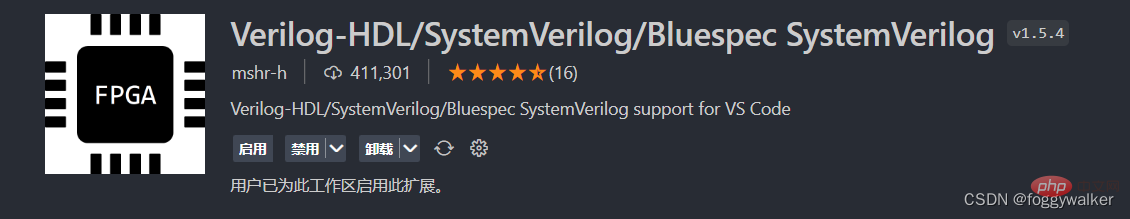

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

Fonctions réalisables :

- Grammaire Highlight

- Instanciation automatique

- Invites et sauts de code

- Complète automatique

Configuration du plug-in

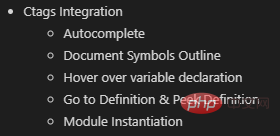

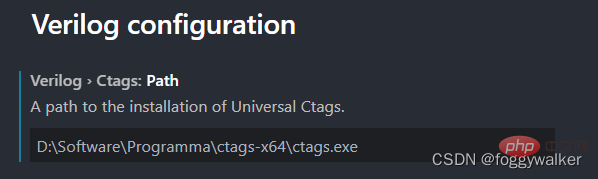

Comme expliqué sur la page d'accueil du plug-in Verilog HDL/SystemVerilog, la fonction Ctags est prise en charge :

Étapes de configuration :

Téléchargez la dernière version de ctags, certaines fonctions de l'ancienne version ne sont pas assez complètes ; Windows peut choisir la version x64

Définissez le chemin de ctags.exe dans l'environnement système ; variable ;

Paramètres du plug-in Configurez le chemin des ctags ;

Redémarrez simplement VSCode :

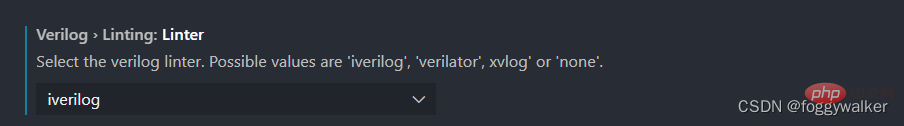

xvlog ( vivado)

xvlog ( vivado)

modelsim

Affichage des fonctions

- Prend en charge la coloration syntaxique telle que Verilog et SV.

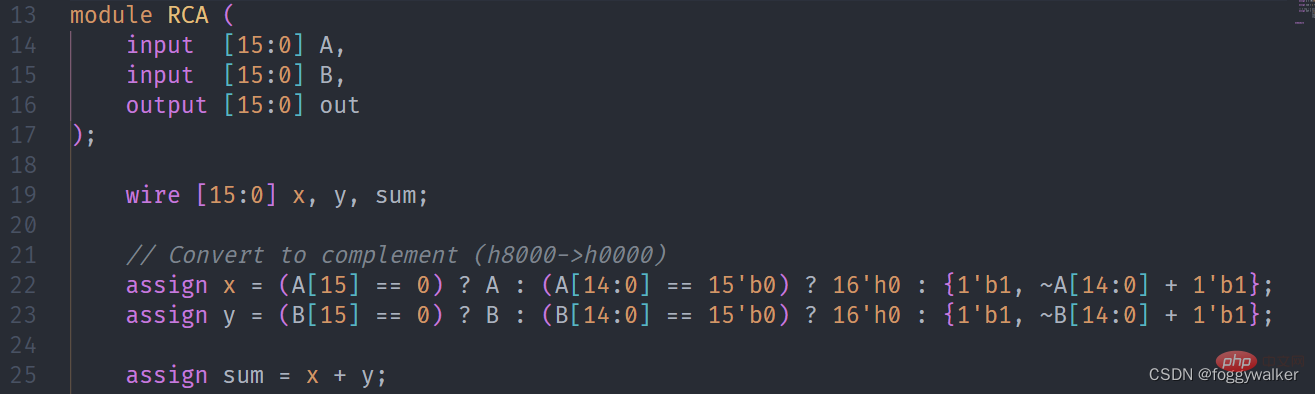

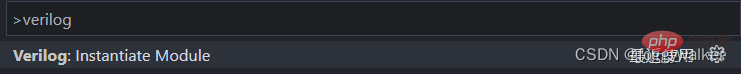

Shift+ctrl+p input verilog, vous pouvez directement instancier le module automatiquement. Placez la souris sur le signal et un relevé s'affichera dans la boîte flottante. Ctrl + clic gauche, cliquez sur le nom du signal pour accéder automatiquement à la déclaration. Placez le curseur sur le signal, cliquez avec le bouton droit et sélectionnez Afficher la définition (les touches de raccourci peuvent être liées par vous-même. Vous pouvez développer le code au niveau de la déclaration ici. Il est très pratique de modifier la déclaration sans avoir à faire des allers-retours). .

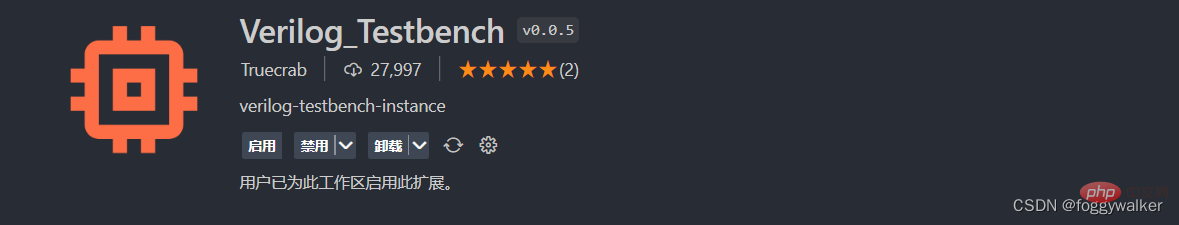

Verilog_Testbench

Fonctions réalisables :

Générer automatiquement le banc de test

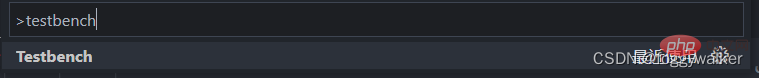

shift+ctrl+p pour entrer dans testben ch Générer directement tb. Copiez-le ensuite dans le terminal.

- SystemVerilog et Verilog Formatter

, et il prend également en charge un large éventail de paramètres de formatage personnalisés. Personnellement, je pense qu'il est plus facile à utiliser que le format Verilog. Les fonctions peuvent être réalisées. format : utilisation : bazel- bin/verilog/tools/formatter/verible-verilog-format [options]

Drapeaux de common/formatting/basic_format_style_init.cc :

--column_limit (Longueur de ligne cible à respecter lors du formatage.);

par défaut : 100;

--indentation_spaces (Chaque niveau d'indentation ajoute autant d'espaces.);

par défaut : 2;

--line_break_penalty (Pénalité ajoutée à la solution pour chaque ligne introduite

break.); par défaut : 2;

--over_column_limit_penalty (Pour la minimisation de la pénalité, cela représente la

valeur de pénalité de base en cas de dépassement de la limite de colonne. Une pénalité supplémentaire

de 1 est encourue pour chaque caractère dépassant cette limite) ; par défaut : 100;

--wrap_spaces (Chaque niveau d'indentation ajoute autant d'espaces. Cela s'applique lorsque le

premier élément après une section de groupe ouvert est enveloppé. Sinon, le niveau d'indentation

est défini sur la position de la colonne du groupe ouvert

opérateur.); par défaut : 4 ;

Flags from external/com_google_absl/absl/flags/parse.cc:

--flagfile (liste de fichiers séparés par des virgules à partir desquels charger les indicateurs) ; par défaut : ;

--fromenv (liste d'indicateurs séparés par des virgules à définir à partir de l'environnement [use

'export FLAGS_flag1=value']) ; par défaut : ;

--tryfromenv (liste d'indicateurs séparés par des virgules à essayer de définir à partir de l'environnement

s'il est présent) ; par défaut : ;

--undefok (liste de noms d'indicateurs séparés par des virgules qu'il est possible de spécifier sur

la ligne de commande même si le programme ne définit pas d'indicateur avec ce nom

); par défaut : ;

Indicateurs de verilog/formatting/format_style_init.cc :

--assignment_statement_alignment (Formater diverses affectations :

{align, flush-left, preserve, infer} ); par défaut : infer;

--case_items_alignment (Format des éléments de cas :

{align,flush-left,preserve,infer}) ; par défaut : infer;

--class_member_variable_alignment (Formater les variables des membres de la classe :

{align,flush-left,preserve,infer}) ; par défaut : infer ;

--compact_indexing_and_selections (Utiliser des expressions binaires compactes à l'intérieur de

opérateurs d'indexation/sélection de bits) ; par défaut : true ;

--distribution_items_alignment (Aligher les éléments de distribution :

{align,flush-left,preserve,infer}) ; par défaut : infer;

--enum_assignment_statement_alignment (Formater les affectations avec des énumérations :

{align,flush-left,preserve,infer}) ; par défaut : inférer;

--expand_coverpoints (Si vrai, développez toujours les points de couverture.); par défaut : false;

--formal_parameters_alignment (Format des paramètres formels :

{align,flush-left,preserve,infer}) ; par défaut : infer;

--formal_parameters_indentation (Indenter les paramètres formels : {indent,wrap});

par défaut : wrap;

--module_net_variable_alignment (Formater les déclarations nettes/variables :

{align,flush-left,preserve,infer}); par défaut : infer;

--named_parameter_alignment (Format des paramètres réels nommés :

{align,flush-left,preserve,infer}) ; par défaut : infer;

--named_parameter_indentation (Indenter les affectations de paramètres nommés :

{indent,wrap} ); par défaut : wrap;

--named_port_alignment (Format des connexions de port nommées :

{align,flush-left,preserve,infer}); par défaut : infer;

--named_port_indentation (Indenter les connexions de port nommées : {indent,wrap});

par défaut : wrap;

--port_declarations_alignment (Formater les déclarations de port :

{align,flush-left,preserve,infer}); par défaut : infer;

--port_declarations_indentation (Déclarations de port d'indentation : {indent,wrap});

par défaut: wrap;

--port_declarations_right_align_packed_dimensions (Si vrai, les dimensions emballées

dans les contextes avec l'alignement activé sont alignées à droite.);

par défaut : false;

--port_declarations_right_align_unpacked_dimensions (Si vrai, les dimensions décompressées

dans les contextes avec l'alignement activé sont alignées à droite.);

par défaut : false;

--struct_union_members_alignment (Format des membres de la structure/de l'union :

{align,flush- gauche, préserver, déduire}); par défaut : infer;

--try_wrap_long_lines (Si c'est vrai, laissez le formateur tenter d'optimiser les décisions d'encapsulation de ligne

là où l'encapsulation est nécessaire, sinon laissez-les non formatées.

Il s'agit d'une mesure à court terme visant à réduire le risque de préjudice.); par défaut : false ;

Indicateurs de verilog/parser/verilog_parser.cc :

--verilog_trace_parser (analyseur Trace Verilog) ; par défaut : faux ;

Indicateurs de verilog/tools/formatter/verilog_format.cc :

--failsafe_success (Si vrai, quittez toujours avec un statut 0, même s'il y avait

des erreurs de saisie ou des erreurs internes. Dans toutes les conditions d'erreur, le texte d'origine

est toujours préservé. Ceci est utile pour déployer des services où

les comportements de sécurité doivent être considérés comme un succès.) par défaut : true;

--inplace (Si vrai, écrasez le fichier d'entrée dans des conditions réussies.);

par défaut : false;

--lines (Lignes spécifiques à formater, basées sur 1, séparées par des virgules, plages N-M

inclusives , N est l'abréviation de N-N. Par défaut, non spécifié, toutes les lignes sont

activées pour le formatage (répétable, cumulatif) ; par défaut : ;

--max_search_states (limite le nombre d'états de recherche explorés lors de l'optimisation du bouclage de la ligne

.); par défaut : 100000;

--show_equally_optimal_wrappings (Si vrai, s'imprime lorsque plusieurs solutions optimales

sont trouvées (stderr), mais continuent de fonctionner normalement.);

par défaut : false;

--show_inter_token_info (Si vrai, avec show_token_partition_tree,

inclure des informations entre les jetons telles que l'espacement et les pénalités de rupture.) ; par défaut : 0;

--show_token_partition_tree (Si vrai, imprime les diagnostics après le partitionnement du jeton

, puis quittez sans formater la sortie.); par défaut : false;

--stdin_name (Lorsque vous utilisez '-' pour lire à partir de stdin, cela donne un nom alternatif

à des fins de diagnostic. Sinon, il est ignoré.);

par défaut : "

--verbose (Soyez plus verbeux.); par défaut : false;

--verify_convergence (Si vrai, et sans formatage incrémentiel avec

--lines, vérifiez que le reformatage de la sortie formatée ne produit aucun autre

changements, c'est-à-dire que le formatage est convergent.); par défaut : true ;

Essayez --helpfull pour obtenir une liste de tous les indicateurs ou --help=substring affiche l'aide pour

les indicateurs qui incluent la sous-chaîne spécifiée dans le nom, la description ou le

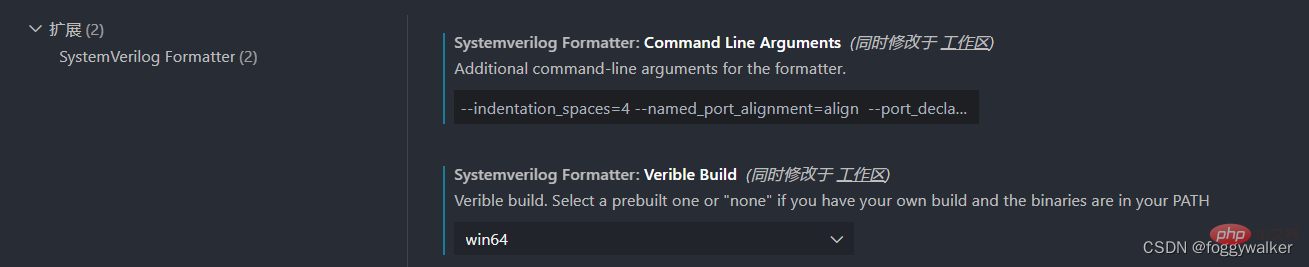

--indentation_spaces=4 --named_port_alignment=align --ort_declarations_alignment=align --module_net_variable_alignment=align如何使用?如何格式化?

和vscode内置格式化一样,直接shift+ctrl+f就可以格式化文件,ctrl+k可以格式化选定内容。

和vscode内置格式化一样,直接shift+ctrl+f就可以格式化文件,ctrl+k可以格式化选定内容。

比如,存在语法问题,或者不能识别语法的时候,格式化会使用不了。这里我"VSCode"

!Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Explication détaillée de la configuration : débogage à distance C++ dans vscode

- Cela vaut la peine de comprendre certaines opérations du curseur vscode pour rendre le développement aussi fluide que de la soie !

- Parlons de la façon dont ESLint et Prettier effectuent le formatage automatique du code dans vscode

- Comment vscode se connecte-t-il à un serveur distant ? (Tutoriel image et texte)

- Partage de plug-ins vscode : 5 plug-ins fonctionnels + 5 plug-ins de pêche