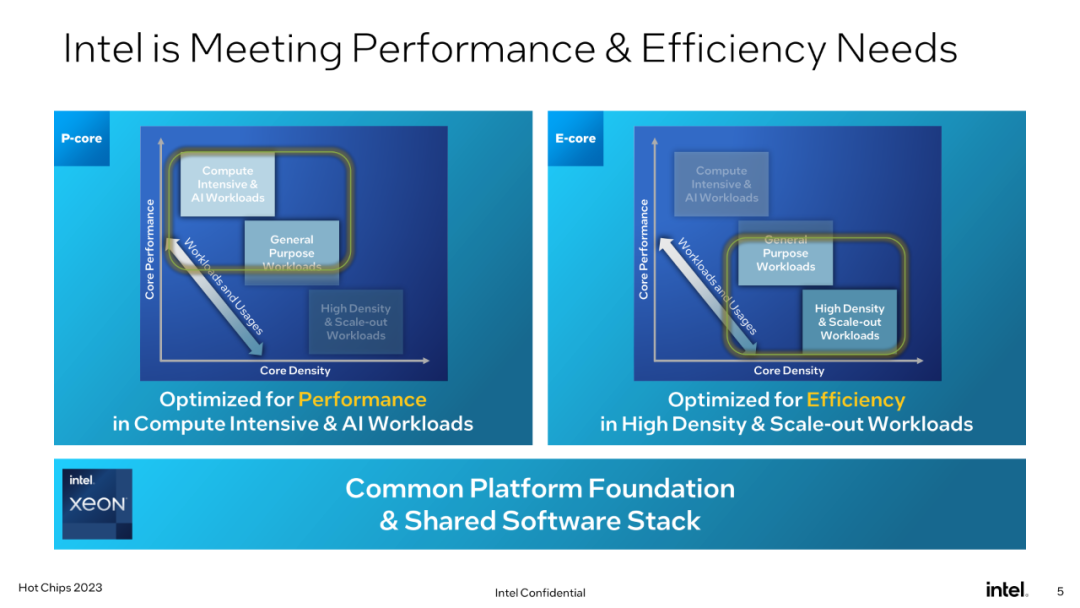

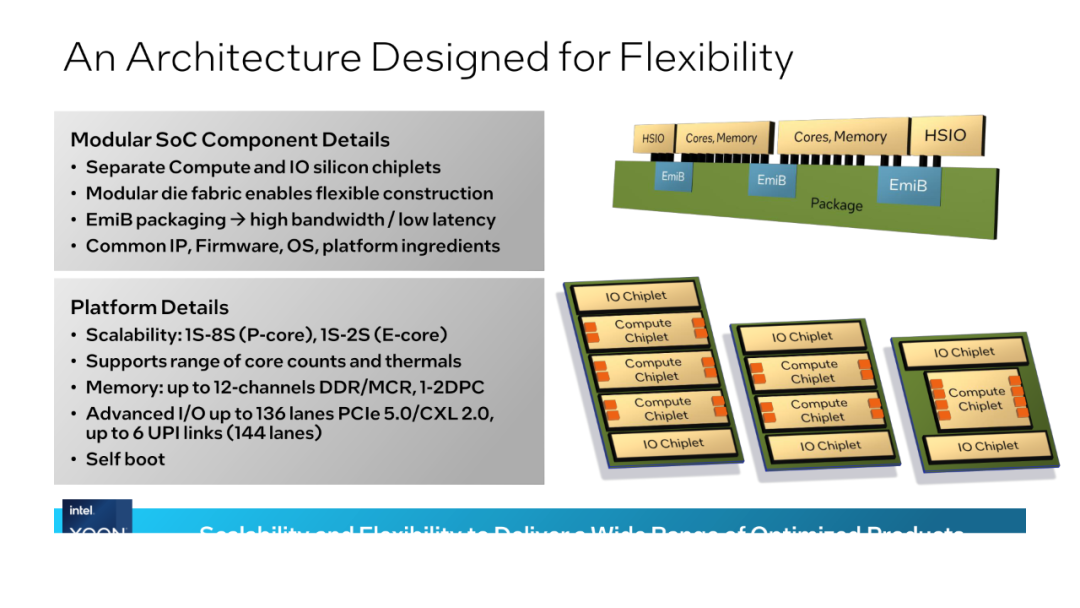

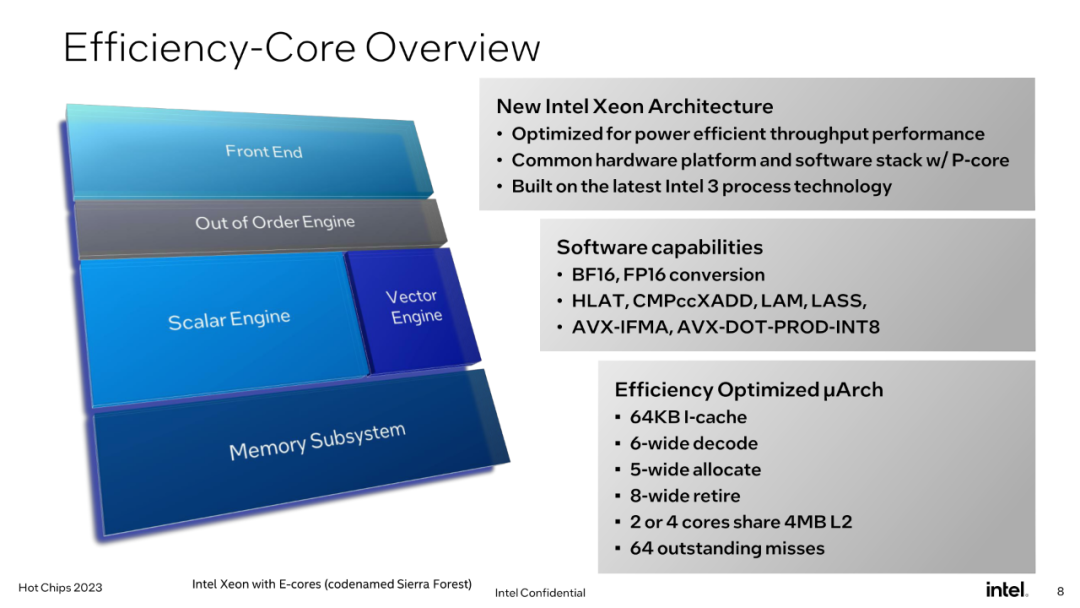

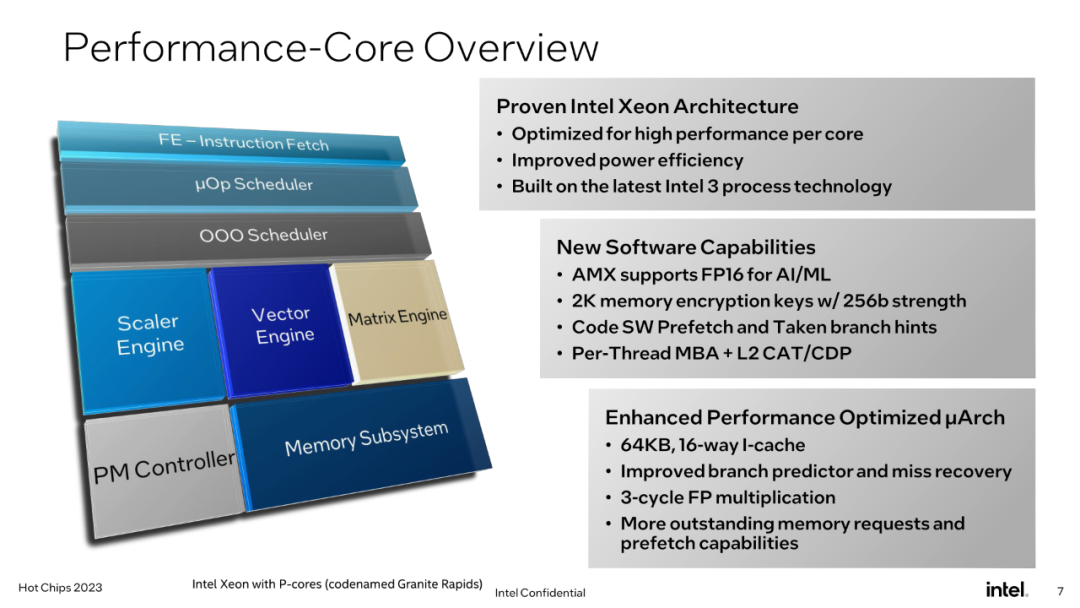

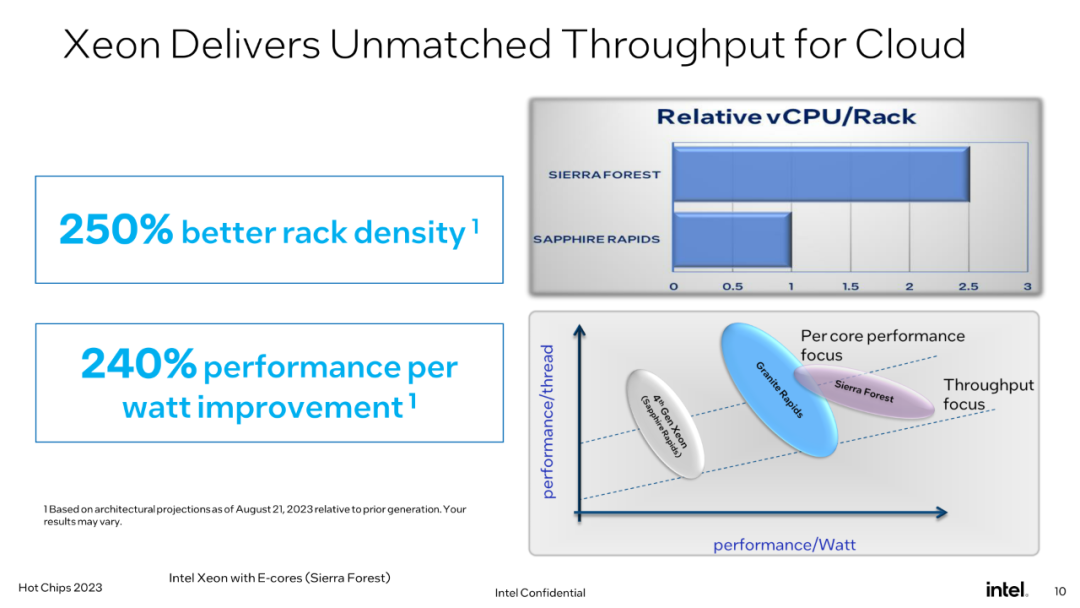

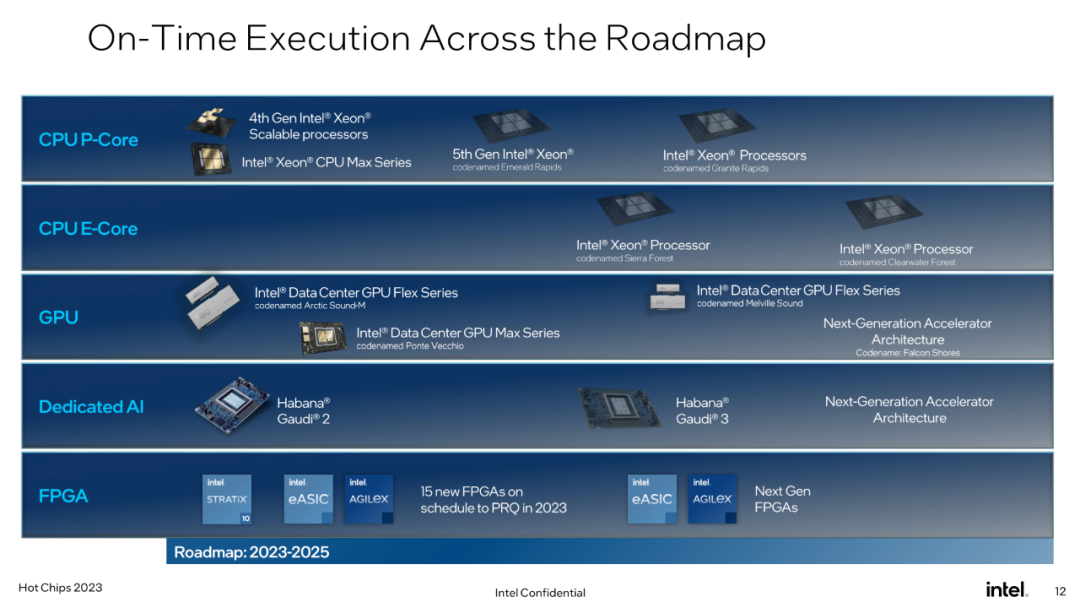

The next generation of Intel chips must have huge performance improvements. The annual Hot Chips is the most important technical conference in the semiconductor industry. Among them, experts in the chip field gather together, and global chip manufacturers often choose to release new products here or explain their future development directions. On Monday local time, at Hot Chips 2023 held at Stanford University, Intel revealed for the first time a new generation of data center chip "Sierra Forest", which has higher performance per watt than previous chips. Generation has increased by 240% and is expected to be launched next year. At the same time, Intel divided its data center chips into two categories for the first time: one is Granite Rapids, focusing on high energy consumption and high performance; the other is Sierra Forest, focusing on High energy efficiency. Let’s look at the specific details of the two data center chips, Granite Rapids and Sierra Forest. Overall, thanks to the introduction of area-efficient E cores (energy efficiency cores), Granite Rapids and Sierra Forest are expected to become Intel Xeon (Xeon) so far One of the most important updates in the scalable hardware ecosystem. Let’s first look at Sierra Forest, which is Intel’s first E-core Xeon scalable chip for data centers and the leading product of the EUV-based Intel 3 process. Intel said Sierra Forest is expected to be available in the first half of next year. Meanwhile, Granite Rapids also uses the same Intel 3 process. In terms of design, both Granite and Sierra are based on chiplet designs and rely on Intel EMIB (Embedded Multi-Die Interconnect Bridge, embedded multi-core interconnection Bridging) technology is a hybrid of computing and I/O chiplets packaged together. Not only that, this chiplet design is also unique, using different computing/IO chiplets instead of packaging "complete" Xeon chiplets together. This means that Granite and Sierra can share a general-purpose I/O chiplet built on the Intel 7 process. #In addition to sharing platform details, Intel also provided for the first time a high-level overview of the architecture used by the E-core and P-core (performance core). As is the case with multiple generations of Xeon now, Intel is leveraging the same basic CPU architecture as its consumer parts. Thus, Granite and Sierra can be thought of as deconstructed Meteor Lake processors, with Granite featuring Redwood Cove P cores and Sierra featuring Crestmont E cores. As mentioned before, this is Intel's first attempt at delivering E-cores to the Xeon market. For Intel, this means tailoring the E-Core design for data center workloads, a significant departure from the previous generation's consumer-focused E-Core designs. Intel revealed that Crestmont is offering a 6-wide instruction decode path as well as an 8-wide fallback backend. While not as powerful as Intel's P-Core, the E-Core is by no means a lightweight core, and Intel's design decisions reflect this. Still, its design is much more efficient than the P-cores in Granite, both in terms of chip space and power consumption. Crestmont’s L1 instruction cache (I-cache) will be 64KB, twice the size of the I-cache in earlier designs. Meanwhile, new members of the Crestmont E-core family can package those cores into 2- or 4-core clusters, unlike Gracemont, which currently only offers 4-core clusters. Finally, for Sierra/Crestmont, the chip will provide instructions as close as possible to Granite Rapids. This means there is BF16 data type support, as well as support for various instruction sets such as AVX-IFMA and AVX-DOT-PROD-INT8. Meanwhile for Granite Rapids, we have the Redwood Cove P core. Redwood/Granite is the legacy core of Xeon processors, and the changes aren't as drastic for Intel as Sierra Forest, but that doesn't mean they haven't improved. In terms of microarchitecture, Redwood Cove gets the same 64KB I-cache as Crestmont, which is 2x the capacity of its predecessor. But most notably, Intel managed to further reduce the latency of floating point multiplication, reducing it from 4/5 cycles to just 3 cycles. Basic instruction latency improvements like this are rare, so we always look forward to them. In addition to this, the Redwood Cove microarchitecture also has features such as branch prediction and prefetching, which are typical optimization goals for Intel. Anything they can do to improve branch prediction (and reduce the cost of rare mistakes) often pays relatively large dividends in terms of performance. Redwood Cove's AMX Matrix engine gets FP16 support, especially for the Xeon series, and FP16 isn't used as much as the already supported BF16 and INT8, but it's generally Improved AMX flexibility. Support for memory encryption is also being improved. Redwood Cove in Granite Rapids will support 2048 256-bit memory keys, while Sapphire Rapids will support 128 keys. While it’s too early to talk about individual SKUs for Granite Rapids and Sierra Forest, But Intel has clearly told us that core counts are increasing overall. The Granite Rapids chip will offer more CPU cores than the Sapphire Rapids (60 for the SPR XCC). Of course, Sierra's 144 cores will provide more CPU cores. Between previous Xeon delays and taking a long time to bring E-core Xeon scalable chips to market, Intel doesn't have as much of a presence in the data center market as it once did. Dominant position, so Granite Rapids and Sierra Forest will mark an important inflection point, pointing the way for the future development of Intel's data center products. We know that the data centers that power the Internet and online services host massive computing power requirements, and also consumes a lot of electricity. In recent years, with the development of technologies such as AI, technology companies are facing the challenge of increasing computing power and reducing energy consumption, which has prompted chip companies to focus on improving power consumption efficiency. Currently, Intel’s share in the data center chip market is being eroded step by step by competitors such as AMD and Ampere (a startup founded by former Intel executive Renee James). This year, Ampere and AMD have launched their own high-efficiency cloud computing chips, and Arm also proposed the Neoverse V2 platform at this Hot Chips 2023. As competition becomes increasingly fierce, it is inevitable that Intel will feel a sense of crisis. https://www.anandtech.com/show/20034/hot-chips-2023-intel-details -granite-rapids-and-sierra-forest-xeonshttps://www.reuters.com/technology/intel-says-new-sierra-forest-chip-more- than-double-power-efficiency-2023-08-28/The above is the detailed content of Intel launches next-generation data center CPU design: Chiplet design, performance increased by 240%. For more information, please follow other related articles on the PHP Chinese website!