Technologie-Peripheriegeräte

Technologie-Peripheriegeräte KI

KI Hier kommt die Lebensader des Transistors: 3D-Stacked-CMOS, wird Moores Gesetz noch weitere 10 Jahre gelten?

Hier kommt die Lebensader des Transistors: 3D-Stacked-CMOS, wird Moores Gesetz noch weitere 10 Jahre gelten?Hier kommt die Lebensader des Transistors: 3D-Stacked-CMOS, wird Moores Gesetz noch weitere 10 Jahre gelten?

Der Transistor gilt als „die größte Erfindung des 20. Jahrhunderts“.

Seine Entstehung legte den Grundstein für die Produktion von integrierten Schaltkreisen, Mikroprozessoren und Computerspeichern.

1965 wurde das „Mooresche Gesetz“ vorgeschlagen und wurde jahrzehntelang zur goldenen Regel der Halbleiterindustrie.

Es zeigt, dass sich alle 18 bis 24 Monate die Anzahl der auf einem Mikrochip verpackten Transistoren verdoppelt und sich auch die Leistung des Chips verdoppelt.

Mit der kontinuierlichen Einführung neuer Prozessknoten ist jedoch die Anzahl der Atome in Transistoren immer geringer geworden und verschiedene physikalische Grenzen schränken die Weiterentwicklung des Mooreschen Gesetzes ein.

Manche Leute denken sogar, dass Moores Gesetz vorbei ist.

Um das Mooresche Gesetz zu „retten“, müssen Ingenieure daher die Transistorstruktur ändern, die Fläche und den Stromverbrauch weiter reduzieren und seine Leistung verbessern.

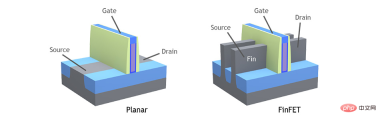

In der zweiten Hälfte des 20. Jahrhunderts war vor allem das Planartransistordesign (Planartransistor) beliebt. Zu Beginn der 2010er Jahre ersetzten 3D-finnenförmige Geräte nach und nach flache Designs.

Jetzt ist eine völlig neue Transistor-Designstruktur, der Gate All Around Transistor (GAA), der Nachfolger von FinFET und steht kurz vor der Produktionseinführung.

Aber wir müssen weiter schauen. Denn selbst mit dieser von Intel vorgeschlagenen neuen RibbonFET-Transistorarchitektur sind unsere Möglichkeiten zur Größenreduzierung begrenzt.

Glauben Sie, dass 3D-gestapelte komplementäre Metalloxidhalbleiter (CMOS) oder CFETs (komplementäre Feldeffekttransistoren) der Schlüssel zur Ausweitung des Mooreschen Gesetzes auf das nächste Jahrzehnt sein werden.

Die Entwicklung der Transistoren

Jeder Metalloxid-Halbleiter-Feldeffekttransistor (MOSFET) verfügt über die gleichen Grundkomponenten:

Gate-Stack, Kanalbereich (Kanalbereich), Source, Drain

Source und Drain sind chemisch dotiert, so dass sie entweder reich an beweglichen Elektronen sind (n-Typ) oder fehlen (p-Typ). Der Kanalbereich weist die entgegengesetzte Dotierung zu Source und Drain auf.

In der planaren Version des Transistors in fortschrittlichen Mikroprozessoren vor 2011 befand sich der Gate-Stapel des MOSFET knapp über dem Kanalbereich und wurde verwendet, um das elektrische Feld in den Kanalbereich zu projizieren.

Durch Anlegen einer ausreichend großen Spannung an das Gate (relativ zur Source) bildet sich im Kanalbereich eine Schicht mobiler Ladungsträger, die den Stromfluss zwischen Source und Drain ermöglicht.

Um die Größe des Planartransistordesigns zu reduzieren, ist ein „Kurzkanaleffekt“ in den Fokus der Physiker gerückt.

Da sich die Prozesstechnologie immer weiter verbessert, wird die Breite der Gate-Elektrode im Transistor immer kleiner. Sie wissen, wenn das Gate weniger als 20 nm dick ist, gerät der Strom außer Kontrolle und der Source-Strom durchdringt das Gate und erreicht direkt den Drain.

Zu diesem Zeitpunkt tritt ein „Leck“ auf, wodurch der Energieverbrauch des Chips stark ansteigt.

Um dieses Problem zu lösen, wird eine neue FinFET-Transistortechnologie vorgeschlagen. Es umschließt das Tor auf drei Seiten um einen Kanal, um eine bessere statische Kontrolle zu gewährleisten.

FinFET reduziert den Stromverbrauch um etwa 50 % bei gleichem Leistungsniveau wie die Planararchitektur der vorherigen Generation. FinFETs schalten außerdem schneller und sorgen für eine Leistungssteigerung von 37 %.

Im Jahr 2011 führte Intel FinFET auf dem von ihm eingeführten 22-nm-Knoten ein und verwendete es bei der Produktion seiner Core-Prozessoren der dritten Generation.

Seitdem ist FinFET zum Arbeitstier des Mooreschen Gesetzes geworden.

Allerdings haben wir durch den Umstieg auf FinFET auch etwas verloren.

Bei planaren Geräten wird die Breite des Transistors durch Fotolithographie definiert, es handelt sich also um einen äußerst flexiblen Parameter.

Aber bei FinFET erfolgt die Transistorbreite in diskreten Schritten, wobei jeweils eine Finne hinzugefügt wird. Diese Eigenschaft wird oft als Fin-Quantisierung bezeichnet.

Trotz der Flexibilität von FinFETs bleibt die Fin-Quantisierung eine wichtige Designbeschränkung. Die damit verbundenen Designregeln und der Wunsch, mehr Finnen hinzuzufügen, um die Leistung zu verbessern, vergrößern die Gesamtfläche der Logikzelle und verkomplizieren den Verbindungsstapel, der einen einzelnen Transistor in eine vollständige Logikschaltung verwandelt.

Außerdem erhöht es die Kapazität des Transistors und verringert dadurch seine Schaltgeschwindigkeit. Während FinFET uns als Arbeitspferd der Branche gute Dienste geleistet hat, ist ein neuer, verfeinerterer Ansatz erforderlich.

Dieser Ansatz führte dazu, dass Physiker den kommenden 3D-Transistor – RibbonFET – erfanden.

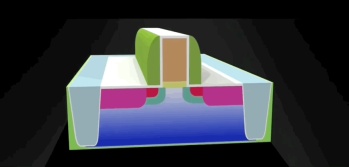

Beim RibbonFET umgibt das Gate den Transistorkanalbereich, um die Kontrolle der Ladungsträger zu verbessern. Die neue Struktur ermöglicht außerdem eine bessere Leistung und eine verfeinerte Optimierung.

Konkret umgibt das Gate die Kanäle vollständig und ermöglicht so eine strengere Kontrolle über die Ladungsträger innerhalb der Kanäle, die nun aus nanoskaligen Siliziumbändern bestehen.

Mit diesen Nanoribbons (Nanosheets) ist es wieder möglich, die Breite des Transistors mittels Fotolithographie beliebig zu verändern.

Nach dem Entfernen der Quantisierungsbeschränkungen ist es möglich, eine entsprechend große Breite für die Anwendung zu generieren. Dadurch können wir Leistung, Leistung und Kosten in Einklang bringen.

Noch wichtiger ist, dass Geräte durch Stapeln und Parallelbetrieb mehr Strom liefern und die Leistung verbessern können, ohne die Fläche zu vergrößern.

Daher ist Intel davon überzeugt, dass RibbonFET die beste Wahl ist, um eine höhere Leistung bei angemessener Leistung zu erzielen.

Sie werden die RibbonFET-Struktur im Intel 20A-Prozess im Jahr 2024 einführen.

3D-Stacked-CMOS

Planar-, FinFET- und RibbonFET-Transistoren haben gemeinsam, dass sie alle CMOS-Technologie verwenden. Wie bereits erwähnt, besteht CMOS aus n-Typ- und p-Typ-Transistoren . Diese Technologie wurde in den 1980er Jahren zum Mainstream, da sie viel weniger Strom verbraucht als andere Alternativen. Weniger Strom bedeutet höhere Betriebsfrequenzen und eine höhere Transistordichte.

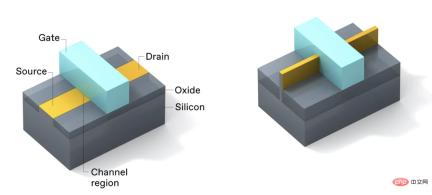

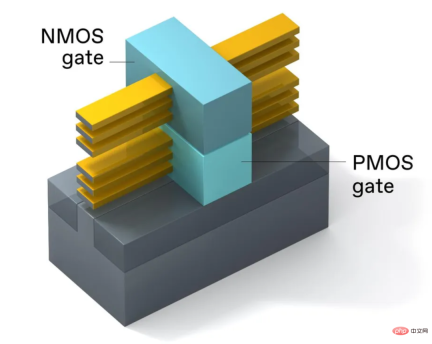

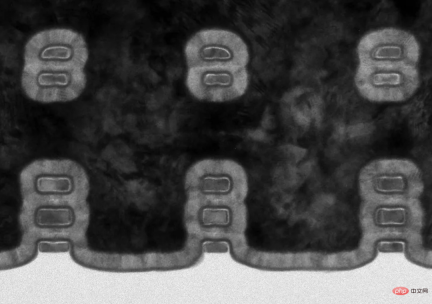

Bisher wurden bei allen CMOS-Technologien Standardpaare von NMOS- und PMOS-Transistoren nebeneinander platziert. In der Grundsatzrede der IEEE International Electronic Components Conference (IEDM) 2019 wurde jedoch ein Konzept von „3D-gestapelten“ Transistoren vorgeschlagen, bei dem NMOS-Transistoren auf PMOS-Transistoren platziert werden.

Auf der IDM 2020 wurde der erste Wechselrichter vorgestellt, der mithilfe von Logikschaltungen mithilfe dieser 3D-Technologie entwickelt wurde. 3D-Stacked-CMOS reduziert den Platzbedarf des Wechselrichters effektiv um die Hälfte, verdoppelt die Transistorflächendichte und verschiebt die Grenzen des Mooreschen Gesetzes weiter.

3D-Stapel-CMOS-Struktur, bei der das PMOS-Gerät auf dem NMOS-Gerät platziert wird, mit einer Gesamtfläche, die der einer RibbonFET-Fläche entspricht. NMOS- und PMOS-Gates verwenden unterschiedliche Metallmaterialien

Um 3D-Stack-CMOS zu nutzen, müssen viele Herausforderungen bei der Prozessintegration gelöst werden, von denen einige die Grenzen der CMOS-Verarbeitung und -Herstellung betreffen.

Wie erreicht man es? Die Herstellung selbstausrichtender 3D-CMOS beginnt mit Siliziumwafern. Auf dem Wafer tragen wir Schicht für Schicht Silizium und Siliziumgermanium auf, eine Struktur, die „Supergitter“ genannt wird. Mithilfe fotolithografischer Muster wird dann ein Teil des Übergitters weggeschnitten, sodass eine flossenartige Struktur zurückbleibt. Übergitterkristalle bieten eine starke Stützstruktur für nachfolgende Entwicklungsprozesse.

Als nächstes wird ein „falsches“ Polysilizium auf das Übergitter gelegt, um ersteres vor der nächsten Operation zu schützen. Bei diesem Schritt, der als vertikal gestapelter Dual-Source/Drain-Prozess bekannt ist, wird an beiden Enden des oberen Nanobands (zukünftige NMOS-Stelle) phosphordotiertes Silizium gezüchtet, während auf dem unteren Nanoband (zukünftige PMOS-Stelle) selektiv dotiertes Silizium gezüchtet wird. Anschließend wird ein Dielektrikum um die Stromquellen gelegt, um diese durch elektrische Entladung voneinander zu isolieren.

3D-Stacking verdoppelt effektiv die CMOS-Transistordichte pro Quadratmillimeter, wobei die tatsächliche Dichte von der Komplexität der beteiligten Logikzellen abhängt.

Schließlich kommt der Bau der Tür. Entfernen Sie zunächst die zuvor installierte Scheintür, um die Silizium-Nanobänder freizulegen. Als nächstes wird nur das Siliziumgermanium weggeätzt, wodurch ein Stapel paralleler Silizium-Nanobänder freigesetzt wird, der den Kanalbereich des Transistors darstellt.

Dann wird auf allen vier Seiten des Nanobandes eine sehr dünne Isolierschicht aufgetragen. Diese Isolierschicht hat eine hohe Dielektrizitätskonstante. Nanobandkanäle sind so klein, dass sie nicht so effizient chemisch beschichtet werden können wie Planartransistoren.

Verwenden Sie ein Metall, um das untere Nanoband zu umgeben, um einen p-dotierten Kanal zu bilden, und das obere Nanoband bildet mit einem anderen Nanoband einen n-dotierten Kanal. Auf diese Weise wird der Gate-Stack aufgebaut und die beiden Transistoren eingebaut.

Dieser Prozess sieht vielleicht kompliziert aus, ist aber besser als eine andere Technik (Sequentielles 3D-Stacking). Wenn letzteres verwendet wird, werden das NMOS-Bauelement und das PMOS-Bauelement auf separaten Wafern montiert, und dann werden die beiden zusammengebracht und die PMOS-Schicht auf den NMOS-Wafer übertragen. Die selbstausrichtende 3D-Stapelmethode erfordert weniger Verarbeitungsschritte und kann die Herstellungskosten strenger kontrollieren.

Und was noch wichtiger ist: Diese Selbstausrichtungsmethode vermeidet auch Ausrichtungsfehler, die beim Verbinden zweier Wafer auftreten können. Die Herstellung aller erforderlichen Verbindungen zu 3D-Stacked-CMOS ist eine große Herausforderung. Stromanschlüsse werden vom Gerätestapel unten benötigt. Das NMOS-Gerät [oben] und das PMOS-Gerät [unten] verfügen konstruktionsbedingt über separate Source-/Drain-Kontakte, aber beide Geräte teilen sich ein gemeinsames Gate.

Es ist erwähnenswert, dass der vertikale Abstand zwischen NMOS und PMOS optimiert werden muss: Wenn er zu kurz ist, erhöht er die parasitäre Kapazität, wenn er zu lang ist, erhöht er den Widerstand der Verbindung zwischen den beiden Geräten. Beide Extremsituationen führen dazu, dass der Stromkreis langsamer wird und mehr Strom verbraucht.

Viele Designstudien, wie die vom American TEL Research Center auf der IEDM 2021-Konferenz vorgestellte, schlagen vor, alle notwendigen Verbindungen innerhalb des begrenzten Raums von 3D-CMOS bereitzustellen, ohne die Fläche der Logikeinheiten, aus denen sie bestehen, wesentlich zu vergrößern. Die Untersuchung zeigt, dass es bei der Suche nach den besten Verbindungsoptionen viele Möglichkeiten für Innovationen gibt.

Die Zukunft des Mooreschen Gesetzes

Mit Streifen-Feldeffekttransistoren und 3D-CMOS haben wir einen klaren Weg, die Lebensdauer des Mooreschen Gesetzes zu verlängern, mindestens bis 2024 und darüber hinaus.

In einem Interview im Jahr 2005 gab Gordon Moore, der Befürworter des Mooreschen Gesetzes, zu: „Ich bin von Zeit zu Zeit von den erzielten Fortschritten überrascht.“

Er sagte: „Es gab Zeiten auf dem Weg, in denen ich dachte, wir hätten das Ende erreicht, aber unsere kreativen Ingenieure fanden Wege, um die Schwierigkeiten zu überwinden.“ durchlief FinFET und gelangte mit kontinuierlicher Optimierung zur RibbonFET-Ära und schließlich zum 3D-Stacked-CMOS-Prozess. Wir gehen davon aus, dass die Überraschung, die Herrn Gordon Moore hinterlassen wurde, bald kommen wird.

Das obige ist der detaillierte Inhalt vonHier kommt die Lebensader des Transistors: 3D-Stacked-CMOS, wird Moores Gesetz noch weitere 10 Jahre gelten?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

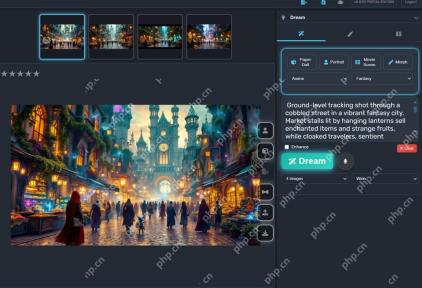

Die KI -Spielentwicklung tritt mit dem Dreamer -Portal von Upheaval in seine agentenische Ära einMay 02, 2025 am 11:17 AM

Die KI -Spielentwicklung tritt mit dem Dreamer -Portal von Upheaval in seine agentenische Ära einMay 02, 2025 am 11:17 AMUmwälzungsspiele: Revolutionierung der Spielentwicklung mit KI -Agenten Upprudaval, ein Studio für Spieleentwicklung, das aus Veteranen von Branchengiganten wie Blizzard und Obsidian besteht

Uber will dein Robotaxi -Shop sein. Werden Anbieter sie lassen?May 02, 2025 am 11:16 AM

Uber will dein Robotaxi -Shop sein. Werden Anbieter sie lassen?May 02, 2025 am 11:16 AMDie Robotaxi-Strategie von Uber: Ein Fahrwerk Ökosystem für autonome Fahrzeuge Auf der jüngsten Curbivore-Konferenz stellte Richard Willder von Uber ihre Strategie vor, die Robotaxi-Anbieter zu werden. Nutzung ihrer dominanten Position in

KI -Agenten, die Videospiele spielen, werden zukünftige Roboter verändernMay 02, 2025 am 11:15 AM

KI -Agenten, die Videospiele spielen, werden zukünftige Roboter verändernMay 02, 2025 am 11:15 AMVideospiele erweisen sich als unschätzbare Testgründe für die modernste KI-Forschung, insbesondere bei der Entwicklung autonomer Agenten und realer Roboter, die möglicherweise sogar zum Streben nach künstlicher allgemeiner Intelligenz (AGI) beitragen. A

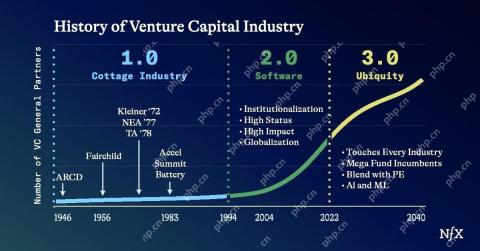

Der Startup Industrial Complex, VC 3.0 und James Curriers ManifestoMay 02, 2025 am 11:14 AM

Der Startup Industrial Complex, VC 3.0 und James Curriers ManifestoMay 02, 2025 am 11:14 AMDie Auswirkungen der sich entwickelnden Risikokapitallandschaft sind in Medien, Finanzberichten und alltäglichen Gesprächen offensichtlich. Die spezifischen Konsequenzen für Anleger, Startups und Mittel werden jedoch häufig übersehen. Risikokapital 3.0: ein Paradigma

Adobe Updates Creative Cloud und Firefly bei Adobe Max London 2025May 02, 2025 am 11:13 AM

Adobe Updates Creative Cloud und Firefly bei Adobe Max London 2025May 02, 2025 am 11:13 AMAdobe Max London 2025 lieferte erhebliche Aktualisierungen für Creative Cloud und Firefly, was eine strategische Verlagerung in Richtung Zugänglichkeit und generativer KI widerspiegelt. Diese Analyse enthält Erkenntnisse aus Briefings vor der Ereignis mit Adobe Leadership. (Hinweis: Adob

Alles, was Meta in Lamacon angekündigt hatMay 02, 2025 am 11:12 AM

Alles, was Meta in Lamacon angekündigt hatMay 02, 2025 am 11:12 AMDie Lamacon-Ankündigungen von Meta zeigen eine umfassende KI-Strategie, die direkt mit geschlossenen KI-Systemen wie OpenAIs konkurrieren und gleichzeitig neue Einnahmequellen für seine Open-Source-Modelle erstellt. Dieser vielfältige Ansatz zielt auf BO ab

Die Brau -Kontroverse über den Vorschlag, dass KI nichts anderes ist als nur normale TechnologieMay 02, 2025 am 11:10 AM

Die Brau -Kontroverse über den Vorschlag, dass KI nichts anderes ist als nur normale TechnologieMay 02, 2025 am 11:10 AMEs gibt schwerwiegende Unterschiede im Bereich der künstlichen Intelligenz zu dieser Schlussfolgerung. Einige bestehen darauf, dass es Zeit ist, die "neuen Kleidung des Kaisers" aufzudecken, während andere der Idee, dass künstliche Intelligenz nur gewöhnliche Technologie ist, stark aussieht. Lassen Sie uns darüber diskutieren. Eine Analyse dieses innovativen KI -Durchbruchs ist Teil meiner laufenden Forbes -Spalte, die die neuesten Fortschritte im Bereich der KI abdeckt, einschließlich der Identifizierung und Erklärung einer Vielzahl einflussreicher KI -Komplexitäten (klicken Sie hier, um den Link anzuzeigen). Künstliche Intelligenz als gemeinsame Technologie Erstens sind einige Grundkenntnisse erforderlich, um die Grundlage für diese wichtige Diskussion zu schaffen. Derzeit gibt es eine große Menge an Forschungen, die sich zur Weiterentwicklung künstlicher Intelligenz widmen. Das Gesamtziel ist es, künstliche allgemeine Intelligenz (AGI) und sogar mögliche künstliche Super Intelligence (AS) zu erreichen

Model -Bürger, warum KI -Wert der nächste Business -Maßstab istMay 02, 2025 am 11:09 AM

Model -Bürger, warum KI -Wert der nächste Business -Maßstab istMay 02, 2025 am 11:09 AMDie Effektivität des KI -Modells eines Unternehmens ist jetzt ein wichtiger Leistungsindikator. Seit dem KI -Boom wurde generative KI für alles verwendet, vom Komponieren von Geburtstagseinladungen bis zum Schreiben von Softwarecode. Dies hat zu einer Verbreitung von Sprachmod geführt

Heiße KI -Werkzeuge

Undresser.AI Undress

KI-gestützte App zum Erstellen realistischer Aktfotos

AI Clothes Remover

Online-KI-Tool zum Entfernen von Kleidung aus Fotos.

Undress AI Tool

Ausziehbilder kostenlos

Clothoff.io

KI-Kleiderentferner

Video Face Swap

Tauschen Sie Gesichter in jedem Video mühelos mit unserem völlig kostenlosen KI-Gesichtstausch-Tool aus!

Heißer Artikel

Heiße Werkzeuge

SecLists

SecLists ist der ultimative Begleiter für Sicherheitstester. Dabei handelt es sich um eine Sammlung verschiedener Arten von Listen, die häufig bei Sicherheitsbewertungen verwendet werden, an einem Ort. SecLists trägt dazu bei, Sicherheitstests effizienter und produktiver zu gestalten, indem es bequem alle Listen bereitstellt, die ein Sicherheitstester benötigen könnte. Zu den Listentypen gehören Benutzernamen, Passwörter, URLs, Fuzzing-Payloads, Muster für vertrauliche Daten, Web-Shells und mehr. Der Tester kann dieses Repository einfach auf einen neuen Testcomputer übertragen und hat dann Zugriff auf alle Arten von Listen, die er benötigt.

Notepad++7.3.1

Einfach zu bedienender und kostenloser Code-Editor

DVWA

Damn Vulnerable Web App (DVWA) ist eine PHP/MySQL-Webanwendung, die sehr anfällig ist. Seine Hauptziele bestehen darin, Sicherheitsexperten dabei zu helfen, ihre Fähigkeiten und Tools in einem rechtlichen Umfeld zu testen, Webentwicklern dabei zu helfen, den Prozess der Sicherung von Webanwendungen besser zu verstehen, und Lehrern/Schülern dabei zu helfen, in einer Unterrichtsumgebung Webanwendungen zu lehren/lernen Sicherheit. Das Ziel von DVWA besteht darin, einige der häufigsten Web-Schwachstellen über eine einfache und unkomplizierte Benutzeroberfläche mit unterschiedlichen Schwierigkeitsgraden zu üben. Bitte beachten Sie, dass diese Software

Dreamweaver CS6

Visuelle Webentwicklungstools

MinGW – Minimalistisches GNU für Windows

Dieses Projekt wird derzeit auf osdn.net/projects/mingw migriert. Sie können uns dort weiterhin folgen. MinGW: Eine native Windows-Portierung der GNU Compiler Collection (GCC), frei verteilbare Importbibliotheken und Header-Dateien zum Erstellen nativer Windows-Anwendungen, einschließlich Erweiterungen der MSVC-Laufzeit zur Unterstützung der C99-Funktionalität. Die gesamte MinGW-Software kann auf 64-Bit-Windows-Plattformen ausgeführt werden.