Heim >Technologie-Peripheriegeräte >KI >Erstmaliges Training von BERT und ResNet auf einem Smartphone, wodurch der Energieverbrauch um 35 % gesenkt wird

Erstmaliges Training von BERT und ResNet auf einem Smartphone, wodurch der Energieverbrauch um 35 % gesenkt wird

- 王林nach vorne

- 2023-04-09 11:41:061935Durchsuche

Die Forscher sagten, dass sie Edge-Training als Optimierungsproblem betrachteten und so den optimalen Zeitplan entdeckten, um bei einem gegebenen Speicherbudget einen minimalen Energieverbrauch zu erreichen.

Derzeit werden Deep-Learning-Modelle häufig auf Edge-Geräten wie Smartphones und eingebetteten Plattformen für Inferenzen eingesetzt. Unter ihnen wird das Training immer noch hauptsächlich auf großen Cloud-Servern mit Hochdurchsatzbeschleunigern wie GPUs durchgeführt. Zentralisierte Cloud-Trainingsmodelle erfordern die Übertragung sensibler Daten wie Fotos und Tastatureingaben von Edge-Geräten in die Cloud, was die Privatsphäre der Benutzer opfert und zusätzliche Kosten für die Datenverschiebung verursacht.

Bildunterschrift: Twitter @Shishir Patil

Damit Benutzer ihre Modelle personalisieren können, ohne die Privatsphäre zu beeinträchtigen, erfordern gerätebasierte Trainingsmethoden wie föderiertes Lernen keine Integration von Daten in die Cloud, It Es ist auch möglich, lokale Trainingsaktualisierungen durchzuführen. Diese Methoden wurden auf der Gboard-Tastatur von Google eingesetzt, um Tastaturvorschläge zu personalisieren, und werden auch von iPhones verwendet, um die automatische Spracherkennung zu verbessern. Gleichzeitig unterstützen aktuelle gerätebasierte Trainingsmethoden das Training moderner Architekturen und großer Modelle nicht. Das Training größerer Modelle auf Edge-Geräten ist nicht möglich, vor allem weil der begrenzte Gerätespeicher keine Backpropagation-Aktivierungen speichern kann. Eine einzelne Trainingsiteration von ResNet-50 erfordert über 200-mal mehr Speicher als Inferenz.

Zu den in früheren Arbeiten vorgeschlagenen Strategien gehören das Auslagern in den Hilfsspeicher und die Neuimplementierung, um den Speicherbedarf des Cloud-Trainings zu reduzieren. Allerdings erhöhen diese Methoden den Gesamtenergieverbrauch erheblich. Mit Paging-Methoden verbundene Datenübertragungen erfordern im Allgemeinen mehr Energie als umfangreiche Datenberechnungen. Wenn das Speicherbudget schrumpft, erhöht die Neuimplementierung den Energieverbrauch um O(n^2).

In einem aktuellen Artikel der UC Berkeley haben mehrere Forscher gezeigt, dass Paging und Neuimplementierung sich in hohem Maße ergänzen. Durch die Neuimplementierung einfacher Vorgänge und das Auslagern der Ergebnisse komplexer Vorgänge auf Sekundärspeicher wie Flash- oder SD-Karten können sie die effektive Speicherkapazität bei minimalem Energieverbrauch erweitern. Darüber hinaus haben die Forscher durch die Kombination dieser beiden Methoden auch bewiesen, dass es möglich ist, Modelle wie BERT auf mobilen Edge-Geräten zu trainieren. Indem sie Edge-Training als Optimierungsproblem betrachteten, entdeckten sie den optimalen Zeitplan, der bei einem gegebenen Speicherbudget einen minimalen Energieverbrauch erreicht.

- Papieradresse: https://arxiv.org/pdf/2207.07697.pdf

- Projekthomepage: https://poet.cs.berkeley.edu/

- GitHub-Adresse: https://github. com/shishirpatil/poet

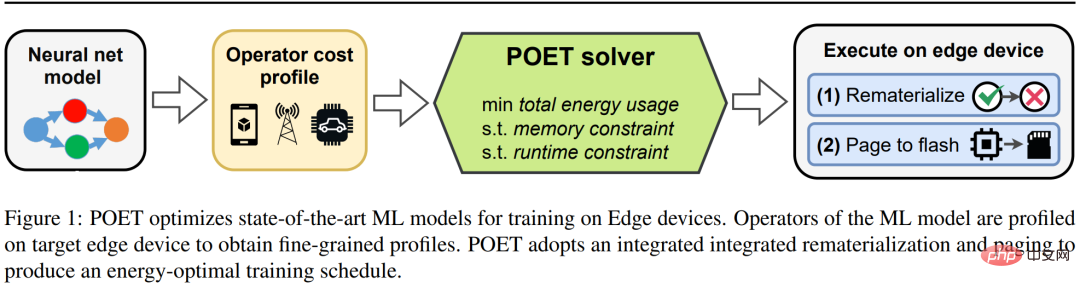

Die Forscher schlugen POET (Private Optimal Energy Training) vor, einen Algorithmus für das energieoptimale Training moderner neuronaler Netze auf speicherbegrenzten Edge-Geräten. Seine Architektur ist in Abbildung 1 dargestellt . Angesichts der extrem hohen Kosten für das Zwischenspeichern aller Aktivierungstensoren für die Backpropagation optimiert POET das Paging und die Neuimplementierung von Aktivierungen und reduziert so den Speicherverbrauch um bis zu den Faktor zwei. Sie formulierten das marginale Trainingsproblem als ganzzahlige lineare Programmierung (ILP) um und stellten fest, dass es von einem Löser in 10 Minuten optimal gelöst werden konnte.

Bildunterschrift: POET optimiert das Training von SOTA-Modellen für maschinelles Lernen auf Edge-Geräten.

Bei Modellen, die auf realen Edge-Geräten bereitgestellt werden, erfolgt das Training, wenn das Edge-Gerät im Leerlauf zu sein scheint und Zyklen berechnen kann, wie z. B. Google Gboard, das Modellaktualisierungen plant, während das Telefon aufgeladen wird. Daher enthält POET auch strenge Trainingsbeschränkungen. Angesichts der Speicherbeschränkungen und der Anzahl der Trainingsepochen generiert POET Lösungen, die auch die vorgegebene Trainingsfrist einhalten. Darüber hinaus entwickelten die Forscher mithilfe von POET ein umfassendes Kostenmodell und zeigten, dass es mathematisch werterhaltend ist (d. h. keine Näherungen vornimmt) und mit bestehenden Out-of-the-Box-Architekturen funktioniert.

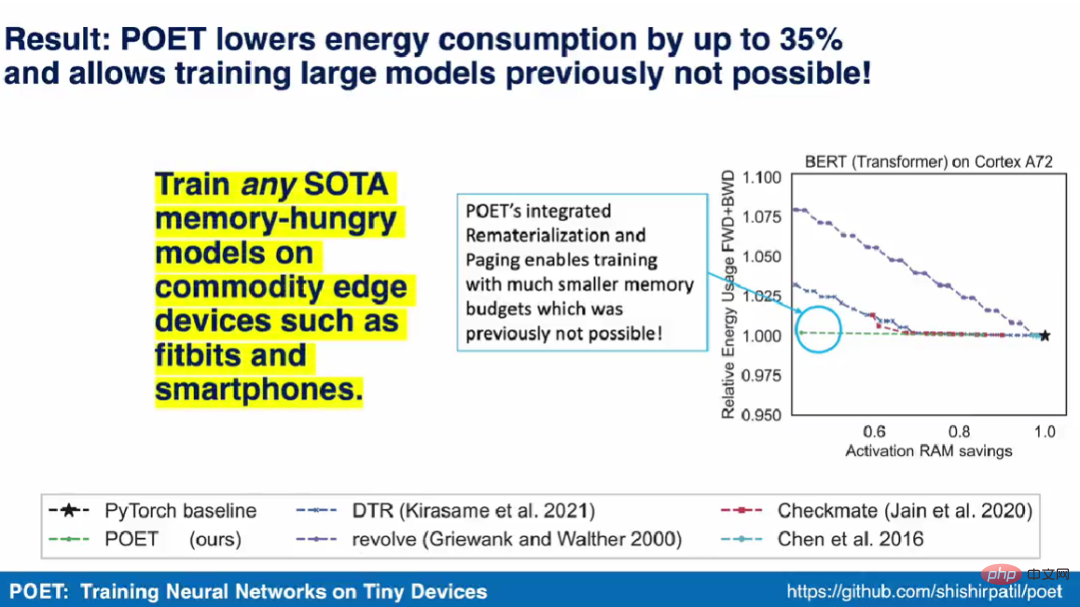

Shishir Patil, der Erstautor des Papiers, sagte im Demonstrationsvideo, dass der POET-Algorithmus jedes SOTA-Modell trainieren kann, das großen Speicher auf kommerziellen Edge-Geräten wie Smartphones benötigt. Sie waren auch das erste Forschungsteam, das das Training von SOTA-Modellen für maschinelles Lernen wie BERT und ResNet auf Smartphones und ARM Cortex-M-Geräten demonstrierte.

Integriertes Paging und Neuimplementierung

Neuimplementierung und Paging sind zwei Techniken, um den Speicherverbrauch großer SOTA ML-Modelle zu reduzieren. Bei Neuimplementierungen werden Aktivierungstensoren gelöscht, sobald sie nicht mehr benötigt werden, am häufigsten während des Vorwärtsdurchlaufs. Dadurch wird wertvoller Speicher frei, der zum Speichern von Aktivierungen für nachfolgende Ebenen verwendet werden kann. Wenn der gelöschte Tensor erneut benötigt wird, berechnet die Methode ihn anhand anderer verwandter Aktivierungen neu, wie durch die Abstammung angegeben. Paging, auch Offloading genannt, ist eine ergänzende Technik zur Speicherreduzierung. Beim Paging werden Aktivierungstensoren, die nicht unmittelbar benötigt werden, vom Primärspeicher zum Sekundärspeicher, beispielsweise einem Flash-Speicher oder einer SD-Karte, abgerufen. Wenn der Tensor erneut benötigt wird, blättern Sie ihn aus.

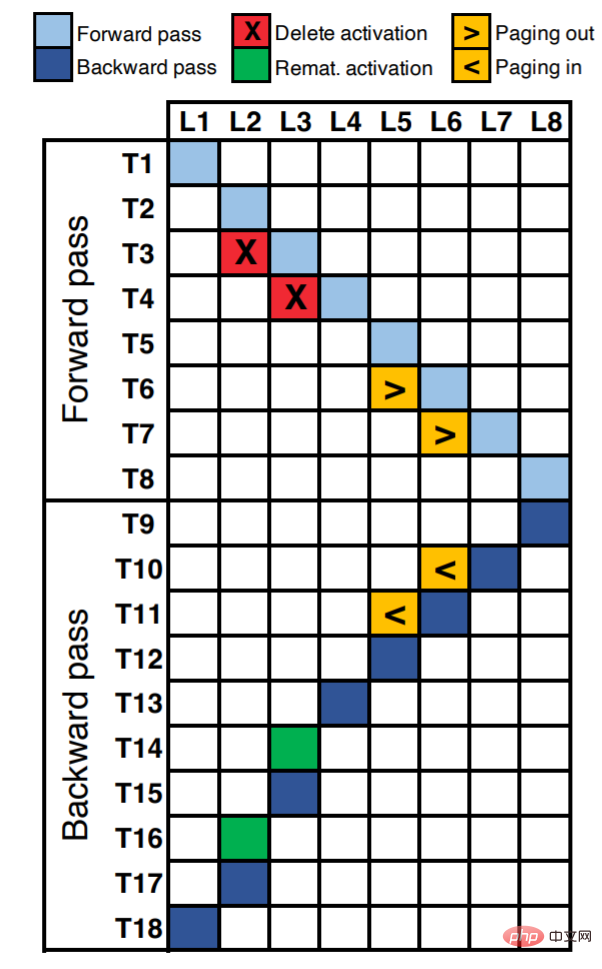

Abbildung 2 zeigt den Ausführungsplan eines achtschichtigen neuronalen Netzwerks. Entlang der X-Achse entspricht jede Einheit jeder Schicht des neuronalen Netzwerks (insgesamt 8 Schichten L8). Die Y-Achse stellt den logischen Zeitschritt innerhalb einer Epoche dar. Die belegten Zellen im Diagramm (mit Farbe gefüllt) stellen die im entsprechenden Zeitschritt durchgeführten Operationen dar (Vorwärts-/Rückwärtsausbreitungsberechnung, Neuimplementierung oder Paging).

Zum Beispiel können wir sehen, dass die Aktivierung von L1 im ersten Zeitschritt (T1) berechnet wird. Bei T2 und T3 werden die Aktivierungsbeträge von L2 bzw. L3 berechnet. Geht man davon aus, dass es sich bei den Schichten L2 und L3 um speicherintensive, aber rechentechnisch kostengünstige Operationen wie Nichtlinearität (tanH, ReLU usw.) handelt, dann ist eine Neuimplementierung die beste Wahl. Wir können Aktivierungen ({T3, L2}, {T4, L3}) löschen, um Speicher freizugeben, und wenn diese Aktivierungen während der Backpropagation benötigt werden, können wir sie erneut implementieren ({T14, L3}, {T16, L2}).

Angenommen, die L5- und L6-Schichten sind rechenintensive Operationen wie Faltung, dichte Matrixmultiplikation usw. Bei solchen Vorgängen führt eine Neuimplementierung zu einer erhöhten Laufzeit und Energie und ist nicht optimal. Für diese Schichten ist es besser, die Aktivierungstensoren in den Hilfsspeicher ({T6, L5}, {T7, L6}) und bei Bedarf in ({T10, L6}, {T11, L5}) auszulagern.

Einer der Hauptvorteile von Paging besteht darin, dass es per Pipeline verarbeitet werden kann, um die Latenz abhängig von der Speicherbusbelegung auszublenden. Dies liegt daran, dass moderne Systeme über eine DMA-Funktion (Direct Memory Access) verfügen, die Aktivierungstensoren vom Sekundärspeicher in den Hauptspeicher verschiebt, während die Rechen-Engines parallel laufen. Beispielsweise kann im Zeitschritt T7 gleichzeitig L6 aufgerufen und L7 berechnet werden. Allerdings ist die Neuimplementierung rechenintensiv und nicht parallelisierbar, was zu einer erhöhten Laufzeit führt. Beispielsweise müssen wir den Zeitschritt T14 verwenden, um L3 neu zu berechnen, wodurch sich der Rest der Backpropagation-Ausführung verzögert.

POET

Diese Forschung schlägt POET vor, einen Compiler auf Graphenebene für tiefe neuronale Netze, der den Trainings-DAG großer Modelle neu schreibt, um Speicherbeschränkungen auf Edge-Geräten anzupassen und gleichzeitig eine hohe Energie aufrechtzuerhalten Effizienz.

POET ist hardwarebewusst und verfolgt zunächst die Ausführung von Vorwärts- und Rückwärtsdurchläufen sowie die damit verbundenen Speicherzuweisungsanforderungen, die Laufzeit sowie den Speicher- und Energieverbrauch jedes Vorgangs. Diese feinkörnige Analyse jeder Arbeitslast erfolgt nur einmal für eine bestimmte Hardware, ist automatisiert, kostengünstig und bietet das genaueste Kostenmodell für POET.

POET generiert dann ein gemischt-ganzzahliges lineares Programm (MILP), das effizient gelöst werden kann. Der POET-Optimierer sucht nach effizienten Neuimplementierungen und Paging-Zeitplänen, die den speichergebundenen End-to-End-Energieverbrauch minimieren. Der resultierende Zeitplan wird dann verwendet, um einen neuen DAG für die Ausführung auf dem Edge-Gerät zu generieren.

Obwohl MILP auf handelsüblicher Hardware gelöst wird, umfasst der an das Edge-Gerät gesendete Zeitplan nur wenige hundert Bytes, was ihn sehr speichereffizient macht.

Reimplementierungen sind am effizientesten für Vorgänge, die rechenintensiv, aber speicherintensiv sind. Allerdings eignet sich Paging am besten für rechenintensive Vorgänge, bei denen eine Neuimplementierung einen erheblichen Energieaufwand verursachen würde. POET erwägt gemeinsam die Neuimplementierung und das Paging in einem integrierten Suchraum.

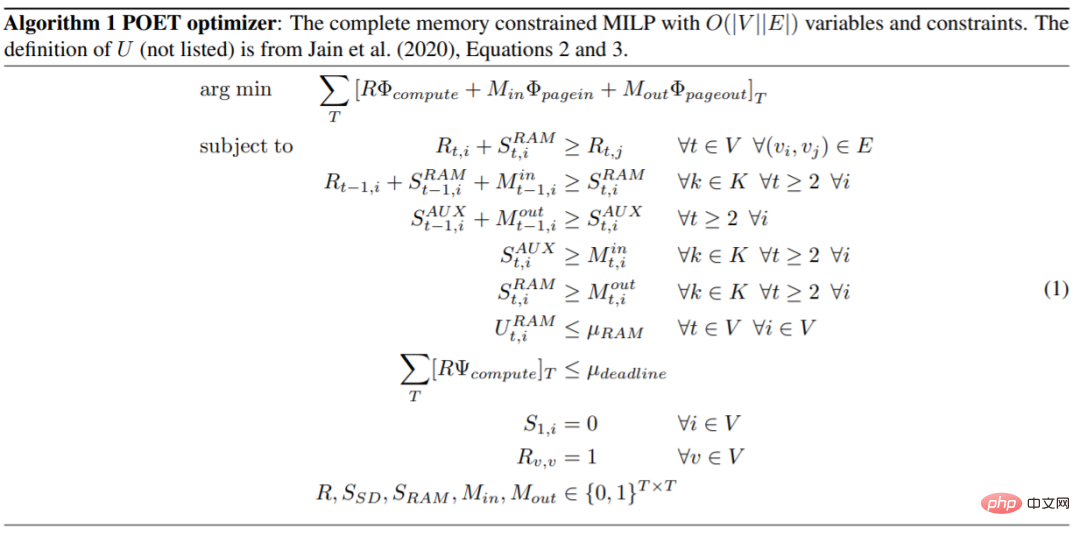

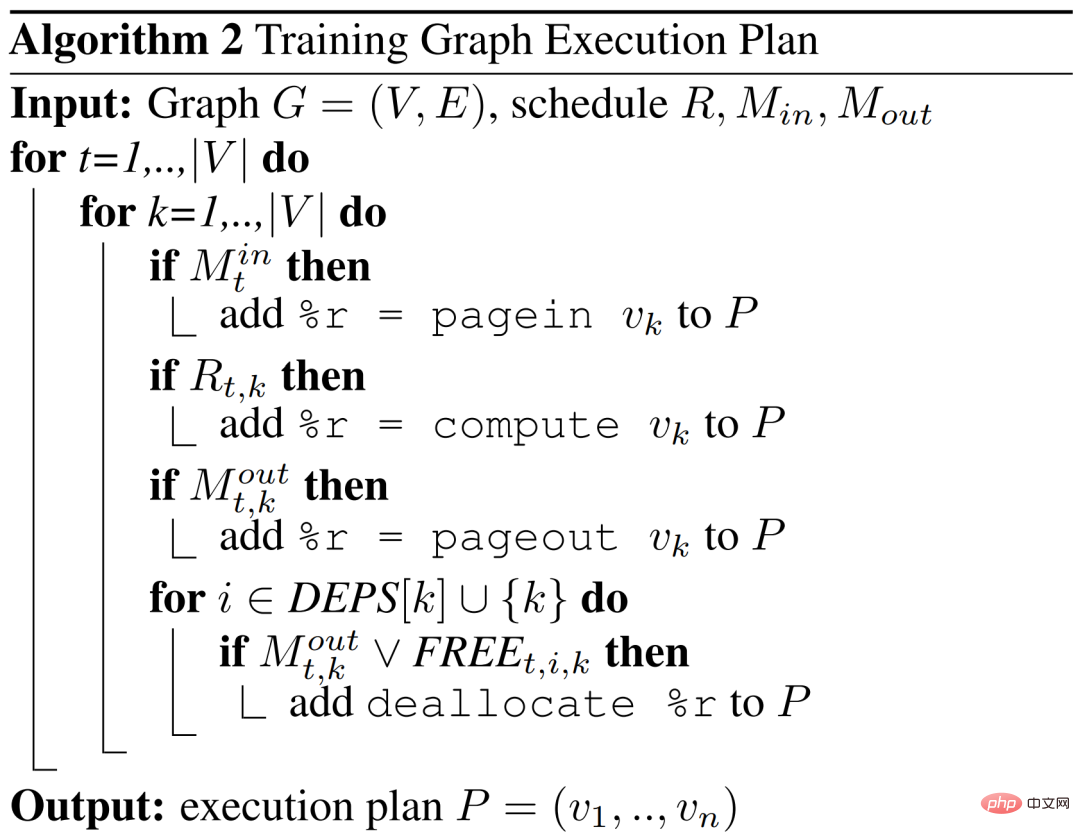

Die Methode in diesem Artikel kann auf komplexe und realistische Architekturen erweitert werden. Der POET-Optimierungsalgorithmus ist wie folgt.

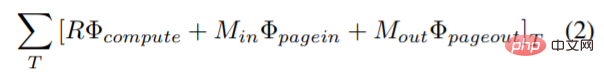

Diese Studie führt eine neue Zielfunktion in das Optimierungsproblem ein, um den umfassenden Energieverbrauch von Berechnung, Ein- und Auslagerung zu minimieren, das Neue Die Zielfunktion, die Paging und Neuimplementierung kombiniert, lautet:

wobei Φ_compute, Φ_pagein und Φ_pageout jeweils die Berechnung jedes Knotens und jeder Seite darstellen wird beim Ein- und Auslagern verbraucht.

POET gibt den DAG-Zeitplan basierend darauf aus, welche Knoten (k) des Diagramms bei jedem Zeitschritt (t) neu implementiert werden und welche Knoten ein- oder ausgelagert werden.

Experimentelle Ergebnisse

Experimentelle Ergebnisse

Bei der Evaluierung von POET versuchten die Forscher, drei Schlüsselfragen zu beantworten. Erstens: Wie viel Energie kann POET über verschiedene Modelle und Plattformen hinweg einsparen? Zweitens: Wie profitiert POET von einer hybriden Paging- und Neuimplementierungsstrategie? Und schließlich: Wie passt sich POET an unterschiedliche Laufzeitbudgets an?

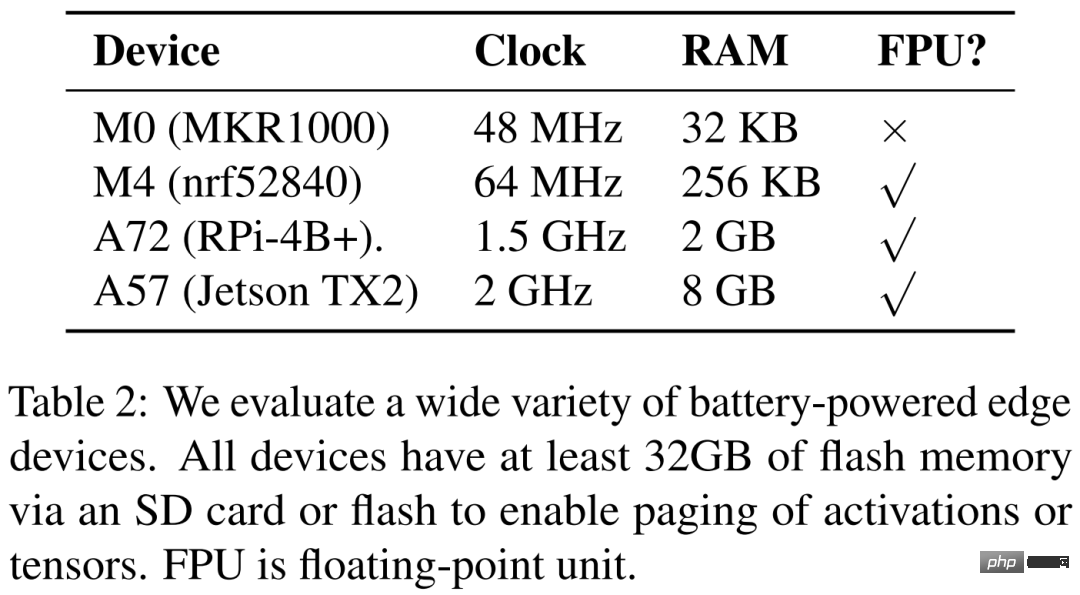

Die Forscher listen in der folgenden Tabelle 2 vier verschiedene Hardwaregeräte auf, nämlich ARM Cortex M0 MKR1000, ARM Cortex M4F nrf52840, A72 Raspberry Pi 4B+ und Nvidia Jetson TX2. POET ist vollständig hardwarebewusst und verlässt sich auf eine feinkörnige Analyse.

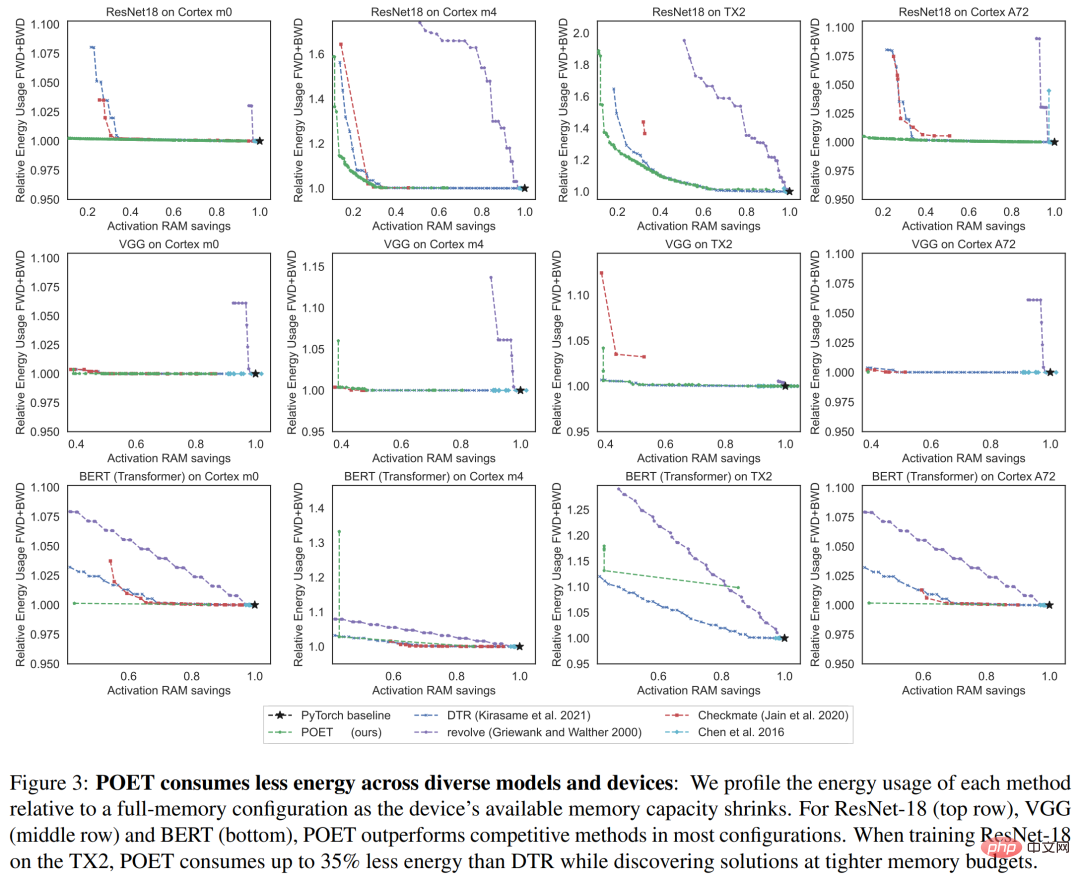

Abbildung 3 unten zeigt den Energieverbrauch einer einzelnen Trainingsepoche. Jede Spalte entspricht einer anderen Hardwareplattform. Die Forscher fanden heraus, dass POET plattformübergreifend energieeffiziente Zeitpläne (Y-Achse) generiert und gleichzeitig den Spitzenspeicherverbrauch (X-Achse) reduziert und Zeitbudgets einhält.

Abbildung 3 unten zeigt den Energieverbrauch einer einzelnen Trainingsepoche. Jede Spalte entspricht einer anderen Hardwareplattform. Die Forscher fanden heraus, dass POET plattformübergreifend energieeffiziente Zeitpläne (Y-Achse) generiert und gleichzeitig den Spitzenspeicherverbrauch (X-Achse) reduziert und Zeitbudgets einhält.

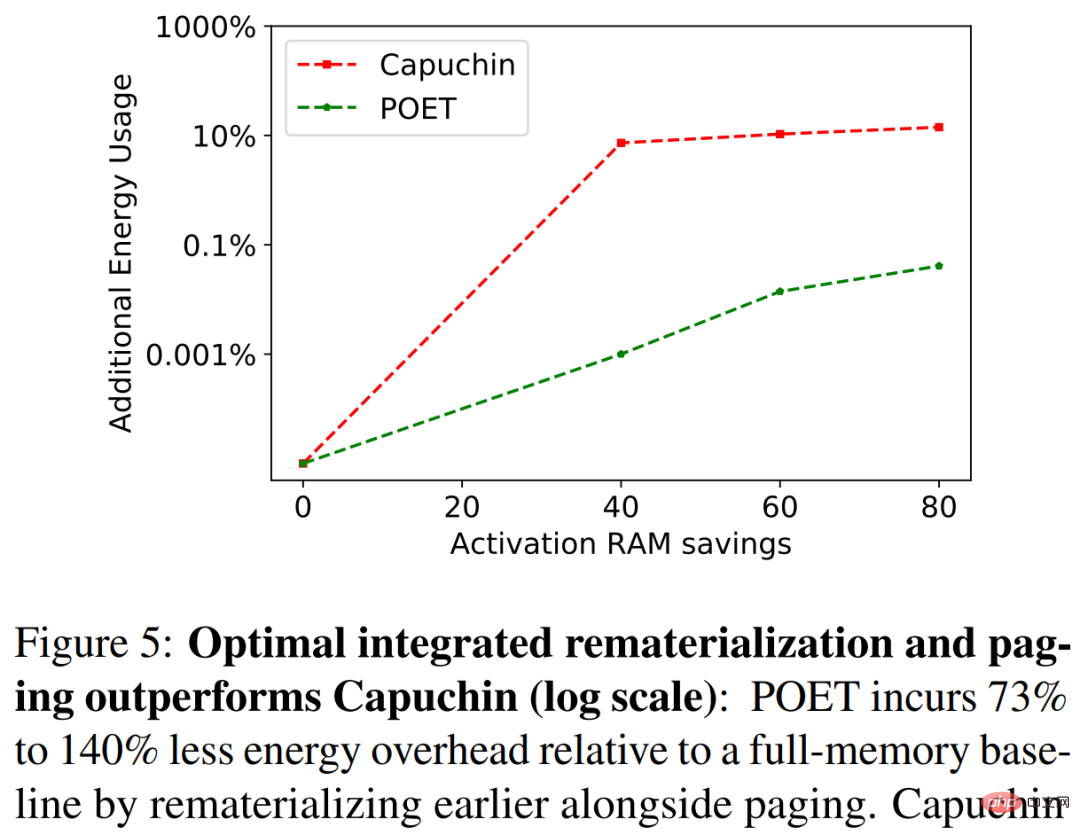

In Abbildung 5 unten verglichen die Forscher POET und Capuchin beim Training von ResNet-18 auf A72. Mit sinkendem RAM-Budget verbraucht Capuchin bei vollem Speicher 73 % bis 141 % mehr Energie als die Basisversion. Im Vergleich dazu erzeugt POET weniger als 1 % der verbrauchten Energie. Dieser Trend gilt für alle getesteten Architekturen und Plattformen.

In Abbildung 5 unten verglichen die Forscher POET und Capuchin beim Training von ResNet-18 auf A72. Mit sinkendem RAM-Budget verbraucht Capuchin bei vollem Speicher 73 % bis 141 % mehr Energie als die Basisversion. Im Vergleich dazu erzeugt POET weniger als 1 % der verbrauchten Energie. Dieser Trend gilt für alle getesteten Architekturen und Plattformen.

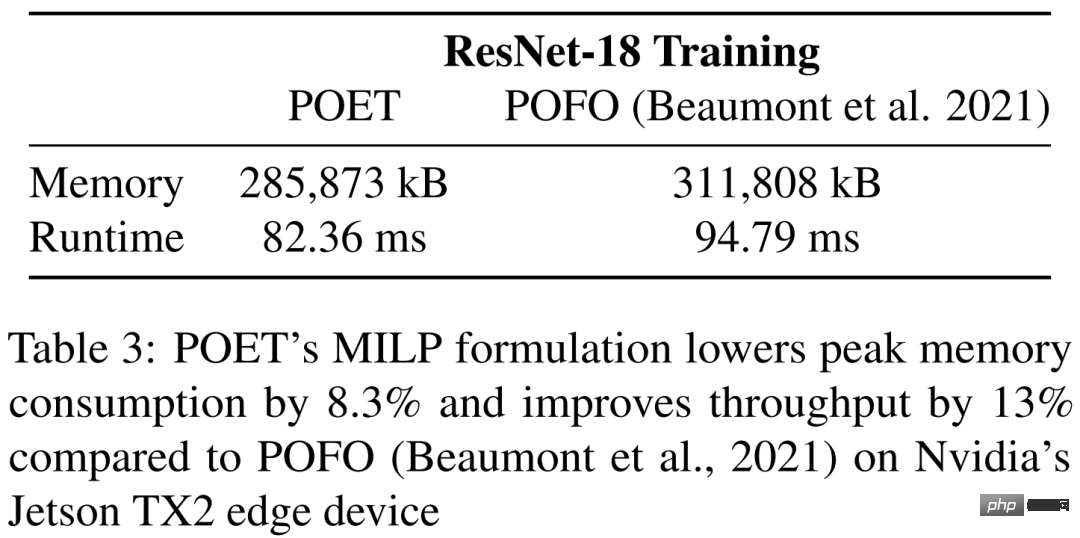

In Tabelle 3 vergleicht die Studie POET und POFO beim Training von ResNet-18 auf Nvidias Jetson TX2. Die Studie ergab, dass POET eine integrierte Neuimplementierung und Paging fand, die den Spitzenspeicherverbrauch um 8,3 % reduzierte und den Durchsatz um 13 % verbesserte. Dies zeigt den Vorteil des MILP-Lösers von POET, der über einen größeren Suchraum optimieren kann. Während POFO nur lineare Modelle unterstützt, kann POET auf nichtlineare Modelle verallgemeinert werden, wie in Abbildung 3 dargestellt.

In Tabelle 3 vergleicht die Studie POET und POFO beim Training von ResNet-18 auf Nvidias Jetson TX2. Die Studie ergab, dass POET eine integrierte Neuimplementierung und Paging fand, die den Spitzenspeicherverbrauch um 8,3 % reduzierte und den Durchsatz um 13 % verbesserte. Dies zeigt den Vorteil des MILP-Lösers von POET, der über einen größeren Suchraum optimieren kann. Während POFO nur lineare Modelle unterstützt, kann POET auf nichtlineare Modelle verallgemeinert werden, wie in Abbildung 3 dargestellt.

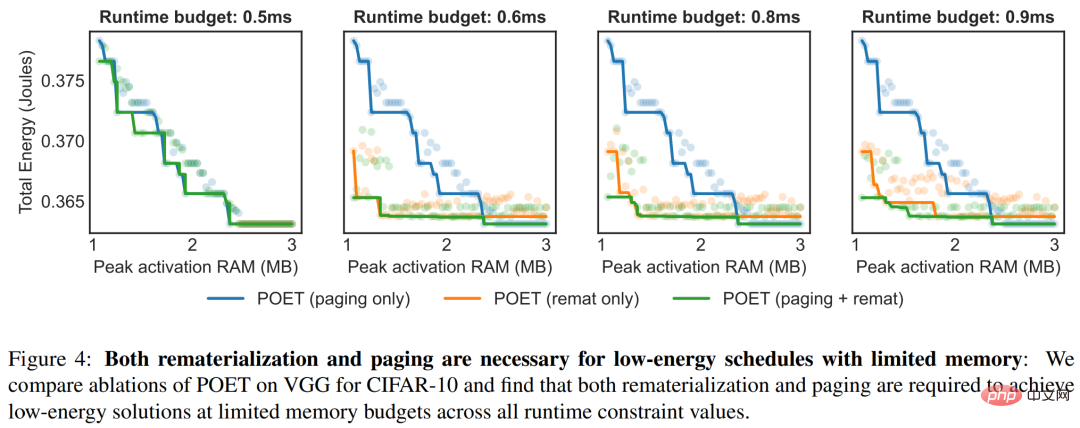

Abbildung 4 verdeutlicht die Vorteile der Anwendung einer Ensemble-Strategie durch POET unter verschiedenen Zeitbeschränkungen. Für jede Laufzeit ist in der folgenden Abbildung der Gesamtenergieverbrauch dargestellt.

Abbildung 4 verdeutlicht die Vorteile der Anwendung einer Ensemble-Strategie durch POET unter verschiedenen Zeitbeschränkungen. Für jede Laufzeit ist in der folgenden Abbildung der Gesamtenergieverbrauch dargestellt.

Das obige ist der detaillierte Inhalt vonErstmaliges Training von BERT und ResNet auf einem Smartphone, wodurch der Energieverbrauch um 35 % gesenkt wird. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Technologietrends, die Sie im Jahr 2023 im Auge behalten sollten

- Wie künstliche Intelligenz Rechenzentrumsteams neue Alltagsaufgaben beschert

- Können künstliche Intelligenz oder Automatisierung das Problem der geringen Energieeffizienz in Gebäuden lösen?

- OpenAI-Mitbegründer im Interview mit Huang Renxun: Die Argumentationsfähigkeiten von GPT-4 haben noch nicht die Erwartungen erfüllt

- Dank der OpenAI-Technologie übertrifft Bing von Microsoft Google im Suchverkehr