Heim >Technologie-Peripheriegeräte >KI >Inspiration durch Teslas selbst entwickelte Chip-Architektur

Inspiration durch Teslas selbst entwickelte Chip-Architektur

- PHPznach vorne

- 2023-04-08 22:51:021080Durchsuche

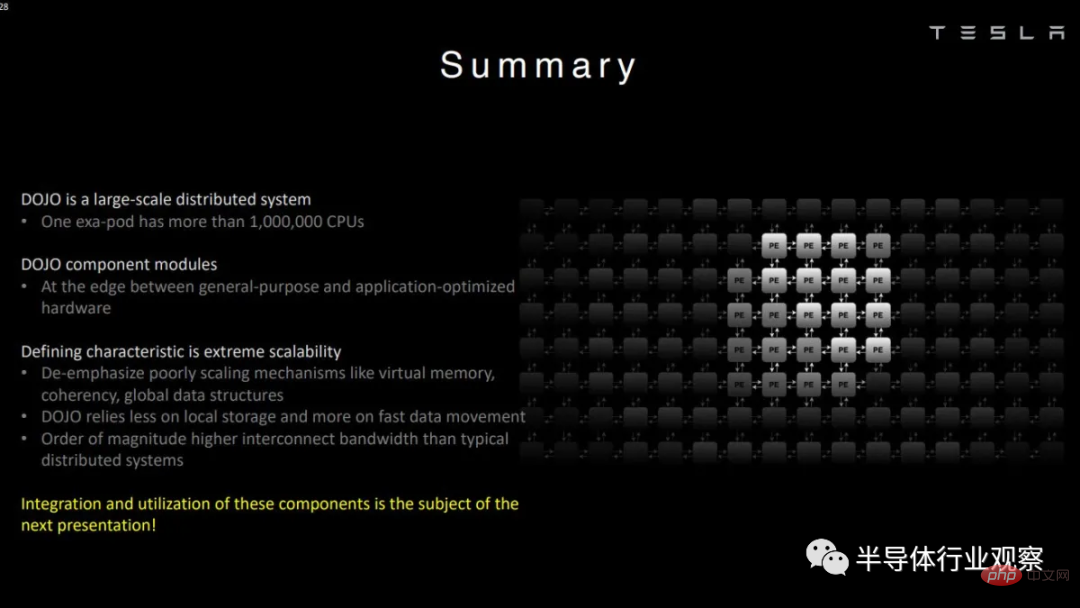

Zu sagen, dass Tesla nur an maschinellem Lernen interessiert ist, wäre eine Untertreibung. Tatsächlich hat der Elektroautohersteller einen hauseigenen Supercomputer namens Dojo gebaut, der für das Training seiner Modelle für maschinelles Lernen optimiert ist.

Im Gegensatz zu vielen anderen Supercomputern verwendet Dojo keine handelsüblichen CPUs und GPUs, etwa von AMD, Intel oder Nvidia. Tesla entwarf seine Mikroarchitektur auf der Grundlage ihrer Bedürfnisse und ermöglichte so Kompromisse, die bei allgemeineren Architekturen nicht möglich waren.

In diesem Artikel werfen wir einen Blick auf die Architektur basierend auf Teslas Demo bei Hot Chips. Die Architektur hat keinen eigenen Namen. Der Einfachheit halber sprechen wir im Folgenden immer von der Architektur, wenn wir von Dojo sprechen.

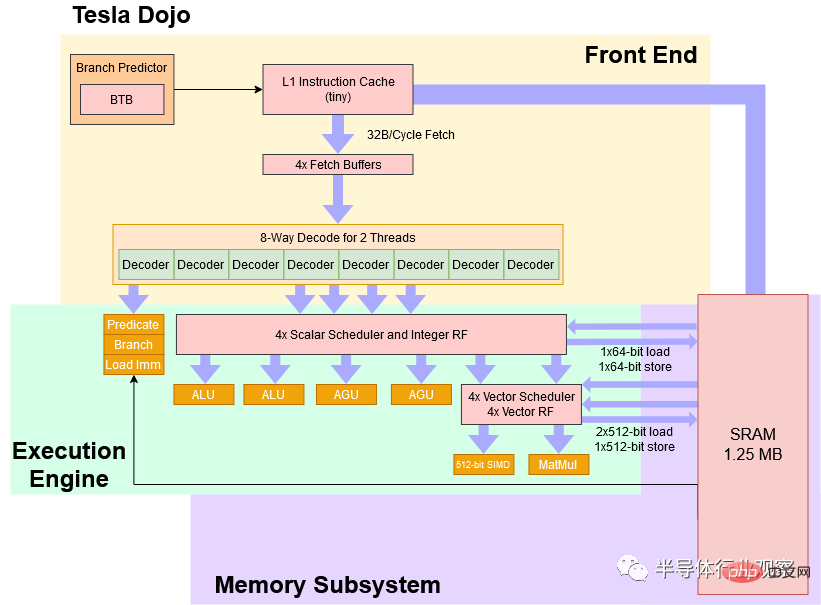

Blockdiagramm

Auf hohem Niveau ist Dojo ein 8-Wide-Core mit Vier-Wege-SMT, der mit konservativen 2 GHz läuft, mit einer Pipeline im CPU-Stil, die es toleranter gegenüber verschiedenen Algorithmen macht als a GPU- und Zweigcode. Der Befehlssatz von Dojo ähnelt in skalarer Hinsicht dem von RISC-V, die Tesla-Ingenieure fügten jedoch einen benutzerdefinierten Satz von Vektoranweisungen hinzu, die sich auf die Beschleunigung des maschinellen Lernens konzentrieren.

Vereinfachtes Blockdiagramm des Tesla Dojo-Kerns

Tesla beschreibt Dojo als „Allzweck-CPU mit hohem Durchsatz“. Aus leistungstechnischer Sicht ist daran definitiv etwas Wahres dran. Doch um die Rechendichte zu erhöhen, hat Tesla ein Opfer gebracht, und Dojo-Kerne sind im Vergleich zu den CPUs, die wir aus Desktops, Laptops und Smartphones kennen, sehr schwierig zu verwenden. In mancher Hinsicht ähnelt der Dojo-Kernel eher dem SPE in IBMs Cell als einem herkömmlichen Allzweck-CPU-Kernel.

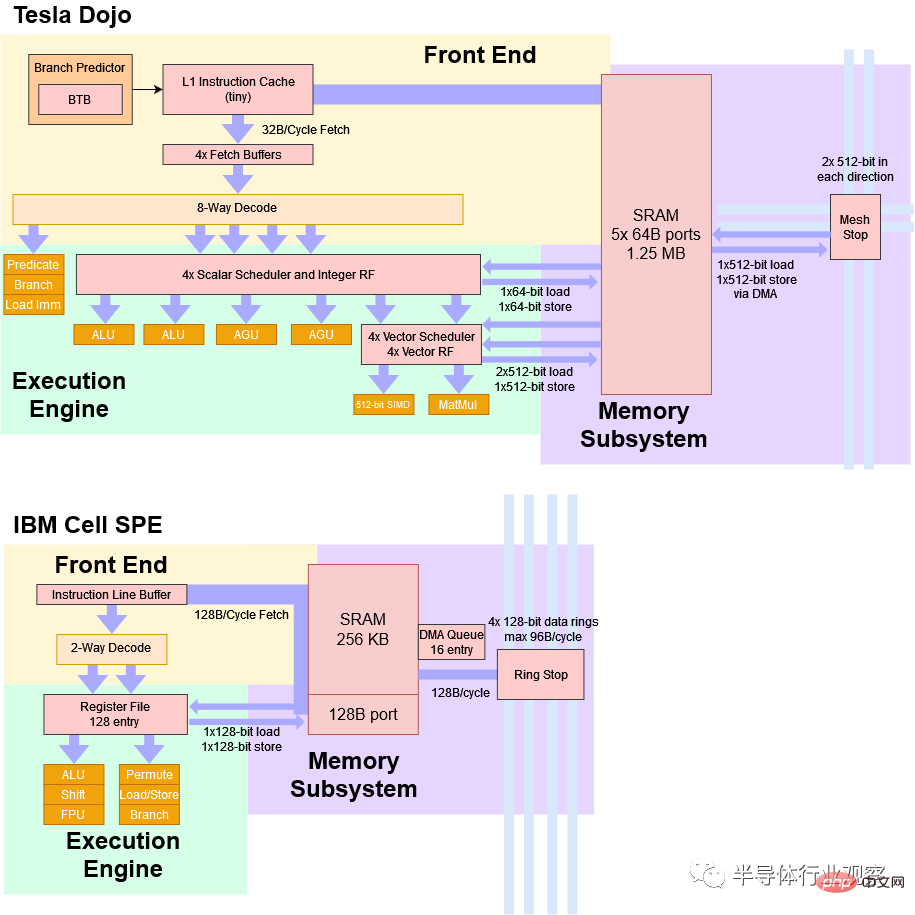

Wie Cells SPE?

Der Mitte der 2000er Jahre eingeführte IBM Cell-Prozessor verfügt über acht „Synergistic Processing Elements“ oder SPEs, die aus einer voll funktionsfähigen CPU-Kernsteuerung („Power Processing Element“ oder PPE: Power Processing Element) bestehen. Auf den ersten Blick hat Dojo viele Ähnlichkeiten mit SPE.

Sowohl Dojo als auch SPE sind für die Vektorverarbeitung optimiert und verlassen sich bei der Arbeitsverteilung auf separate Host-Prozessoren. Auf Dojo oder SPE ausgeführter Code kann nicht direkt auf den Systemspeicher zugreifen. Stattdessen wird erwartet, dass Anwendungen hauptsächlich in einem kleinen Teil des lokalen SRAM funktionieren. Dieser lokale SRAM wird per Software verwaltet und kann nicht als Cache verwendet werden. Wenn Daten aus dem Hauptspeicher benötigt werden, müssen diese über eine DMA-Operation eingebracht werden.

Schließlich fehlt sowohl Dojo als auch Cells SPE die Unterstützung für virtuellen Speicher. Wir werden später im Detail darauf eingehen, was das bedeutet, aber kurz gesagt: Es macht Multitasking sehr schwierig.

Ein sehr vereinfachter Vergleich zwischen Tesla Dojo und IBM Cell SPE

Dojo unterscheidet sich in mehreren wichtigen Punkten. Da Dojo nicht für kleine Bereitstellungen konzipiert wurde, befindet sich der Hostprozessor auf einem separaten Hostsystem. Diese Hostsysteme verfügen über PCIe-Karten mit Schnittstellenprozessoren, die dann über Hochgeschwindigkeits-Netzwerkverbindungen mit den Dojo-Chips verbunden sind. Im Gegensatz dazu befindet sich der Hauptprozessor von Cell auf demselben Chip. Dadurch ist es möglich, einzelne Cell-Chips einzeln einzusetzen – etwas, das in Dojo nicht möglich ist.

Dojos 1,25 MB großer lokaler SRAM-Block ist viel größer und hat eine höhere Bandbreite als der Cell SPE, der nur 256 KB SRAM hat. Der 256-KB-SRAM von Cell verfügt nur über einen Port, der 128 B pro Zyklus liefern kann. Der SRAM von Dojo verfügt über fünf 64B-Ports. Natürlich sind die architektonischen Ziele sehr unterschiedlich. Dojo ist breit getaktet und niedrig getaktet, während Cell SPE über schmale und tiefe Pipelines verfügt, die für hohe Taktung ausgelegt sind.

Frontend: CPU-Komfort usw.

Lassen Sie uns kurz die Dojo-Pipelines vorstellen, beginnend mit dem Frontend. Es gibt eine Art Verzweigungsprädiktor, wie Teslas Diagramm BTB (Branch Target Buffer: Verzweigungszielpuffer) zeigt. Seine Vorhersagefähigkeiten erreichen möglicherweise nicht das Niveau, das wir bei Hochleistungskernen von AMD, ARM und Intel sehen, da Dojo die Chipfläche vorrangig für die Vektorausführung aufwenden muss. Aber selbst ein einfacher Verzweigungsprädiktor ist eine große Verbesserung gegenüber keinem Prädiktor, und die Verzweigungsvorhersagefunktionen von Dojo sollten bei der Verarbeitung von verzweigtem Code oder größeren Befehlsflächen eine bessere Leistung als die GPU bieten.

Sobald der Verzweigungsprädiktor den nächsten Befehlsabrufzeiger generiert, kann Dojo 32 Bytes pro Zyklus aus dem „kleinen“ Befehlscache in Abrufpuffer pro Thread abrufen. Dieser Befehlscache kann dazu beitragen, den Druck auf die Befehlsbandbreite auf dem lokalen SRAM zu verringern und sicherzustellen, dass die Datenseite mit möglichst wenig Konflikten auf den SRAM zugreifen kann. Darüber hinaus ist der Befehlscache nicht kohärent. Wenn neuer Code in den lokalen SRAM geladen wird, muss der Befehlscache geleert werden, bevor zum neuen Code verzweigt wird.

Hot-Chips-Präsentation von Tesla

Aus dem Abrufpuffer kann Dojos Decoder acht Anweisungen pro Zyklus aus zwei Threads verarbeiten. Ich bin etwas verwirrt darüber, was „zwei Threads pro Zyklus“ bedeutet, da CPUs mit SMT normalerweise einen Thread pro Zyklus verarbeiten und Threads an Zyklusgrenzen wechseln. Möglicherweise teilt Dojo den Decoder in zwei Cluster auf und wählt zwei Threads aus, um ihnen in jeder Schleife Daten zuzuführen. Dies kann den Decodierungsdurchsatznachteil für die genommene Verzweigung verringern.

Während der Dekodierung können bestimmte Anweisungen (z. B. Verzweigungen, prädizierte Operationen und sofortige Ladevorgänge („Listenparsing“)) im Frontend ausgeführt und aus der Pipeline entfernt werden. Dies ist ein bisschen wie bei neueren x86-CPUs, bei denen Register-zu-Register-Kopien beim Renamer entfallen. Aber Sie haben richtig gehört – Dojo verfolgt keine „Eliminierungs“-Anweisungen über die Pipeline, um den ordnungsgemäßen Ruhestand aufrechtzuerhalten. Andere Prozessoren verfolgen alles bis zum Beenden, sodass sie an jeder Befehlsgrenze anhalten und den gesamten Status beibehalten können, der zum Fortsetzen der Ausführung erforderlich ist. Diese Fähigkeit wird als „präzise Ausnahmen“ bezeichnet und moderne Betriebssysteme nutzen sie, um alle möglichen Extras bereitzustellen, wie z. B. Paging auf die Festplatte oder um Ihnen genau mitzuteilen, wo Ihr Code fehlerhaft ist.

Tesla kümmert sich nicht um konkrete Ausnahmen. Dojo verfügt zwar über einen Debug-Modus, in dem mehr Anweisungen durch die Pipeline geleitet werden, um „präzisere“ Ausnahmen bereitzustellen, aber es gibt keine geordnete Exit-Logik wie bei einer normalen Out-of-Order-CPU.

Dojos Ausführungs-Engine

Nachdem wir ein breites Frontend gesehen haben, könnte es etwas seltsam sein, eine 4-weite Integer-Ausführungs-Engine mit nur zwei ALUs und zwei AGUs zu sehen. Diese trichterförmige Pipeline ist jedoch sinnvoll, da einige Anweisungen am Frontend ausgeführt und verworfen werden.

Dojo schafft es auch nicht in Client-Systeme, bei denen die Leistung skalarer Ganzzahlen wichtig ist. Daher bietet die Ganzzahlseite ausreichend Durchsatz, um den Kontrollfluss und die Adressgenerierung zu bewältigen und so die Vektor- und Matrixzellen mit Strom zu versorgen.

Dojos Vektor- und Matrixausführungsenden werden nach der Skalarausführungs-Engine in der Kernpipeline platziert, und es gibt zwei Ausführungspipelines. Zwei Pipelines klingen vielleicht nicht nach viel, aber Dojo verfügt hinter diesen Pipelines über sehr große Ausführungseinheiten. Eine Pipeline kann eine 512-Bit-Vektorausführung durchführen, während die andere Pipeline eine 8x8x4-Matrixmultiplikation durchführt. Solange die Anweisungen genügend explizite Parallelität aufweisen, kann Dojo daher einen sehr hohen Durchsatz erzielen – insbesondere bei Verwendung von Matrixeinheiten. Tesla behauptet, dass ein Chip mit 354 Dojo-Kernen 362 BF16 TFLOPS bei 2 GHz erreichen kann, was darauf hindeutet, dass jeder Kern 512 BF16 FLOPS pro Zyklus ausführen kann.

Wir sind nicht sicher, ob Dojo eine völlig außer Betrieb befindliche Ausführung durchführen kann. Aber Tesla sagte, dass die Integer-Seite der Vektorseite weit voraus sein kann, was darauf hindeutet, dass sie Anweisungen ausführen könnte, die früher ins Stocken gerieten, bis einer der Scheduler voll war. Das Fehlen einer geordneten Stilllegung weist auch darauf hin, dass die Ausführungsfähigkeiten außerhalb der Reihenfolge liegen.

Im Allgemeinen ist die Implementierung einer Out-of-Order-Ausführung mit großer Komplexität verbunden. Dies liegt daran, dass die CPU Anweisungen nacheinander ausführen muss. Hochleistungs-CPUs von AMD, ARM und Intel verwenden große Neuordnungspuffer (und andere Strukturen), um Anweisungen zu verfolgen, damit ihre Ergebnisse in der Programmreihenfolge festgeschrieben werden können. Das heißt, wenn ein Programm etwas Dummes macht, wie zum Beispiel durch Null dividieren, können diese Kerne genau anzeigen, welche Anweisung fehlgeschlagen ist. Darüber hinaus können sie einen CPU-Status anzeigen, der die Aktionen aller Anweisungen vor dem Fehler widerspiegelt, jedoch nicht danach. Dies bedeutet, dass Sie die Ursache für den Fehler bei der Anweisung beheben und die Ausführung fortsetzen können. Dojo gibt diese Fähigkeit auf. Im Gegenzug vermeidet Dojo den Energie- und Flächenaufwand, der mit der Verfolgung jeder Anweisung durch seine Pipeline verbunden ist, um sicherzustellen, dass die Ergebnisse in der Programmreihenfolge geliefert werden.

SRAM-Zugriff

Normalerweise würden wir hier über Caching sprechen. Da Dojo jedoch keinen direkten Zugriff auf den Systemspeicher hat, werden wir den 1,25-MB-SRAM-Block besprechen. Es kann zwei 512-Bit-Ladevorgänge pro Zyklus verarbeiten und bietet so eine Bandbreite pro Zyklus, die AVX-512-fähigen Intel-CPUs entspricht. Laut Tesla verfügt der SRAM über fünf 512-Bit-Ports (2 Ladeports, 1 Speicherport und zwei Stop-to-Grid-Ports). Auf der Skalarseite gibt es jedoch nur zwei AGUs, was wahrscheinlich bedeutet, dass der Kern nicht zwei 512-Bit-Ladevorgänge und einen 512-Bit-Speicher pro Zyklus verarbeiten kann.

Da der lokale SRAM-Block von Dojo nicht zwischengespeichert wird, sind die mit den Daten gespeicherten Tag- und Statusbits nicht erforderlich. Dem SRAM ist außerdem kein L1D-Cache vorgeschaltet, daher muss er schnell genug sein, um alle Lade- und Speicheranweisungen zu verarbeiten, ohne einen Engpass zu verursachen, auch wenn er in seiner Größe näher am L2-Cache liegt. Der Verzicht auf die Implementierung von SRAM als Cache könnte Teslas Methode sein, die Latenz niedrig zu halten. Wenn wir auf AMDs Hammer-Architektur von vor langer Zeit zurückblicken, können wir sehen, dass der Zugriff auf 1 MB L2 nach der Erkennung eines L1D-Fehlers 8 Zyklen dauerte (bei einer Gesamtlatenz von 12 Zyklen). Wenn 1 MB SRAM direkt adressiert und nicht als Cache verwendet würde, könnten drei Stufen entfernt werden, wodurch die Latenz auf 5 Zyklen reduziert würde:

Folie aus einer früheren Hot-Chips-Präsentation, die L2 zeigt. Die am Cache-Zugriff beteiligten Pipeline-Stufen. Wenn L2 kein Cache ist, werden Stufen, die übersprungen werden können, rot markiert.

Angesichts jahrzehntelanger Prozessknotenverbesserungen und noch niedrigerer Taktratenziele als Athlon ist es leicht zu erkennen, wie Tesla auf SRAM-Blöcke der L2-Größe mit L1-ähnlicher Latenz zugreifen könnte. Das Überspringen des L1-Cache spart sicherlich Platz und Strom.

Um Latenz, Fläche und Kernkomplexität weiter zu reduzieren, bietet Dojo keine Unterstützung für virtuellen Speicher. Daher verfügt es über keine TLB- oder Page-Walk-Mechanismen. Moderne Betriebssysteme nutzen virtuellen Speicher, um jedem Prozess eine eigene Speicheransicht zu geben. Die vom Programm verwendete Speicheradresse ist kein direkter Zugriff auf die physische Speicheradresse, sondern wird von der CPU mithilfe der vom Betriebssystem festgelegten Paging-Struktur in eine physische Adresse umgewandelt. Auf diese Weise isolieren moderne Betriebssysteme Programme voneinander und verhindern, dass eine fehlerhafte Anwendung das gesamte System zum Absturz bringt.

Mit dem virtuellen Speicher können Sie auch mehr Programme ausführen als mit dem physischen Speicher. Wenn Ihnen der reale Speicher ausgeht, hebt das Betriebssystem die Zuordnung der Seite auf, schreibt sie auf die Festplatte und stellt Ihrem Programm den benötigten Speicher zur Verfügung. Wenn ein anderes schlechtes Programm versucht, auf diesen Speicher zuzugreifen, versucht die CPU, die virtuelle Adresse in eine physische Adresse zu übersetzen, stellt jedoch fest, dass die Übersetzung nicht existiert. Die CPU löst eine Seitenfehlerausnahme aus, die das Betriebssystem verarbeitet, indem es die entfernte Seite zurück in den physischen Speicher liest und den Seitentabelleneintrag ausfüllt.

Nichts davon ist auf Dojo möglich. Bei der 4-Wege-SMT-Funktion des Kernels geht es mehr darum, eine einzelne Anwendung expliziter Parallelität auszusetzen, als darum, die Multitasking-Leistung zu verbessern. Beispielsweise kann ein Thread Vektorberechnungen durchführen, während ein anderer Thread asynchron Daten vom Systemspeicher in den SRAM lädt (über DMA).

Um das Design weiter zu vereinfachen, kann Dojo SRAM mit nur 21 Adressbits adressieren, was die AGU und den Adressierungsbus von Dojo vereinfachen kann. Diese Kompromisse könnten es Tesla ermöglichen, mit ausreichend geringer Latenz auf diesen SRAM zuzugreifen, um die Implementierung eines separaten L1-Datencaches davor zu vermeiden.

Speicherzugriff

Apropos Systemspeicher: Der Dojo-Chip ist nicht direkt mit dem Speicher verbunden. Stattdessen verbinden sie sich mit einem Schnittstellenprozessor, der mit einem HBM ausgestattet ist. Diese Schnittstellenprozessoren sind auch für die Kommunikation mit dem Hostsystem verantwortlich.

Dojo-Kachel mit 25 unabhängigen Chips kann auf 160 GB HBM-Speicher zugreifen Tesla sagt, dass sie 900 GB/s von jeder Chipkante über Kachelgrenzen hinweg übertragen können, was bedeutet, dass eine Verbindungsbandbreite von 4,5 TB/s übertragen werden kann Zugriffsschnittstellenprozessor und dessen HBM. Da der Zugriff auf das HBM einen separaten Chip erfordert, kann die Zugriffslatenz sehr hoch sein.

ist klein, wie macht man das?

Dojo ist ein 8-breiter Kernel mit mindestens einigen OoO-Ausführungsfähigkeiten, ordentlichem Vektordurchsatz und einer Matrixmultiplikationseinheit. Aber selbst mit 1,25 MB lokalem SRAM ist es am Ende ein sehr kleiner Kern. Im Vergleich dazu belegt der A64FX von Fujitsu mehr als doppelt so viel Fläche auf demselben Prozessknoten. Beim Prozessordesign kommt es darauf an, die richtigen Kompromisse einzugehen. Tesla möchte den Durchsatz beim maschinellen Lernen maximieren, indem es eine große Anzahl von Kernen auf einen Chip packt, sodass einzelne Kerne klein sein müssen. Um seine Zoneneffizienz zu erreichen, verwendet Dojo einige bekannte Techniken. Es läuft mit konservativen 2 GHz. Schaltungen mit niedrigerem Takt nehmen tendenziell weniger Fläche ein. Es verfügt möglicherweise über einen einfachen Verzweigungsvorhersager und einen kleinen Befehlscache. Wenn das Programm über einen großen Code-Footprint oder viele Verzweigungen verfügt, führt dies zu Leistungseinbußen.

Tesla reduziert aber auch den Stromverbrauch und den Flächenverbrauch weiter, indem es Funktionen eliminiert, die für die Ausführung interner Workloads nicht erforderlich sind. Sie führen kein datenseitiges Caching durch, unterstützen keinen virtuellen Speicher und unterstützen keine präzisen Ausnahmen.

Das Ergebnis ist ein Prozessorkern, der die Leistungsflexibilität moderner CPU-Kerne bietet, aber in vielerlei Hinsicht weniger benutzerfreundlich und programmiererfreundlich ist als der Intel 8086. Zusätzlich zum Kern spart Tesla auch in großem Maßstab Chipfläche ein, indem es Dojo-Chips speziell für den Einsatz entwickelt.

Physische Implementierung

Der Dojo-Kern wird schrumpfend auf einem sehr großen 645 mm2 großen Chip namens D1 implementiert. Im Gegensatz zu anderen uns bekannten Chips ist ein einzelner Dojo-Chip nicht autark. Es verfügt nicht über einen DDR- oder PCIe-Controller. An den Rändern des Chips befinden sich IO-Schnittstellen, die es dem Chip ermöglichen, mit benachbarten Chips mit einer Latenz von etwa 100 ns zu kommunizieren.

Um auf den Systemspeicher zuzugreifen, muss der Dojo D1-Chip mit einem Schnittstellenprozessor kommunizieren, der über ein integriertes HBM verfügt. Der Schnittstellenprozessor wiederum ist über PCIe mit dem Hostsystem verbunden (der Schnittstellenprozessor ist auf einer PCIe-Karte installiert). Theoretisch würde eine minimale funktionale Dojo-Bereitstellung einen Dojo-Chip, eine Schnittstellenprozessorkarte und ein Hostsystem umfassen. Aber Tesla setzt Dojo-Chips in Modulen mit jeweils 25 Chips ein, um einen Eindruck von der Größe zu vermitteln. Der Dojo D1-Chip ist speziell als Baustein für Supercomputer konzipiert und nicht mehr.

Diese Spezialisierung kann mehr Werkzeugfläche einsparen. Dojo D1 verschwendet keinen Platz auf DDR- und PCIe-Controllern. Der größte Teil des Chips wird vom massiven Dojo-Kern eingenommen, mit Ausnahme der benutzerdefinierten E/A-Anschlüsse an der Außenseite, die für die Verbindung mit dem benachbarten Chip ausgelegt sind.

Im Gegensatz dazu verbrauchen Chips, die im Hinblick auf mehr Einsatzflexibilität entwickelt wurden, viel Platz für IO. AMDs Zen 1 „Zeppelin“-Chips zeigen dies sehr gut. Zeppelin kann direkt an DDR4-Speicher, PCIe-Geräte, SATA-Laufwerke und USB-Geräte angeschlossen werden – perfekt für Kundenanforderungen. In einem Server ermöglicht die IFOP-Schnittstelle die Kommunikation mit benachbarten Chips. Große Teile des SRAM, die sich in der Nähe des IFOP befinden, können als Snoop-Filter dienen und dazu beitragen, die Cache-Kohärenz in Umgebungen mit hoher Kernanzahl effizient aufrechtzuerhalten. Dojo versucht nicht, die Cache-Kohärenz zwischen den Kernen aufrechtzuerhalten und verwendet keinen SRAM für die Snoop-Filterung.

Aus AMDs Chiplet-Demo auf der ISSCC 2021

AMD hat dies erreicht, indem es etwa 44 % der „Zeppelin“-Chipfläche für andere Logik als für zu bezahlende Kerne und Cache reserviert hat dies Flexibilität. Dojo nutzt nur 28,9 % der Chipfläche für andere Dinge als SRAM und Kerne.

Abschlussworte

Die Mikroarchitektur hinter dem Tesla Dojo-Supercomputer zeigt, wie man eine sehr hohe Rechendichte erreicht und gleichzeitig die Fähigkeit der CPU zur Verarbeitung von Verzweigungscode beibehält. Um dorthin zu gelangen, müssen Sie auf die meisten Annehmlichkeiten verzichten, die unser modernes Computererlebnis ausmachen. Wenn Sie Ihren Desktop hypothetisch um den Dojo-Kern herum aufbauen können, wird die Erfahrung wahrscheinlich jedem bekannt vorkommen, der MS-DOS verwendet hat. Sie können nicht mehrere Anwendungen gleichzeitig ausführen. Eine einzelne fehlerhafte Anwendung kann Sie dazu zwingen, Ihr System neu zu starten. Wenn Sie nicht über genügend RAM zum Ausführen eines Programms verfügen, können Sie die vollständige Ausführung (ohne Auslagerung auf die Festplatte) vergessen.

Aber diese Kompromisse machen bei Teslas Supercomputer durchaus Sinn. Tesla benötigt keinen Dojo-Kern, um mehrere laufende Anwendungen gleichzeitig zu verarbeiten, Dojo muss lediglich vertrauenswürdigen Code darin ausführen. Tesla kümmert sich also nicht um die Unterstützung des virtuellen Speichers. Ebenso werden maschinelle Lernprogramme, die auf Dojo laufen, unter Berücksichtigung dieses spezifischen Systems geschrieben. Sie verfügen nicht über einen Stapel beliebiger Programme, die möglicherweise mehr Speicher benötigen, als verfügbar ist. Das bedeutet, dass Sie keine genauen Ausnahmen (und keinen virtuellen Speicher) benötigen, um Techniken wie die Überbelegung von Speicher, die Speicherkomprimierung oder den Austausch von Speicherseiten zwischen Festplatten zu ermöglichen. Präzise Ausnahmen sind auch beim Debuggen nützlich, Tesla erledigt dies jedoch auf kostengünstigere Weise durch einen separaten Debug-Modus.

Sicher ist, dass die Kompromisse, die Tesla anwendet, um eine hohe Rechendichte zu erreichen, bei Consumer- oder Server-CPUs nicht möglich sind. Aber in Aktion machen sie jede Menge Spaß, und wir müssen Tesla dafür danken, dass er sich die Zeit genommen hat, sie bei Hot Chips vorzuführen. In den letzten zwei Jahrzehnten verlangsamten sich die Verbesserungen bei Prozessknoten, was zu noch langsameren Fortschritten bei der Single-Threaded-Leistung führte. Leistungs- und Kühlungseinschränkungen haben in den letzten fünf Jahren zu einer Verringerung der Multithread-Leistung geführt. Da der Bedarf an mehr Rechenleistung jedoch nicht abnimmt, greifen Unternehmen auf spezialisiertere Hardware zurück, um Schritt zu halten.

Die Architektur des Dojo-Supercomputers von Tesla ist ein gutes Beispiel dafür, wie Kompromisse zur Erhöhung der Rechendichte eingegangen werden und wie aktuelle Trends die Einführung spezieller Hardware für durchsatzbeschränkte Anwendungen begünstigen.

Das obige ist der detaillierte Inhalt vonInspiration durch Teslas selbst entwickelte Chip-Architektur. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Technologietrends, die Sie im Jahr 2023 im Auge behalten sollten

- Wie künstliche Intelligenz Rechenzentrumsteams neue Alltagsaufgaben beschert

- Können künstliche Intelligenz oder Automatisierung das Problem der geringen Energieeffizienz in Gebäuden lösen?

- OpenAI-Mitbegründer im Interview mit Huang Renxun: Die Argumentationsfähigkeiten von GPT-4 haben noch nicht die Erwartungen erfüllt

- Dank der OpenAI-Technologie übertrifft Bing von Microsoft Google im Suchverkehr