Heim >Technologie-Peripheriegeräte >KI >Winziges maschinelles Lernen verspricht, Deep Learning in Mikroprozessoren zu integrieren

Winziges maschinelles Lernen verspricht, Deep Learning in Mikroprozessoren zu integrieren

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBnach vorne

- 2023-04-08 13:51:091779Durchsuche

Übersetzer |. Zhu Xianzhong

Rezensent |. Liang Ce Sun Shujuan

Der anfängliche Erfolg von Deep-Learning-Modellen wurde großen Servern mit großen Speichermengen und GPU-Clustern zugeschrieben. Das Versprechen von Deep Learning hat eine Branche hervorgebracht, die Cloud-Computing-Dienste für tiefe neuronale Netze bereitstellt. Infolgedessen erfreuen sich große neuronale Netze, die auf nahezu unbegrenzten Cloud-Ressourcen laufen, großer Beliebtheit, insbesondere bei Technologieunternehmen mit großen Budgets.

Aber gleichzeitig zeichnete sich in den letzten Jahren auch ein weiterer gegenläufiger Trend ab, nämlich die Erstellung von Machine-Learning-Modellen für Edge-Geräte. Diese als Tiny Machine Learning (TinyML) bekannten Modelle funktionieren auf Geräten mit begrenztem Speicher und begrenzter Rechenleistung sowie nicht vorhandener oder eingeschränkter Internetverbindung.

Eine aktuelle Forschungsarbeit, die gemeinsam von IBM und dem Massachusetts Institute of Technology (MIT) durchgeführt wurde, löst das Problem des Spitzenspeicherengpasses von Convolutional Neural Networks (CNN). Hierbei handelt es sich um eine Deep-Learning-Architektur, die besonders für Computer-Vision-Anwendungen wichtig ist. Ein Modell namens McUnETV2, das in der Lage ist, Convolutional Neural Networks (CNN) auf Mikrocontrollern mit geringem Speicher und geringem Stromverbrauch auszuführen, wird in einem auf der NeurIPS 2021-Konferenz vorgestellten Papier detailliert beschrieben.

1. Warum TinyML (TinyML)?

Obwohl Cloud Deep Learning sehr erfolgreich ist, ist es nicht für alle Situationen geeignet. Tatsächlich erfordern viele Anwendungen häufig, dass Inferenzaufgaben direkt auf dem Hardwaregerät ausgeführt werden. Beispielsweise ist in manchen Einsatzumgebungen wie der Drohnenrettung die Internetverbindung nicht garantiert. Auch in anderen Bereichen wie dem Gesundheitswesen erschweren Datenschutzanforderungen und behördliche Auflagen das Senden von Daten zur Verarbeitung in die Cloud. Für Anwendungen, die Echtzeit-Inferenz in Maschinensprache erfordern, ist die durch Round-Trip-Cloud-Computing verursachte Latenz noch unerschwinglicher.

Alle oben genannten Bedingungen müssen erfüllt sein, um Geräte für maschinelles Lernen wissenschaftlich und kommerziell attraktiv zu machen. Beispielsweise verfügen iPhone-Telefone mittlerweile über viele Anwendungen, die Gesichtserkennung und Spracherkennung ausführen, und Android-Telefone können auch Übersetzungssoftware direkt ausführen. Darüber hinaus kann die Apple Watch bereits maschinelle Lernalgorithmen verwenden, um Bewegungen und EKG-Muster zu erkennen (Hinweis: EKG ist die Abkürzung für Elektrokardiogramm, auch bekannt als EKG). Es handelt sich um ein Testexperiment, mit dem die Zeitknoten der auslösenden elektrischen Signalsequenz aufgezeichnet werden Durch die Analyse von EKG-Bildern können Ärzte besser diagnostizieren, ob die Herzfrequenz normal ist und ob Probleme mit der Herzfunktion vorliegen.

Die oben genannten ML-Modelle auf diesen Geräten werden teilweise durch technologische Fortschritte ermöglicht, die eine kompaktere und rechen- und speichereffizientere neuronale Netze unterstützen. Gleichzeitig ist aufgrund der Fortschritte in der Hardwaretechnologie die Implementierung solcher ML-Modelle auch im mobilen Umfeld möglich geworden. Unsere Smartphones und Wearables verfügen heute über mehr Rechenleistung als die Hochleistungsserver von vor 30 Jahren und einige verfügen sogar über spezielle Coprozessoren für maschinelle Sprachinferenz.

TinyML bringt Edge-KI noch einen Schritt weiter und ermöglicht die Ausführung von Deep-Learning-Modellen auf Mikrocontrollern (MCUs), auch wenn Mikrocontroller ressourcenbeschränkter sind als die kleinen Computer, die wir in unseren Taschen und am Handgelenk tragen.

Mikrocontroller hingegen sind preiswert und werden im Durchschnitt für weniger als 0,50 US-Dollar verkauft. Sie sind fast überall zu finden und können in alles eingebaut werden, von der Verbraucherindustrie bis hin zu Industrieanlagen. Gleichzeitig verfügen sie nicht über die Ressourcen, die in Allzweck-Computergeräten zu finden sind, und die meisten verfügen nicht über Betriebssysteme. Die CPU des Mikrocontrollers ist klein, verfügt nur über ein paar hundert Kilobyte Low-Power-Speicher (SRAM) und ein paar Megabyte Speicher und verfügt über keine Netzwerkausrüstung. Die meisten von ihnen verfügen über keinen Stromanschluss und waren viele Jahre lang auf Knopfbatterien angewiesen. Daher könnte die Installation von Deep-Learning-Modellen auf MCUs neue Möglichkeiten für viele Anwendungen eröffnen.

2. Speicherengpass in Faltungs-Neuronalen Netzen

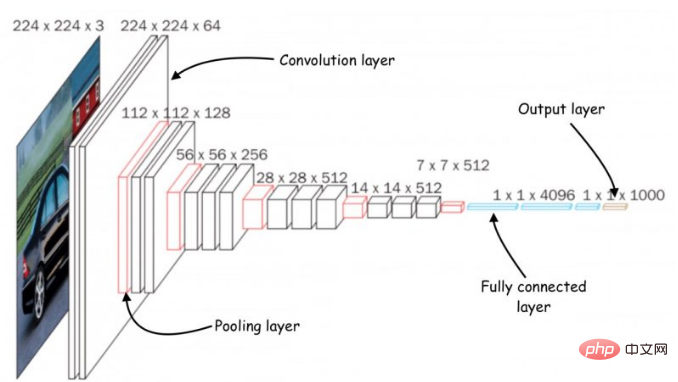

Architektur von Faltungs-Neuronalen Netzen (CNN)

Es wurden mehrere Anstrengungen unternommen, um tiefe neuronale Netze auf eine Größe zu reduzieren, die für Rechengeräte mit kleinem Speicher geeignet ist. Die meisten dieser Bemühungen konzentrieren sich jedoch auf die Reduzierung der Parameteranzahl in Deep-Learning-Modellen. „Pruning“ ist beispielsweise ein beliebter Optimierungsalgorithmus, der neuronale Netze verkleinert, indem unwichtige Parameter aus der Modellausgabe entfernt werden.

Das Problem bei Pruning-Methoden besteht darin, dass sie den Speicherengpass neuronaler Netze nicht lösen können. Standardimplementierungen von Deep-Learning-Bibliotheken erfordern, dass die gesamte Netzwerkschicht- und Aktivierungsschichtzuordnung in den Speicher geladen wird. Leider bewirken klassische Optimierungsmethoden keine wesentlichen Änderungen an den frühen Rechenschichten neuronaler Netze, insbesondere bei Faltungs-Neuronalen Netzen.

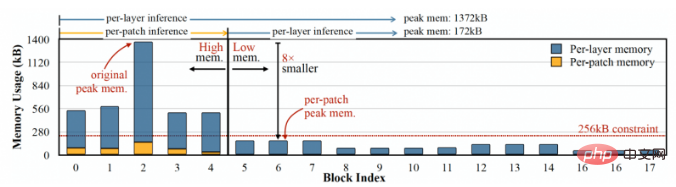

Dies führt zu einem Ungleichgewicht in der Größe der verschiedenen Schichten des Netzwerks und führt zum Problem der „Speicherspitze“: Selbst wenn das Netzwerk nach der Bereinigung schlanker wird, muss das Gerät, auf dem es ausgeführt wird, über denselben Speicher wie die größte Schicht verfügen. Beispielsweise erreicht die Berechnung der frühen Schichten im beliebten TinyML-Modell MobileNetV2 eine Speicherspitze von etwa 1,4 Megabyte, während spätere Schichten einen sehr geringen Speicherbedarf haben. Zum Ausführen des Modells benötigt das Gerät so viel Speicher wie das Modell seinen Spitzenwert erreicht. Da die meisten MCUs nur über ein paar hundert KB Speicher verfügen, können sie keine Standardversionen von MobileNetV2 ausführen.

MobileNetV2 ist ein für Edge-Geräte optimiertes neuronales Netzwerk, dessen Spitzenspeicher jedoch etwa 1,4 Megabyte beträgt, was es für viele Mikrocontroller unzugänglich macht.

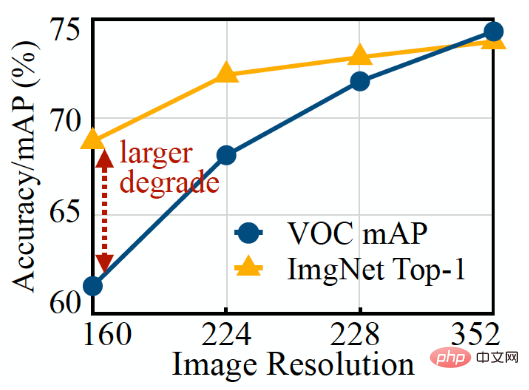

Eine weitere Möglichkeit, ein neuronales Netzwerk zu optimieren, besteht darin, die Eingabegröße des Modells zu reduzieren. Kleinere Eingabebilder erfordern kleinere CNNs, um Vorhersageaufgaben auszuführen. Allerdings stellt die Reduzierung der Eingabegröße ihre eigenen Herausforderungen dar und ist nicht für alle Computer-Vision-Aufgaben effektiv. Deep-Learning-Modelle zur Objekterkennung reagieren beispielsweise sehr empfindlich auf die Bildgröße und ihre Leistung lässt schnell nach, wenn die Eingabeauflösung abnimmt.

Aus der obigen Abbildung ist leicht zu erkennen, dass das Bildklassifizierungs-ML-Modell (orange Linie) die Auflösung leichter reduzieren kann als das Zielerkennungsmodell (blaue Linie).

3. MCUNetV2-Patch-basierte Inferenz

Um das Speicherengpassproblem von Faltungs-Neuronalen Netzen zu lösen, haben Forscher eine Deep-Learning-Architektur namens MCUNetV2 entwickelt, die ihre Speicherbandbreite an die Grenze des Mikrocontrollers anpassen kann. MCUNetV2 wurde auf der Grundlage früherer Ergebnisse derselben wissenschaftlichen Forschungsgruppe entwickelt, die angenommen und erfolgreich bei der NeurIPS 2020-Konferenz eingereicht wurden.

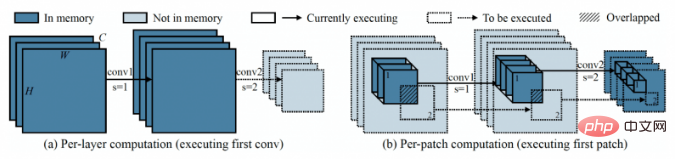

Die Hauptidee hinter MCUNetV2 ist „Patch-basierte Inferenz“, eine Technik, die den Speicherbedarf eines CNN reduziert, ohne seine Genauigkeit zu beeinträchtigen. Anstatt eine gesamte neuronale Netzwerkschicht in den Speicher zu laden, lädt und berechnet MCUNetV2 zu jedem Zeitpunkt kleinere Regionen oder „Patches“ der Schicht. Anschließend durchläuft es die Schicht Block für Block und kombiniert diese Werte, bis der Aktivierungsanteil der gesamten Schicht berechnet wird.

Die linke Seite der Abbildung zeigt das klassische Deep-Learning-System, das eine ganze Schicht berechnet, während die rechte Seite zeigt, wie MCUNetV2 jeweils einen Patch berechnet, wodurch der Speicherbedarf für die DL-Inferenz reduziert wird.

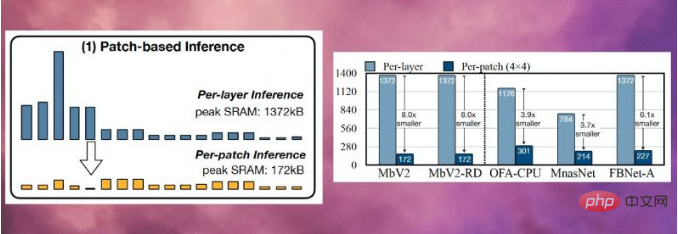

Da MCUNetV2 jeweils nur ein Neuron speichern muss, werden Speicherspitzen erheblich reduziert, ohne die Modellauflösung oder Parameter zu verringern. Experimente der Forscher zeigen, dass MCUNetV2 den Spitzenspeicher auf ein Achtel reduzieren kann.

MCUNetV2 kann die Speicherspitze von Deep-Learning-Modellen auf ein Achtel reduzieren.

Patch-basierte Inferenz führt auch zu einem Kompromiss beim Rechenaufwand und spart gleichzeitig Speicher. Forscher am Massachusetts Institute of Technology (MIT) und IBM haben herausgefunden, dass die gesamte Netzwerkberechnung in verschiedenen Architekturen um 10–17 % zunehmen kann, was offensichtlich nicht auf Mikrocontroller mit geringem Stromverbrauch zutrifft.

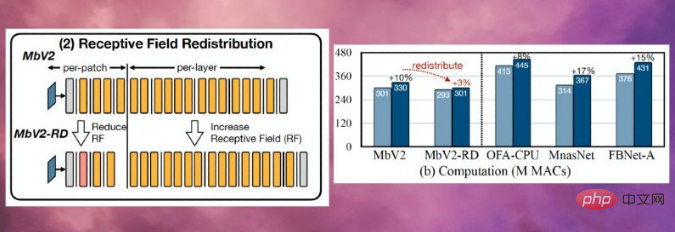

Um diese Einschränkung zu überwinden, verteilten die Forscher die „Empfangsfelder“ verschiedener Blöcke des neuronalen Netzwerks neu (Hinweis: In CNN entspricht ein Pixel in der Feature-Map der n-ten Ebene der Anzahl der Pixel im Eingabebild der ersten Schicht, d. h. Dies ist das Empfangsfeld dieser Schicht (als „RF“ bezeichnet). Bei CNN ist das Empfangsfeld der Bildbereich, der jederzeit verarbeitet werden kann. Größere Empfangsfelder erfordern größere Patches und Überlappungen zwischen den Patches. Dies führt natürlich zu einem höheren Rechenaufwand. Durch die Verkleinerung des Empfangsfelds in den ersten Blöcken des Netzwerks und die Erweiterung des Empfangsfelds in späteren Phasen konnten die Forscher den Rechenaufwand um mehr als zwei Drittel reduzieren.

Die Neuverteilung rezeptiver Felder trägt dazu bei, den Rechenaufwand von MCUNetV2 um mehr als zwei Drittel zu reduzieren.

Abschließend stellten die Forscher fest, dass die Optimierung von MCUNetV2 weitgehend von der ML-Modellarchitektur, der Anwendung sowie dem Arbeitsspeicher und der Speicherkapazität abhängt des Zielgeräts. Um die manuelle Abstimmung von Deep-Learning-Modellen für jedes Gerät und jede Anwendung zu vermeiden, verwendeten die Forscher die „Suche nach neuronalen Algorithmen“, einen Prozess, der maschinelles Lernen nutzt, um die Struktur neuronaler Netzwerke und die Inferenzplanung automatisch zu optimieren.

Die Forscher testeten Deep-Learning-Architekturen in verschiedenen Anwendungen auf mehreren Mikrocontroller-Modellen mit kleineren Speicherkapazitäten. Die Ergebnisse zeigen, dass MCUNetV2 andere TinyML-Technologien übertrifft und in der Lage ist, eine höhere Genauigkeit bei der Bildklassifizierung und Objekterkennung bei geringerem Speicherbedarf und geringerer Latenz zu erreichen.

Wie in der Abbildung unten gezeigt, verwenden Forscher MCUNetV2 mit Echtzeit-Personenerkennung, visuellen Weckwörtern und Gesichts-/Maskenerkennung.

Anmerkung des Übersetzers: Was hier gezeigt wird, ist nur ein Screenshot des Videos mit MCUNetV2, das auf der Website youtube.com angezeigt wird.

4. TinyML-Anwendungen

In einem Artikel aus dem Jahr 2018 mit dem Titel „Why the Future of Machine Learning is Tiny“ glaubt Softwareentwickler Pete Warden, dass maschinelles Lernen auf MCU äußerst wichtig ist. „Ich glaube, dass maschinelles Lernen auf kleinen Chips mit geringem Stromverbrauch ausgeführt werden kann, und diese Kombination wird eine Vielzahl von Problemen lösen, die wir derzeit nicht lösen können“, schrieb Worden.

Dank der Fortschritte bei Sensoren erhalten wir Daten aus der ganzen Welt und CPU-Fähigkeiten werden erheblich verbessert. Unsere Fähigkeit, diese Daten durch Modelle des maschinellen Lernens zu verarbeiten und zu nutzen, ist jedoch durch die Netzwerkkonnektivität und den Zugriff auf Cloud-Server eingeschränkt. Wie Worden sagte, sind Prozessoren und Sensoren energieeffizienter als Funksender wie Bluetooth und WLAN.

Worden schrieb: „Der physikalische Prozess des Verschiebens von Daten scheint viel Energie zu erfordern. Es scheint eine Regel zu sein, dass die für einen Vorgang erforderliche Energie proportional zur Distanz zum Senden der Bits ist. Die CPU und der Sensor benötigen zum Senden nur.“ Die Übertragung der Anzahl der Bits erfordert nur ein paar Millimeter und ist kostengünstig, während die Funkübertragung mehrere Meter oder mehr erfordert, um ein paar Datenbits zu senden, und das ist teuer ... Es ist klar, dass es ein riesiges potenzielles Marktpotenzial gibt, das darauf wartet, erschlossen zu werden Wir brauchen eine Technologie, die auf billigen Mikrocontrollern funktioniert, sehr wenig Energie verbraucht, auf Berechnungen statt auf Funk basiert und alle unsere verschwendeten Sensordaten in nützliche Daten umwandeln kann „Deep Learning“ wird die Lücke füllen. Wir können damit rechnen, dass TinyML in den kommenden Jahren seinen Weg in Milliarden von Mikrocontrollern in Haushalten, Büros, Krankenhäusern, Fabriken, Bauernhöfen, Straßen, Brücken und mehr findet und möglicherweise Anwendungen ermöglicht, die vorher einfach nicht möglich waren.

Originallink: https://thenextweb.com/news/tinyml-deep-learning-microcontrollers-syndication

Einführung des Übersetzers

Zhu Xianzhong, 51CTO-Community-Redakteur, 51CTO-Expertenblogger, Dozent, Computerlehrer an einer Universität in Weifang , Ein Veteran in der Welt der freiberuflichen Programmierung. In den Anfängen konzentrierte er sich auf verschiedene Microsoft-Technologien (stellte drei technische Bücher zu ASP.NET AJX und Cocos 2d-X zusammen). In den letzten zehn Jahren widmete er sich der Open-Source-Welt (vertraut mit beliebten Vollversionen). Stack-Webentwicklungstechnologie) und lernte OneNet/AliOS+Arduino/ESP32/Raspberry Pi und andere IoT-Entwicklungstechnologien sowie Scala+Hadoop+Spark+Flink und andere Big-Data-Entwicklungstechnologien kennen.

Das obige ist der detaillierte Inhalt vonWinziges maschinelles Lernen verspricht, Deep Learning in Mikroprozessoren zu integrieren. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Technologietrends, die Sie im Jahr 2023 im Auge behalten sollten

- Wie künstliche Intelligenz Rechenzentrumsteams neue Alltagsaufgaben beschert

- Können künstliche Intelligenz oder Automatisierung das Problem der geringen Energieeffizienz in Gebäuden lösen?

- OpenAI-Mitbegründer im Interview mit Huang Renxun: Die Argumentationsfähigkeiten von GPT-4 haben noch nicht die Erwartungen erfüllt

- Dank der OpenAI-Technologie übertrifft Bing von Microsoft Google im Suchverkehr