VSCode怎么配置verilog环境?下面本篇文章给大家推荐三个插件,让VSCode流畅编写verilog,三个插件可实现代码提示+自动例化+格式化。

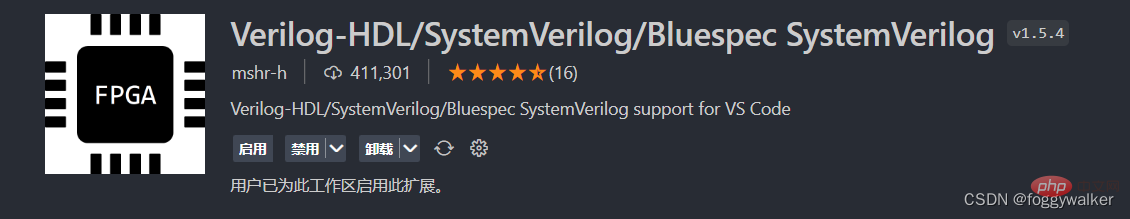

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

可实现功能:

- 语法高亮

- 自动例化

- 代码提示和跳转

- 自动补全

插件配置

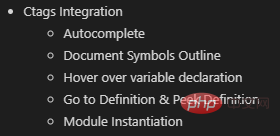

如Verilog HDL/SystemVerilog插件欢迎页的说明,支持Ctags功能:

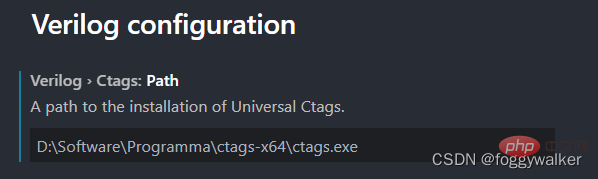

配置步骤:

下载最新版ctags,旧版的有些功能不够齐全;windows可选x64版本;

将ctags.exe的路径设置到系统环境变量中;

插件设置中配置ctags路径;

重启VSCode即可;

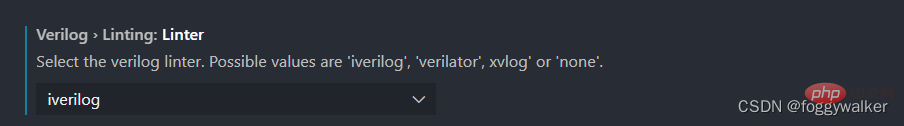

可以选择不同的编译器

包括:

- iverilog

- xvlog(vivado)

- modelsim

功能展示

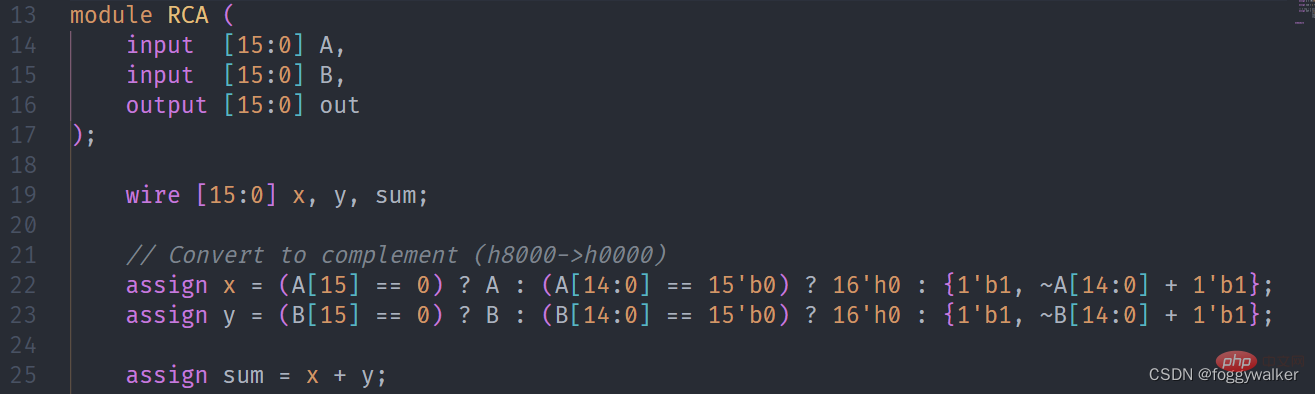

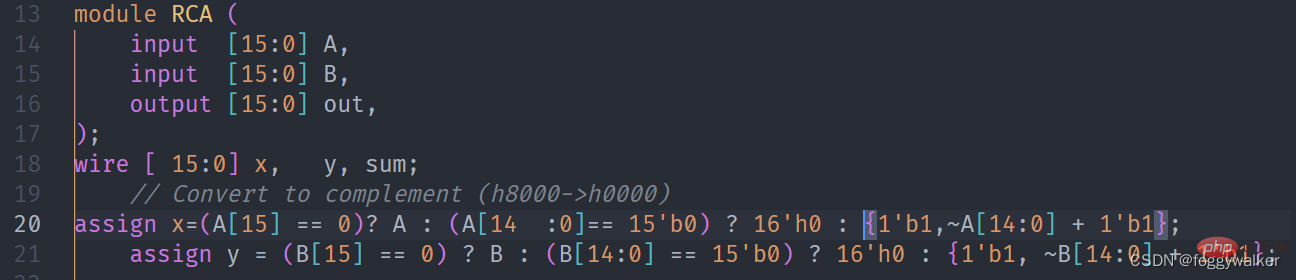

支持verilog、SV等语法高亮。

支持verilog、SV等语法高亮。

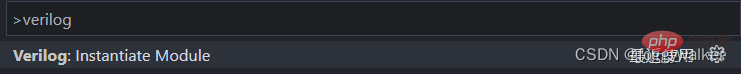

shift+ctrl+p输入verilog,可以直接自动例化模块。

鼠标放在信号上,就会有声明显示在悬浮框中。Ctrl+左键,点击信号名,自动跳转到声明处。光标放在信号处,右键选择查看定义(快捷键可自行绑定),可以在此处展开声明处的代码,用于修改声明十分方便,就不用再来回跳转了。

鼠标放在信号上,就会有声明显示在悬浮框中。Ctrl+左键,点击信号名,自动跳转到声明处。光标放在信号处,右键选择查看定义(快捷键可自行绑定),可以在此处展开声明处的代码,用于修改声明十分方便,就不用再来回跳转了。

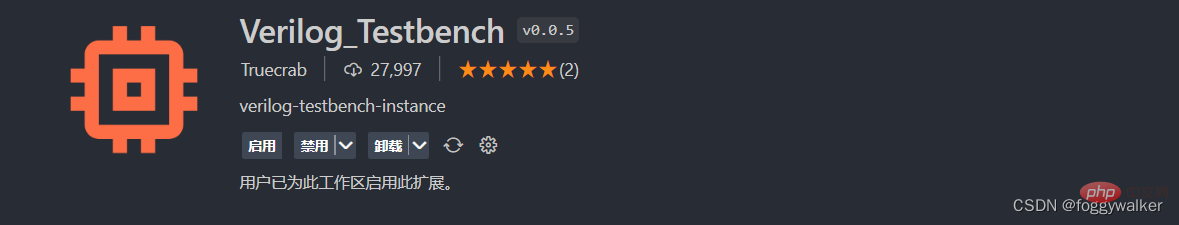

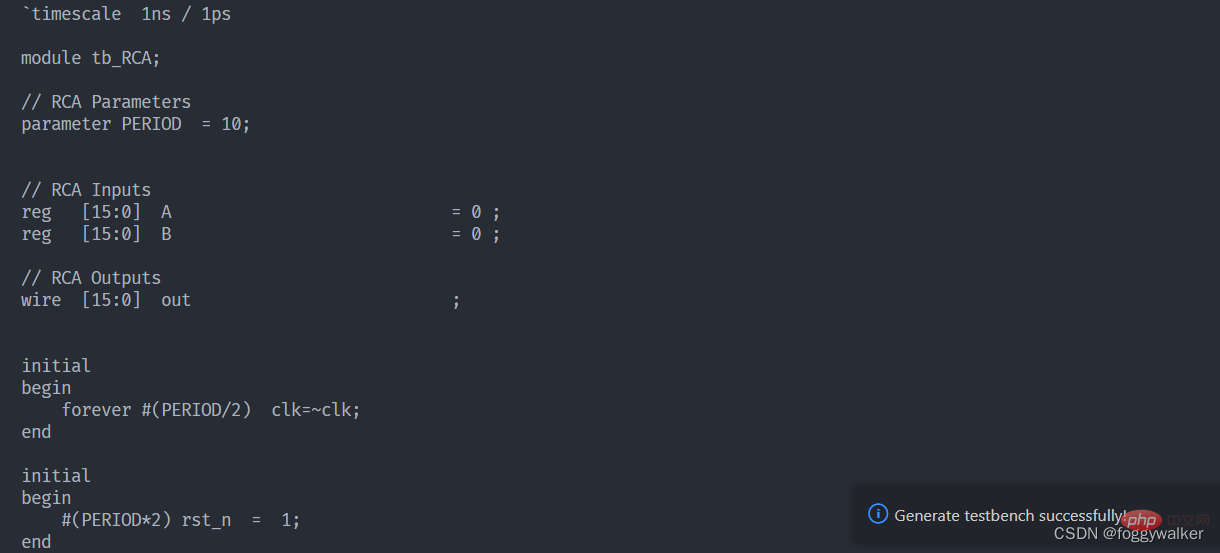

Verilog_Testbench

可实现功能:

- 自动生成testbench

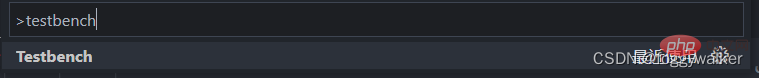

shift+ctrl+p输入testbench,可以直接生成tb。然后在终端复制即可。

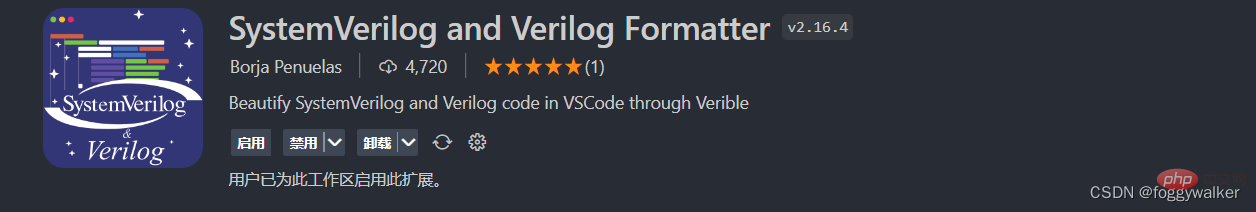

SystemVerilog and Verilog Formatter

这款工具由谷歌推出,同时支持Verilog和System Verilog,效果非常好,支持自定义的格式化参数也很丰富。个人认为比verilog format好用。

这款工具由谷歌推出,同时支持Verilog和System Verilog,效果非常好,支持自定义的格式化参数也很丰富。个人认为比verilog format好用。

可实现功能

- 自动格式化文件

- 自动格式化选定内容

- 自定义格式

自定义参数设置表

verible-verilog-format: usage: bazel-bin/verilog/tools/formatter/verible-verilog-format [options] 28897b20adb25fbae118a3f80f538dec [7970bcb837aac0da4981fe65dba2f39c]

To pipe from stdin, use '-' as 28897b20adb25fbae118a3f80f538dec.Flags from common/formatting/basic_format_style_init.cc:

--column_limit (Target line length limit to stay under when formatting.);

default: 100;

--indentation_spaces (Each indentation level adds this many spaces.);

default: 2;

--line_break_penalty (Penalty added to solution for each introduced line

break.); default: 2;

--over_column_limit_penalty (For penalty minimization, this represents the

baseline penalty value of exceeding the column limit. Additional penalty

of 1 is incurred for each character over this limit); default: 100;

--wrap_spaces (Each wrap level adds this many spaces. This applies when the

first element after an open-group section is wrapped. Otherwise, the

indentation level is set to the column position of the open-group

operator.); default: 4;

Flags from external/com_google_absl/absl/flags/parse.cc:

--flagfile (comma-separated list of files to load flags from); default: ;

--fromenv (comma-separated list of flags to set from the environment [use

'export FLAGS_flag1=value']); default: ;

--tryfromenv (comma-separated list of flags to try to set from the

environment if present); default: ;

--undefok (comma-separated list of flag names that it is okay to specify on

the command line even if the program does not define a flag with that

name); default: ;

Flags from verilog/formatting/format_style_init.cc:

--assignment_statement_alignment (Format various assignments:

{align,flush-left,preserve,infer}); default: infer;

--case_items_alignment (Format case items:

{align,flush-left,preserve,infer}); default: infer;

--class_member_variable_alignment (Format class member variables:

{align,flush-left,preserve,infer}); default: infer;

--compact_indexing_and_selections (Use compact binary expressions inside

indexing / bit selection operators); default: true;

--distribution_items_alignment (Aligh distribution items:

{align,flush-left,preserve,infer}); default: infer;

--enum_assignment_statement_alignment (Format assignments with enums:

{align,flush-left,preserve,infer}); default: infer;

--expand_coverpoints (If true, always expand coverpoints.); default: false;

--formal_parameters_alignment (Format formal parameters:

{align,flush-left,preserve,infer}); default: infer;

--formal_parameters_indentation (Indent formal parameters: {indent,wrap});

default: wrap;

--module_net_variable_alignment (Format net/variable declarations:

{align,flush-left,preserve,infer}); default: infer;

--named_parameter_alignment (Format named actual parameters:

{align,flush-left,preserve,infer}); default: infer;

--named_parameter_indentation (Indent named parameter assignments:

{indent,wrap}); default: wrap;

--named_port_alignment (Format named port connections:

{align,flush-left,preserve,infer}); default: infer;

--named_port_indentation (Indent named port connections: {indent,wrap});

default: wrap;

--port_declarations_alignment (Format port declarations:

{align,flush-left,preserve,infer}); default: infer;

--port_declarations_indentation (Indent port declarations: {indent,wrap});

default: wrap;

--port_declarations_right_align_packed_dimensions (If true, packed

dimensions in contexts with enabled alignment are aligned to the right.);

default: false;

--port_declarations_right_align_unpacked_dimensions (If true, unpacked

dimensions in contexts with enabled alignment are aligned to the right.);

default: false;

--struct_union_members_alignment (Format struct/union members:

{align,flush-left,preserve,infer}); default: infer;

--try_wrap_long_lines (If true, let the formatter attempt to optimize line

wrapping decisions where wrapping is needed, else leave them unformatted.

This is a short-term measure to reduce risk-of-harm.); default: false;

Flags from verilog/parser/verilog_parser.cc:

--verilog_trace_parser (Trace verilog parser); default: false;

Flags from verilog/tools/formatter/verilog_format.cc:

--failsafe_success (If true, always exit with 0 status, even if there were

input errors or internal errors. In all error conditions, the original

text is always preserved. This is useful in deploying services where

fail-safe behaviors should be considered a success.); default: true;

--inplace (If true, overwrite the input file on successful conditions.);

default: false;

--lines (Specific lines to format, 1-based, comma-separated, inclusive N-M

ranges, N is short for N-N. By default, left unspecified, all lines are

enabled for formatting. (repeatable, cumulative)); default: ;

--max_search_states (Limits the number of search states explored during line

wrap optimization.); default: 100000;

--show_equally_optimal_wrappings (If true, print when multiple optimal

solutions are found (stderr), but continue to operate normally.);

default: false;

--show_inter_token_info (If true, along with show_token_partition_tree,

include inter-token information such as spacing and break penalties.);

default: false;

--show_largest_token_partitions (If > 0, print token partitioning and then

exit without formatting output.); default: 0;

--show_token_partition_tree (If true, print diagnostics after token

partitioning and then exit without formatting output.); default: false;

--stdin_name (When using '-' to read from stdin, this gives an alternate

name for diagnostic purposes. Otherwise this is ignored.);

default: "c2f32e7e9231c3bf5bf9f218b5147824";

--verbose (Be more verbose.); default: false;

--verify_convergence (If true, and not incrementally formatting with

--lines, verify that re-formatting the formatted output yields no further

changes, i.e. formatting is convergent.); default: true;Try --helpfull to get a list of all flags or --help=substring shows help for

flags which include specified substring in either in the name, or description or

path.

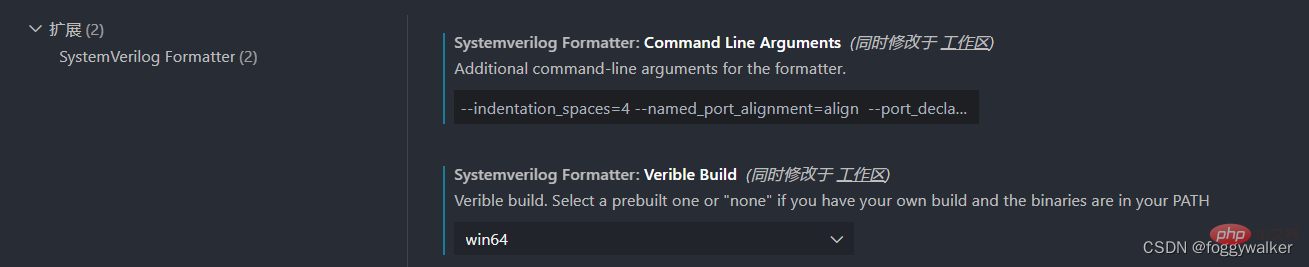

插件配置

如果是windows,systemverilogFormatter.veribleBuild设置为win64

systemverilogFormatter.commandLineArguments可以自定义格式化参数,下面放上我自己用的参数,可以实现大部分常用代码段实现对齐。

--indentation_spaces=4 --named_port_alignment=align --ort_declarations_alignment=align --module_net_variable_alignment=align

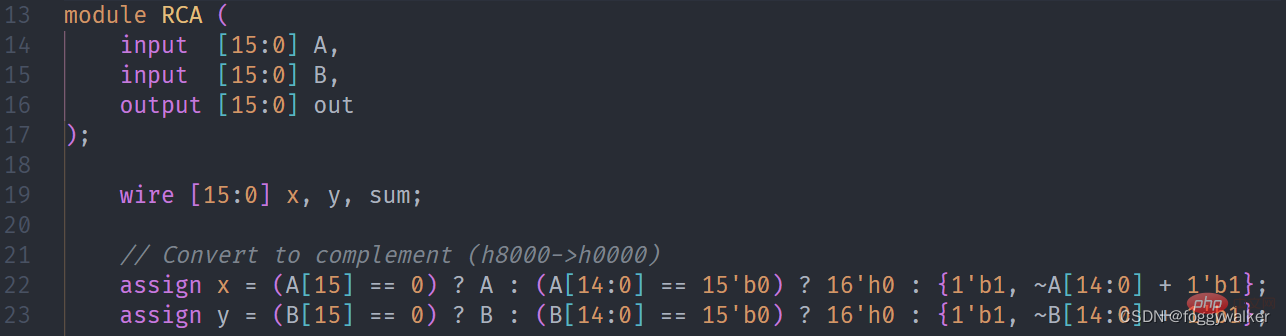

如何使用?如何格式化?

和vscode内置格式化一样,直接shift+ctrl+f就可以格式化文件,ctrl+k可以格式化选定内容。

值得注意的是,由于这个插件也是在完善中,还是存在部分问题的。

值得注意的是,由于这个插件也是在完善中,还是存在部分问题的。

比如else不会换行。

比如,存在语法问题,或者不能识别语法的时候,格式化会使用不了。这里我将最后一个端口加上","就不能格式化了。

比如,存在语法问题,或者不能识别语法的时候,格式化会使用不了。这里我将最后一个端口加上","就不能格式化了。

更多关于VSCode的相关知识,请访问:vscode基础教程!

以上是VSCode怎么配置verilog环境?代码提示+自动例化+格式化插件分享的详细内容。更多信息请关注PHP中文网其他相关文章!

在Visual Studio和VS代码之间进行选择:适合您的合适工具May 09, 2025 am 12:21 AM

在Visual Studio和VS代码之间进行选择:适合您的合适工具May 09, 2025 am 12:21 AMVisualStudio适合大型项目,VSCode适用于各种规模的项目。1.VisualStudio提供全面的IDE功能,支持多种语言,集成调试和测试工具。2.VSCode是轻量级编辑器,通过扩展支持多种语言,界面简洁,启动快。

Visual Studio:开发人员的强大工具May 08, 2025 am 12:19 AM

Visual Studio:开发人员的强大工具May 08, 2025 am 12:19 AMVisualStudio是微软开发的强大IDE,支持多种编程语言和平台。它的核心优势包括:1.智能代码提示和调试功能,2.集成开发、调试、测试和版本控制,3.可通过插件扩展功能,4.提供性能优化和最佳实践工具,帮助开发者提高效率和代码质量。

Visual Studio与代码:定价,许可和可用性May 07, 2025 am 12:11 AM

Visual Studio与代码:定价,许可和可用性May 07, 2025 am 12:11 AMVisualStudio和VSCode在定价、许可和可用性上的差异如下:1.定价:VSCode完全免费,而VisualStudio提供免费社区版和付费企业版。2.许可:VSCode采用灵活的MIT许可证,VisualStudio的许可根据版本不同而有所不同。3.可用性:VSCode跨平台支持,而VisualStudio在Windows上表现最佳。

视觉工作室:从代码到生产May 06, 2025 am 12:10 AM

视觉工作室:从代码到生产May 06, 2025 am 12:10 AMVisualStudio支持从代码编写到生产部署的全流程。1)代码编写:提供智能代码补全和重构功能。2)调试与测试:集成强大调试工具和单元测试框架。3)版本控制:与Git无缝集成,简化代码管理。4)部署与发布:支持多种部署选项,简化应用发布过程。

Visual Studio:查看许可景观May 05, 2025 am 12:17 AM

Visual Studio:查看许可景观May 05, 2025 am 12:17 AMVisualStudio提供了三种许可证类型:社区版、专业版和企业版。社区版免费,适合个人开发者和小型团队;专业版按年订阅,适用于需要更多功能的专业开发者;企业版价格最高,适用于大型团队和企业。选择许可证时需考虑项目规模、预算和团队协作需求。

终极摊牌:Visual Studio与代码May 04, 2025 am 12:01 AM

终极摊牌:Visual Studio与代码May 04, 2025 am 12:01 AMVisualStudio适合大型项目开发,而VSCode适用于各种规模的项目。 1.VisualStudio提供全面的开发工具,如集成调试器、版本控制和测试工具。 2.VSCode以其扩展性、跨平台和快速启动着称,适合快速编辑和小型项目开发。

Visual Studio与代码:比较两个IDEMay 03, 2025 am 12:04 AM

Visual Studio与代码:比较两个IDEMay 03, 2025 am 12:04 AMVisualStudio适合大型项目和Windows开发,而VSCode适用于跨平台和小型项目。1.VisualStudio提供全功能的IDE,支持.NET框架和强大调试工具。2.VSCode则是轻量级编辑器,强调灵活性和扩展性,适用于各种开发场景。

Visual Studio:比较免费和付费选项May 02, 2025 am 12:09 AM

Visual Studio:比较免费和付费选项May 02, 2025 am 12:09 AM选择VisualStudio时,免费版适合个人开发者和小型团队,付费版适合大型企业和需要高级功能的用户。1.免费的CommunityEdition提供基础开发工具,适用于个人和小型团队。2.付费的Professional和Enterprise版提供高级功能和支持,适用于商业环境和大型团队。

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

Video Face Swap

使用我们完全免费的人工智能换脸工具轻松在任何视频中换脸!

热门文章

热工具

安全考试浏览器

Safe Exam Browser是一个安全的浏览器环境,用于安全地进行在线考试。该软件将任何计算机变成一个安全的工作站。它控制对任何实用工具的访问,并防止学生使用未经授权的资源。

PhpStorm Mac 版本

最新(2018.2.1 )专业的PHP集成开发工具

SecLists

SecLists是最终安全测试人员的伙伴。它是一个包含各种类型列表的集合,这些列表在安全评估过程中经常使用,都在一个地方。SecLists通过方便地提供安全测试人员可能需要的所有列表,帮助提高安全测试的效率和生产力。列表类型包括用户名、密码、URL、模糊测试有效载荷、敏感数据模式、Web shell等等。测试人员只需将此存储库拉到新的测试机上,他就可以访问到所需的每种类型的列表。

禅工作室 13.0.1

功能强大的PHP集成开发环境

SublimeText3 英文版

推荐:为Win版本,支持代码提示!