Peranti teknologi

Peranti teknologi AI

AI Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?

Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?

Transistor dikenali sebagai "ciptaan terhebat abad ke-20."

Kemunculannya meletakkan asas untuk penghasilan litar bersepadu, mikropemproses dan ingatan komputer.

Pada tahun 1965, "Moore's Law" telah dicadangkan dan menjadi peraturan emas industri semikonduktor selama beberapa dekad.

Ia menunjukkan bahawa setiap 18~24 bulan, bilangan transistor yang dibungkus pada mikrocip akan berganda, dan prestasi cip akan meningkat dua kali ganda.

Walau bagaimanapun, dengan pengenalan berterusan nod proses baharu, bilangan atom dalam transistor semakin berkurangan. , dan pelbagai had melampau Fizikal menyekat perkembangan selanjutnya Undang-undang Moore.

Sesetengah orang berpendapat bahawa Undang-undang Moore sudah berakhir.

Oleh itu, untuk "menyelamatkan" Undang-undang Moore, jurutera perlu menukar struktur transistor, terus mengurangkan kawasan dan penggunaan kuasa, dan meningkatkan prestasinya.

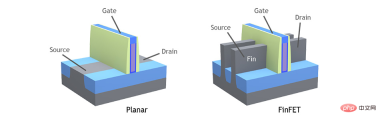

Pada separuh kedua abad ke-20, reka bentuk transistor planar (Transistor Planar) amat popular. Memasuki tahun 2010-an, peranti berbentuk sirip 3D secara beransur-ansur menggantikan reka bentuk rata.

Kini, struktur reka bentuk transistor yang benar-benar baharu, transistor get-all-around (GAA), ialah pengganti kepada FinFET dan akan memasuki pengeluaran.

Walau bagaimanapun, kita mesti melihat lebih jauh. Kerana walaupun dengan seni bina transistor baharu ini RibbonFET yang dicadangkan oleh Intel, keupayaan kami untuk mengurangkan saiz mempunyai had.

Percaya bahawa semikonduktor oksida logam pelengkap (CMOS) atau CFET (transistor kesan medan pelengkap) bertindan 3D akan menjadi sepuluh tahun akan datang untuk melanjutkan Hukum Moore Kunci kepada tahun.

Evolusi Transistor

Setiap Transistor Kesan Medan Semikonduktor Oksida Logam (MOSFET) mempunyai set komponen asas yang sama:

Timbunan pintu, kawasan saluran, sumber, longkang

Punca dan longkang didop secara kimia supaya bahawa mereka sama ada kaya dengan elektron mudah alih (jenis-n) atau kekurangannya (jenis-p). Rantau saluran mempunyai doping yang bertentangan dengan sumber dan longkang.

Dalam versi planar transistor dalam mikropemproses lanjutan sebelum 2011, susunan gerbang MOSFET berada tepat di atas kawasan saluran Unjurkan medan elektrik ke dalam saluran wilayah.

Menggunakan voltan yang cukup besar ke pintu gerbang (berbanding dengan sumber) akan membentuk lapisan pembawa cas mudah alih di kawasan saluran, supaya Biarkan arus mengalir antara punca dan longkang.

Untuk mengurangkan saiz reka bentuk transistor planar, "kesan saluran pendek" telah menjadi tumpuan ahli fizik .

Oleh kerana teknologi proses terus bertambah baik, lebar elektrod get dalam transistor semakin kecil dan kecil. Anda tahu, apabila pintu pagar lebih rendah daripada 20nm, arus akan menjadi tidak terkawal, dan arus sumber akan menembusi pintu dan terus sampai ke longkang.

Pada masa ini, "kebocoran" akan berlaku, yang akan menyebabkan penggunaan tenaga cip meningkat dengan mendadak.

Untuk menyelesaikan masalah ini, teknologi transistor FinFET baharu telah dicadangkan. Ia membalut pintu pagar di sekeliling saluran pada tiga sisi untuk memberikan kawalan statik yang lebih baik.

FinFET mengurangkan penggunaan kuasa kira-kira 50% pada tahap prestasi yang sama seperti seni bina satah generasi sebelumnya. FinFET juga bertukar lebih pantas, memberikan peningkatan prestasi sebanyak 37%.

Pada tahun 2011, Intel memperkenalkan FinFET pada nod 22nmnya dan menggunakannya dalam pengeluaran pemproses Teras generasi ketiga.

Sejak itu, FinFET telah menjadi kuda kerja Undang-undang Moore.

Walau bagaimanapun, kami juga kehilangan sesuatu apabila kami berpindah ke FinFET.

Dalam peranti planar, lebar transistor ditakrifkan oleh fotolitografi, jadi ia merupakan parameter yang sangat fleksibel.

Tetapi dalam FinFET, lebar transistor datang dalam kenaikan diskret, satu sirip ditambah pada satu masa. Sifat ini sering dipanggil kuantisasi sirip.

Walaupun FinFET mempunyai fleksibiliti, pengkuantitian sirip kekal sebagai kekangan reka bentuk yang penting. Peraturan reka bentuk yang mengelilinginya, dan keinginan untuk menambah lebih banyak sirip untuk meningkatkan prestasi, meningkatkan keseluruhan kawasan sel logik dan merumitkan timbunan antara sambungan yang menjadikan satu transistor menjadi litar logik yang lengkap.

Ia juga meningkatkan kapasiti transistor, dengan itu mengurangkan kelajuan pensuisannya. Oleh itu, sementara FinFET telah berkhidmat kepada kami dengan baik sebagai pekerja industri, pendekatan baharu yang lebih halus diperlukan.

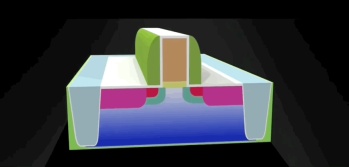

Pendekatan inilah yang menyebabkan ahli fizik mencipta transistor 3D yang akan datang, RibbonFET.

Dalam RibbonFET, pintu pagar mengelilingi kawasan saluran transistor untuk meningkatkan kawalan pembawa cas. Struktur baharu juga membolehkan prestasi yang lebih baik dan pengoptimuman yang lebih halus.

Secara khusus, pintu pagar mengelilingi saluran sepenuhnya, memberikan kawalan yang lebih ketat ke atas pembawa cas dalam saluran, yang kini diperbuat daripada bentuk reben Silikon skala nano.

Menggunakan reben nano (nanosheet) ini, sekali lagi mungkin untuk menggunakan fotolitografi untuk menukar lebar transistor seperti yang dikehendaki.

Setelah kekangan kuantisasi dialih keluar, adalah mungkin untuk menjana lebar bersaiz yang sesuai untuk aplikasi. Ini membolehkan kami mengimbangi kuasa, prestasi dan kos.

Lebih penting lagi, dengan menyusun dan beroperasi secara selari, peranti boleh memacu lebih arus, meningkatkan prestasi tanpa menambah kawasan.

Oleh itu, Intel percaya bahawa RibbonFET adalah pilihan terbaik untuk mencapai prestasi yang lebih tinggi pada kuasa yang munasabah.

Mereka akan memperkenalkan struktur RibbonFET pada proses Intel 20A pada tahun 2024.

CMOS tindanan 3D

Satu perkara yang mempunyai persamaan transistor planar, FinFET dan RibbonFET ialah semuanya Menggunakan teknologi CMOS, seperti yang dinyatakan sebelum ini, CMOS terdiri daripada transistor jenis-n dan jenis-p. Teknologi ini menjadi arus perdana pada tahun 1980-an kerana ia menarik arus yang jauh lebih sedikit daripada alternatif lain. Kurang arus bermakna frekuensi operasi yang lebih tinggi dan ketumpatan transistor yang lebih tinggi.

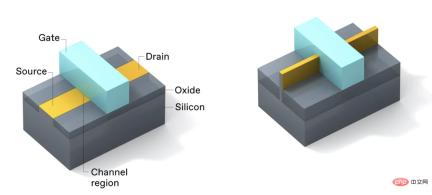

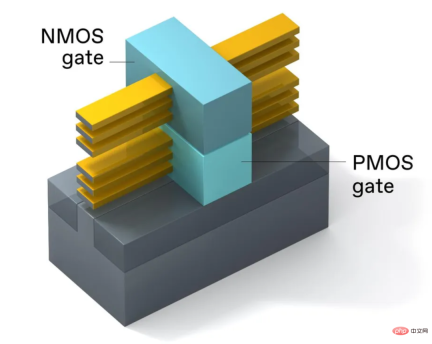

Sehingga kini, semua teknologi CMOS telah meletakkan pasangan standard transistor NMOS dan PMOS bersebelahan. Walau bagaimanapun, dalam ucaptama Persidangan Komponen Elektronik Antarabangsa IEEE (IEDM) 2019, konsep transistor "tindan 3D" telah dicadangkan, meletakkan transistor NMOS di atas transistor PMOS.

Pada IEDM 2020, penyongsang pertama reka bentuk litar logik menggunakan teknologi 3D ini telah dipersembahkan peranti. CMOS bertindan 3D dengan berkesan mengurangkan jejak penyongsang sebanyak separuh, menggandakan ketumpatan kawasan transistor dan seterusnya menolak had Hukum Moore.

Struktur CMOS bertindan 3D, meletakkan peranti PMOS di atas peranti NMOS, dengan jumlah keluasan yang sama dengan satu kawasan RibbonFET. Pintu NMOS dan PMOS menggunakan bahan logam yang berbeza

Untuk menggunakan CMOS bertindan 3D, banyak cabaran penyepaduan proses perlu diselesaikan, sebahagian daripadanya melibatkan pemprosesan dan pembuatan CMOS. had.

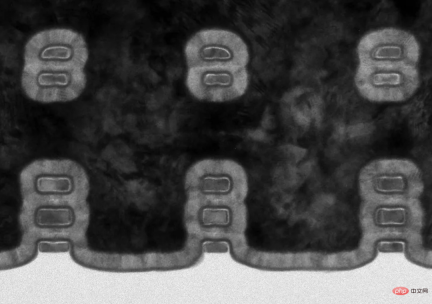

Bagaimana untuk mencapainya? Pembuatan CMOS 3D jajaran sendiri bermula dengan wafer silikon. Pada wafer, kami mendeposit lapisan demi lapisan silikon dan silikon germanium, struktur yang dipanggil "superlattice." Corak fotolitografi kemudiannya digunakan untuk memotong sebahagian daripada superlattice, meninggalkan struktur seperti sirip. Kristal superlattice menyediakan struktur sokongan yang kuat untuk proses pembangunan seterusnya.

Seterusnya, polisilikon "palsu" diletakkan pada kekisi super untuk melindungi bekas daripada operasi seterusnya. Langkah ini, yang dikenali sebagai proses dwi sumber/saliran bertindan secara menegak, menumbuhkan silikon dop fosforus pada kedua-dua hujung reben atas (tapak NMOS masa hadapan) manakala silikon terdop secara selektif pada nanoribbon bawah (tapak PMOS silikon germanium masa hadapan). Selepas itu, dielektrik diletakkan di sekeliling sumber kuasa untuk mengasingkannya antara satu sama lain melalui nyahcas elektrik.

Penyusun 3D dengan berkesan menggandakan ketumpatan transistor CMOS setiap milimeter persegi, ketumpatan sebenar bergantung pada kerumitan sel logik yang terlibat.

Akhirnya datanglah pembinaan pintu. Mula-mula keluarkan pintu palsu yang dipasang sebelum ini untuk mendedahkan reben nano silikon. Seterusnya, hanya germanium silikon yang terukir, melepaskan longgokan nanoribbon silikon selari, yang merupakan kawasan saluran transistor.

Kemudian lapisan penebat yang sangat nipis disalut pada keempat-empat sisi reben nano ini mempunyai pemalar dielektrik yang tinggi. Saluran nanoribbon adalah sangat kecil sehingga ia tidak boleh disalut secara kimia dengan cekap seperti transistor planar.

Gunakan logam untuk mengelilingi reben nano bawah untuk membentuk saluran berdop-p, dan reben nano atas untuk membentuk saluran berdop-n dengan reben nano yang lain. Dengan cara ini, susunan get dibina dan kedua-dua transistor dipasang.

Proses ini mungkin kelihatan rumit, tetapi ia lebih baik daripada teknik lain (susun 3D berurutan). Jika yang terakhir digunakan, peranti NMOS dan peranti PMOS dipasang pada wafer berasingan, dan kemudian kedua-duanya disatukan dan lapisan PMOS dipindahkan ke wafer NMOS. Kaedah tindanan 3D jajaran sendiri mempunyai langkah pemprosesan yang lebih sedikit dan boleh mengawal kos pembuatan dengan lebih ketat.

Dan yang lebih penting, kaedah penjajaran diri ini juga mengelakkan ralat penjajaran yang mungkin berlaku semasa menyambungkan dua wafer. Membuat semua sambungan yang diperlukan ke CMOS bertindan 3D adalah sangat mencabar. Sambungan kuasa akan diperlukan daripada timbunan peranti di bawah. Mengikut reka bentuk, peranti NMOS [atas] dan peranti PMOS [bawah] mempunyai sesentuh sumber/parit yang berasingan, tetapi kedua-dua peranti berkongsi pintu yang sama.

Perlu diperhatikan bahawa jarak menegak antara NMOS dan PMOS perlu dioptimumkan: jika ia terlalu pendek, ia akan meningkatkan kapasiti parasit, jika ia terlalu panjang, ia akan Meningkatkan rintangan sambung antara dua peranti. Sama ada situasi yang melampau akan menyebabkan litar menjadi perlahan dan menggunakan lebih banyak kuasa.

Banyak kajian reka bentuk, seperti yang dibentangkan oleh Pusat Penyelidikan TEL Amerika pada persidangan IEDM 2021, bercadang untuk menyediakan semua sambungan yang diperlukan dalam ruang terhad CMOS 3D, dan berbuat demikian tidak begitu ketara. Tingkatkan kawasan sel logik yang mereka bentuk. Penyelidikan menunjukkan bahawa terdapat banyak peluang untuk inovasi dalam mencari pilihan sambung terbaik.

Masa depan Undang-undang Moore

Dengan transistor kesan medan jalur dan CMOS 3D, kami mempunyai laluan yang jelas untuk meneruskan kehidupan Undang-undang Moore Laluan itu boleh dilanjutkan sekurang-kurangnya sehingga 2024 dan seterusnya.

Dalam temu bual 2005, Gordon Moore, pencadang Undang-undang Moore, mengakui bahawa "Saya terkejut dari semasa ke semasa dengan kemajuan yang telah dibuat. "

Dia berkata, “Ada masa di sepanjang jalan yang saya fikir kami telah sampai ke penghujungnya, tetapi jurutera kreatif kami datang dengan idea untuk mengatasi kesukaran. "

Apabila proses pembuatan transistor melalui FinFET, dan dengan pengoptimuman berterusan muncul era RibbonFET, dan akhirnya bergerak ke arah proses CMOS bertindan 3D, kita Ia adalah menjangkakan bahawa Encik Gordon Moore akan terkejut tidak lama lagi.

Atas ialah kandungan terperinci Inilah talian hayat transistor: CMOS bertindan 3D, adakah Undang-undang Moore akan diteruskan selama 10 tahun lagi?. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

7 Cara untuk Memisahkan Data Menggunakan Splitter Teks Langchain - Analytics VidhyaApr 19, 2025 am 10:11 AM

7 Cara untuk Memisahkan Data Menggunakan Splitter Teks Langchain - Analytics VidhyaApr 19, 2025 am 10:11 AMPemisahan Teks Langchain: mengoptimumkan input LLM untuk kecekapan dan ketepatan Artikel sebelumnya kami meliputi pemuat dokumen Langchain. Walau bagaimanapun, LLM mempunyai batasan saiz tetingkap konteks (diukur dalam token). Melebihi had ini memangkas data, comp

Kursus AI Generatif Percuma: Merintis Masa Depan InovasiApr 19, 2025 am 10:01 AM

Kursus AI Generatif Percuma: Merintis Masa Depan InovasiApr 19, 2025 am 10:01 AMAI Generatif: Merevolusi Kreativiti dan Inovasi Generatif AI sedang mengubah industri dengan mencipta teks, imej, muzik, dan dunia maya pada sentuhan butang. Impaknya merangkumi penyuntingan video, pengeluaran muzik, seni, hiburan, hea

Membuat model QA dengan Pengekod Kalimat Sejagat dan WikiqaApr 19, 2025 am 10:00 AM

Membuat model QA dengan Pengekod Kalimat Sejagat dan WikiqaApr 19, 2025 am 10:00 AMMemanfaatkan kekuatan model penyembuhan untuk menjawab soalan lanjutan Dalam dunia yang kaya dengan maklumat hari ini, keupayaan untuk mendapatkan jawapan yang tepat dengan serta-merta adalah yang paling penting. Artikel ini menunjukkan membina model soal jawab yang mantap (QA) menggunakan

Top 10 mesti membaca kertas penyelidikan pembelajaran mesinApr 19, 2025 am 09:53 AM

Top 10 mesti membaca kertas penyelidikan pembelajaran mesinApr 19, 2025 am 09:53 AMArtikel ini meneroka sepuluh penerbitan seminal yang telah merevolusikan kecerdasan buatan (AI) dan pembelajaran mesin (ML). Kami akan mengkaji kejayaan baru -baru ini dalam rangkaian saraf dan algoritma, menjelaskan konsep teras yang memacu AI moden. Th

Alat AI 11 teratas untuk menggantikan agensi SEO - Analytics VidhyaApr 19, 2025 am 09:49 AM

Alat AI 11 teratas untuk menggantikan agensi SEO - Analytics VidhyaApr 19, 2025 am 09:49 AMKenaikan AI di SEO: 11 Alat Teratas untuk Mengatasi Agensi SEO Kemajuan pesat AI telah membentuk semula landskap SEO. Perniagaan yang bertujuan untuk kedudukan enjin carian teratas memanfaatkan kuasa AI untuk mengoptimumkan strategi dalam talian mereka. Dari au

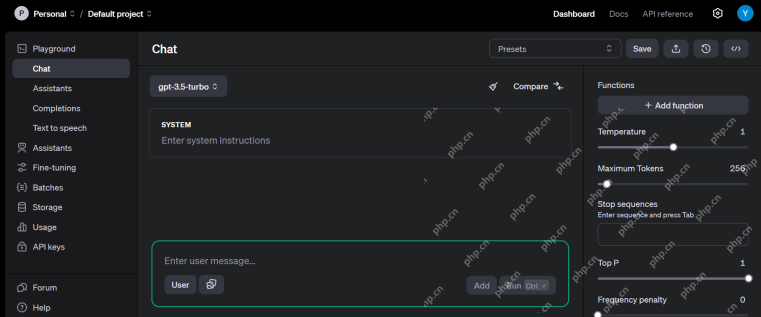

Taman permainan AI percuma untuk anda mencuba pada tahun 2025 - Analytics VidhyaApr 19, 2025 am 09:45 AM

Taman permainan AI percuma untuk anda mencuba pada tahun 2025 - Analytics VidhyaApr 19, 2025 am 09:45 AMMeneroka Taman Permainan AI percuma terbaik pada tahun 2024: Panduan Komprehensif Akses kepada alat dan platform yang betul adalah kunci untuk belajar dan berinovasi dalam bidang kecerdasan buatan yang sentiasa berubah (AI). Taman Permainan AI menawarkan peluang yang hebat

Panduan terperinci mengenai algoritma pengindeksan dalam pangkalan data vektorApr 19, 2025 am 09:41 AM

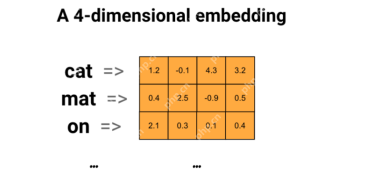

Panduan terperinci mengenai algoritma pengindeksan dalam pangkalan data vektorApr 19, 2025 am 09:41 AMPengenalan Pangkalan data vektor adalah pangkalan data khusus yang direka untuk menyimpan dan mengambil data vektor dimensi tinggi. Vektor ini mewakili ciri atau atribut titik data, mulai dari puluhan hingga ribuan dimensi bergantung pada

Apakah proses penyebaran terbalik? - Analytics VidhyaApr 19, 2025 am 09:40 AM

Apakah proses penyebaran terbalik? - Analytics VidhyaApr 19, 2025 am 09:40 AMPenyebaran yang stabil: Melancarkan keajaiban penyebaran terbalik Penyebaran yang stabil adalah model generatif yang kuat yang mampu menghasilkan imej berkualiti tinggi dari bunyi bising. Proses ini melibatkan dua langkah penting: proses penyebaran ke hadapan (terperinci dalam a sebelumnya a

Alat AI Hot

Undresser.AI Undress

Apl berkuasa AI untuk mencipta foto bogel yang realistik

AI Clothes Remover

Alat AI dalam talian untuk mengeluarkan pakaian daripada foto.

Undress AI Tool

Gambar buka pakaian secara percuma

Clothoff.io

Penyingkiran pakaian AI

AI Hentai Generator

Menjana ai hentai secara percuma.

Artikel Panas

Alat panas

mPDF

mPDF ialah perpustakaan PHP yang boleh menjana fail PDF daripada HTML yang dikodkan UTF-8. Pengarang asal, Ian Back, menulis mPDF untuk mengeluarkan fail PDF "dengan cepat" dari tapak webnya dan mengendalikan bahasa yang berbeza. Ia lebih perlahan dan menghasilkan fail yang lebih besar apabila menggunakan fon Unicode daripada skrip asal seperti HTML2FPDF, tetapi menyokong gaya CSS dsb. dan mempunyai banyak peningkatan. Menyokong hampir semua bahasa, termasuk RTL (Arab dan Ibrani) dan CJK (Cina, Jepun dan Korea). Menyokong elemen peringkat blok bersarang (seperti P, DIV),

SublimeText3 versi Inggeris

Disyorkan: Versi Win, menyokong gesaan kod!

SublimeText3 versi Cina

Versi Cina, sangat mudah digunakan

Dreamweaver Mac版

Alat pembangunan web visual

VSCode Windows 64-bit Muat Turun

Editor IDE percuma dan berkuasa yang dilancarkan oleh Microsoft