Rumah >Peranti teknologi >AI >Gambaran keseluruhan tiga seni bina cip arus perdana untuk pemanduan autonomi dalam satu artikel

Gambaran keseluruhan tiga seni bina cip arus perdana untuk pemanduan autonomi dalam satu artikel

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBke hadapan

- 2023-04-12 12:07:102379semak imbas

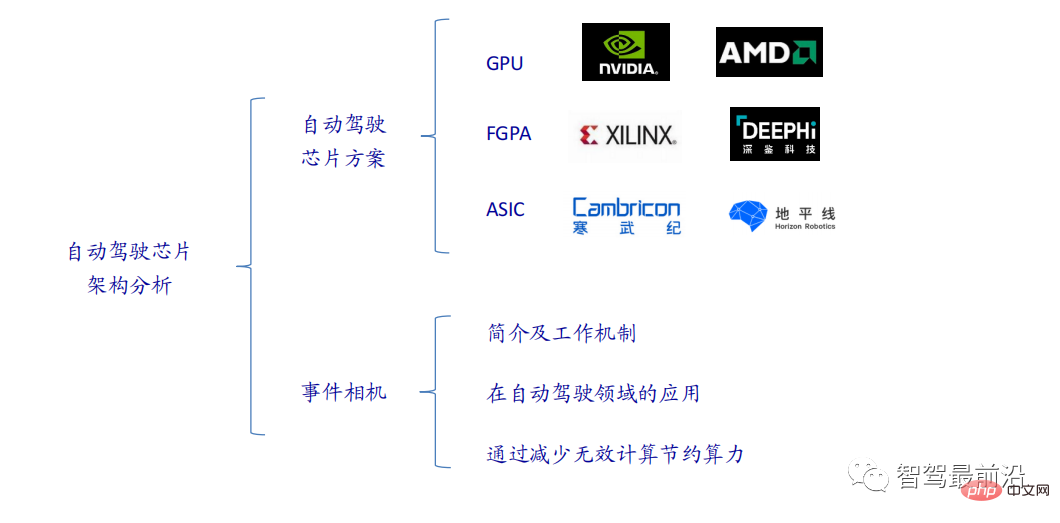

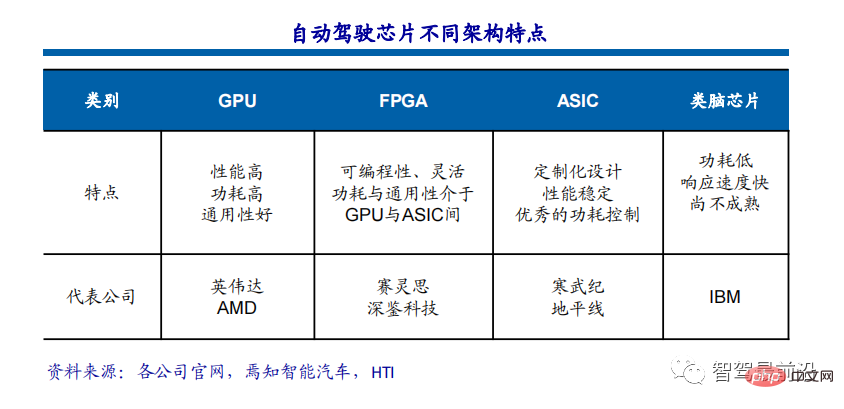

Cip AI arus perdana terbahagi terutamanya kepada tiga kategori, GPU, FPGA dan ASIC. Kedua-dua GPU dan FPGA adalah seni bina cip yang agak matang pada peringkat awal dan merupakan cip kegunaan umum. ASIC ialah cip yang disesuaikan untuk senario AI tertentu. Industri telah mengesahkan bahawa CPU tidak sesuai untuk pengkomputeran AI, tetapi ia juga penting dalam aplikasi AI.

Penyelesaian GPU

Perbandingan seni bina antara GPU dan CPU

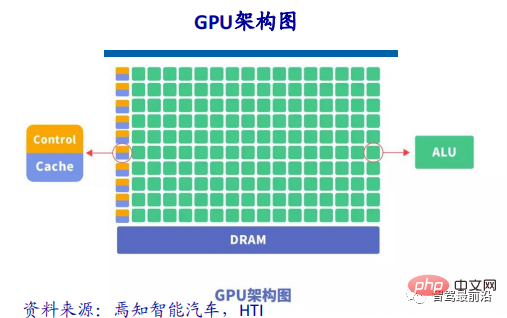

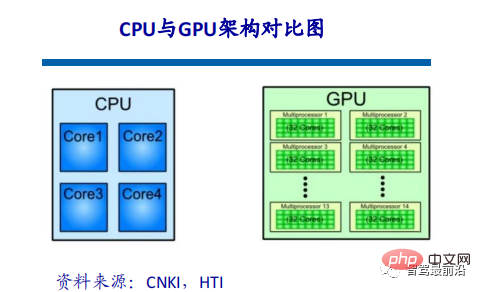

CPU mengikut seni bina von Neumann, terasnya ialah penyimpanan atur cara/data dan pelaksanaan bersiri. Oleh itu, seni bina CPU memerlukan sejumlah besar ruang untuk meletakkan unit storan (Cache) dan unit kawalan (Control Sebaliknya, unit pengkomputeran (ALU) hanya menduduki sebahagian kecil, jadi CPU terhad dalam besar-). pengkomputeran selari skala. Had adalah lebih baik dalam mengendalikan kawalan logik.

GPU (Unit Pemprosesan Grafik), iaitu pemproses grafik, ialah seni bina pengkomputeran selari berskala besar yang terdiri daripada sebilangan besar unit pengkomputeran Ia pada asalnya diasingkan daripada CPU khusus untuk diproses keselarian imej. Mengira data, direka untuk mengendalikan berbilang tugas pengkomputeran selari secara serentak. GPU juga mengandungi unit pengkomputeran asas, unit kawalan dan unit storan, tetapi seni bina GPU adalah sangat berbeza daripada gambar rajah seni binanya ditunjukkan di bawah.

Berbanding dengan CPU, kurang daripada 20% ruang cip CPU ialah ALU, manakala lebih daripada 80% ruang cip GPU ialah ALU. Iaitu, GPU mempunyai lebih banyak ALU untuk pemprosesan selari data.

Perbezaan antara GPU dan CPU

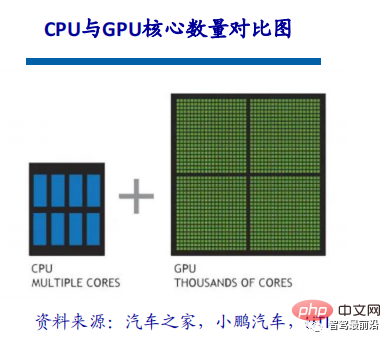

CPU Terdiri daripada beberapa teras yang dioptimumkan untuk pemprosesan bersiri berjujukan, GPU mempunyai seni bina pengkomputeran selari besar-besaran yang terdiri daripada beribu-ribu teras yang lebih kecil dan lebih cekap yang direka untuk pemprosesan serentak Direka untuk berbilang tugas.

Sebab CPU dan GPU sangat berbeza adalah kerana matlamat reka bentuk mereka yang berbeza masing-masing menyasarkan dua senario aplikasi yang berbeza. CPU memerlukan fleksibiliti yang kuat untuk mengendalikan pelbagai jenis data Pada masa yang sama, ia memerlukan pertimbangan logik dan memperkenalkan sejumlah besar lompatan cawangan dan pemprosesan gangguan. Semua ini menjadikan struktur dalaman CPU sangat kompleks. GPU menghadapi data berskala besar dengan jenis yang sangat bersatu dan tiada pergantungan antara satu sama lain dan persekitaran pengkomputeran tulen yang tidak perlu diganggu.

Pengenalan ringkas kepada teknologi pecutan GPU

Untuk pembelajaran mendalam, pecutan perkakasan semasa bergantung terutamanya pada penggunaan unit pemprosesan grafik. Berbanding dengan CPU tradisional, GPU mempunyai beberapa susunan magnitud lebih banyak kuasa pengkomputeran teras dan lebih mudah untuk melakukan pengiraan selari.

Seni bina berbilang teras GPU mengandungi beribu-ribu pemproses strim, yang boleh melaksanakan operasi secara selari dan memendekkan masa pengiraan model dengan banyak. Memandangkan NVIDIA, AMD dan syarikat lain terus mempromosikan sokongan seni bina selari berskala besar bagi GPU mereka, GPU untuk pengkomputeran am telah menjadi cara penting untuk mempercepatkan aplikasi selari.

Pada masa ini GPU telah berkembang ke peringkat yang agak matang. Menggunakan GPU untuk melatih rangkaian saraf dalam boleh memberikan permainan penuh kepada keupayaan pengkomputeran selari yang cekap bagi ribuan teras pengkomputeran Dalam senario di mana data latihan besar-besaran digunakan, masa yang dibelanjakan sangat dipendekkan dan lebih sedikit pelayan yang diduduki. Jika dioptimumkan dengan betul untuk rangkaian neural dalam yang betul, kad GPU boleh bersamaan dengan kuasa pengkomputeran berdozen atau bahkan ratusan pelayan CPU Oleh itu, GPU telah menjadi penyelesaian pilihan industri untuk latihan model pembelajaran mendalam.

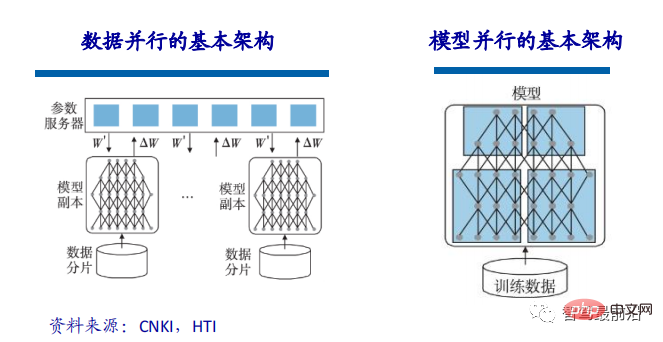

Apabila skala model terlatih agak besar, latihan model boleh dipercepatkan melalui keselarian data boleh membahagikan data latihan dan menggunakan berbilang contoh model untuk memproses berbilang ketulan data masa yang sama. Dalam pelaksanaan keselarian data, memandangkan model yang sama dan data yang berbeza digunakan untuk latihan, kesesakan yang mempengaruhi prestasi model terletak pada pertukaran parameter antara berbilang CPU atau berbilang GPU. Mengikut formula kemas kini parameter, kecerunan yang dikira oleh semua model perlu diserahkan kepada pelayan parameter dan dikemas kini kepada parameter yang sepadan Oleh itu, pembahagian kepingan data dan lebar jalur pelayan parameter mungkin menjadi kesesakan yang mengehadkan kecekapan keselarian data.

Selain keselarian data, keselarian model juga boleh digunakan untuk mempercepatkan latihan model. Keselarian model merujuk kepada pembahagian model besar kepada beberapa serpihan, yang masing-masing dipegang oleh beberapa unit latihan Setiap unit latihan bekerjasama antara satu sama lain untuk melengkapkan latihan model besar.

GPU dipercepatkan pengkomputeran

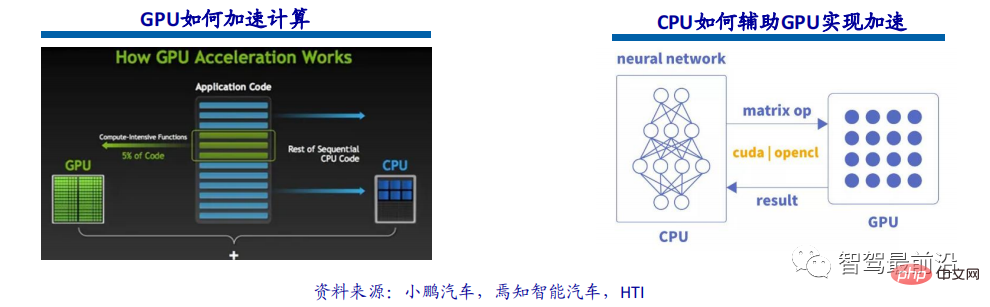

GPU dipercepatkan Pengkomputeran ialah penggunaan kedua-dua unit pemprosesan grafik (GPU) dan CPU untuk mempercepatkan aplikasi saintifik, analitikal, kejuruteraan, pengguna dan perusahaan. Pertama kali diperkenalkan oleh NVIDIA pada tahun 2007, pemecut GPU kini digunakan di seluruh dunia untuk menyokong pusat data cekap tenaga di makmal kerajaan, universiti, syarikat dan perusahaan kecil dan sederhana. GPU mempercepatkan aplikasi pada platform daripada kereta, telefon dan tablet kepada dron dan robot.

Pengkomputeran dipercepatkan GPU boleh menyampaikan prestasi aplikasi yang luar biasa dengan memunggah beban kerja daripada bahagian intensif pengiraan aplikasi ke GPU, sambil masih membiarkan CPU menjalankan kod program yang lain. Dari perspektif pengguna, aplikasi berjalan dengan ketara lebih pantas.

GPU pada masa ini hanya melaksanakan operasi pendaraban dan penambahan matriks selari mudah Pembinaan model rangkaian saraf dan penghantaran aliran data masih dilakukan pada CPU. Proses interaksi antara CPU dan GPU: dapatkan maklumat GPU, konfigurasi id GPU, muatkan parameter neuron ke GPU, GPU mempercepatkan pengiraan rangkaian saraf dan terima hasil pengiraan GPU.

Mengapa GPU sangat penting dalam bidang pemanduan autonomi

Salah satu kategori teknikal yang paling penting dalam teknologi pemanduan autonomi ialah pembelajaran mendalam Kecerdasan buatan berdasarkan seni bina pembelajaran mendalam kini telah digunakan secara meluas dalam penglihatan komputer, pemprosesan bahasa semula jadi, gabungan sensor, pengecaman sasaran, pemanduan autonomi dan. industri automotif yang lain, daripada syarikat permulaan pemanduan autonomi, syarikat Internet hingga OEM utama, sedang giat meneroka penggunaan GPU untuk membina rangkaian saraf untuk mencapai pemanduan autonomi muktamad.

Selepas kelahiran pengkomputeran dipercepatkan GPU, ia menyediakan seni bina pengkomputeran selari berbilang teras untuk data perusahaan, menyokong sumber data yang tidak dapat dikendalikan oleh seni bina CPU sebelumnya. Menurut perbandingan, untuk menyelesaikan tugas latihan pembelajaran mendalam yang sama, kos penggunaan kluster pengkomputeran GPU hanyalah 1/200 daripada kluster pengkomputeran CPU.

GPU ialah kunci kepada pemanduan autonomi dan pembelajaran mendalam

Sama ada ia membolehkan kereta melihat keadaan sekeliling yang sebenar -persekitaran masa dalam masa nyata, atau Merancang laluan dan tindakan pemanduan dengan pantas semuanya memerlukan tindak balas pantas otak kereta, yang menimbulkan cabaran besar kepada pengeluar perkakasan komputer Dalam proses pemanduan autonomi, pembelajaran mendalam atau algoritma kecerdasan buatan sentiasa diperlukan untuk menangani kemungkinan situasi yang tidak terhingga, dan kecerdasan buatan, Perkembangan pesat pembelajaran mendalam dan pemanduan tanpa pemandu telah membawa zaman kegemilangan pembangunan pengkomputeran GPU.

Satu lagi parameter penting GPU ialah keupayaan pengkomputeran titik terapung. Pengiraan titik terapung menggunakan titik perpuluhan terapung untuk mewakili nombor menggunakan nombor binari yang berbeza panjang, sepadan dengan nombor titik tetap. Apabila melelaran algoritma pemanduan autonomi, keperluan ketepatan adalah tinggi dan sokongan operasi titik terapung diperlukan.

Penyelesaian FPGA

definisi dan struktur cip FPGA

FPGA (Field-Programmable Gate Array), yang merupakan tatasusunan get boleh atur cara medan, ialah produk pembangunan selanjutnya berdasarkan peranti boleh atur cara seperti PAL, GAL dan CPLD. Ia muncul sebagai litar separa tersuai dalam bidang litar bersepadu khusus aplikasi, yang bukan sahaja menyelesaikan kekurangan litar tersuai, tetapi juga mengatasi kekurangan bilangan litar get yang terhad bagi peranti boleh atur cara asal.

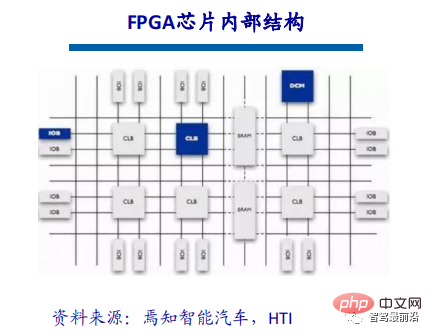

Cip FPGA dilengkapkan terutamanya oleh 6 bahagian, iaitu: unit input dan output boleh atur cara, unit logik boleh atur cara asas, pengurusan jam lengkap, RAM blok terbenam, sumber pendawaian yang kaya, Embedded low- unit fungsi tahap dan modul perkakasan khusus terbenam. FPGA arus perdana semasa masih berdasarkan teknologi jadual carian, yang jauh melebihi prestasi asas versi sebelumnya, dan menyepadukan modul teras keras (jenis ASIC) dengan fungsi biasa (seperti RAM, pengurusan jam dan DSP) .

Cara FPGA berfungsi

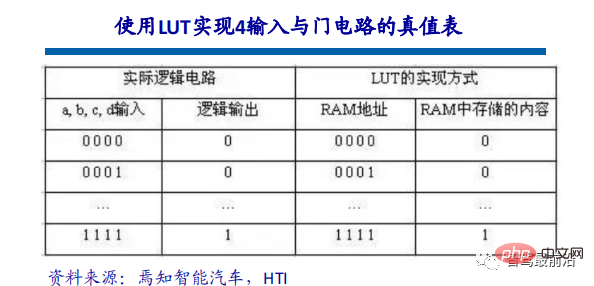

Disebabkan FPGA Ia perlu diprogramkan berulang kali, dan struktur asasnya untuk merealisasikan logik kombinasi tidak boleh diselesaikan melalui get NAND tetap seperti ASIC, tetapi hanya boleh menggunakan struktur yang mudah dikonfigurasikan berulang kali. Jadual carian boleh memenuhi keperluan ini pada masa ini, FPGA arus perdana semuanya menggunakan struktur jadual carian berdasarkan teknologi SRAM Terdapat juga beberapa FPGA gred tentera dan aeroangkasa yang menggunakan struktur jadual carian berdasarkan teknologi Flash atau fius dan antifus. Konfigurasi berulang FPGA dicapai dengan membakar fail untuk menukar kandungan jadual carian.

Look-Up-Table dirujuk sebagai LUT, dan LUT pada asasnya ialah RAM. Pada masa ini, LUT 4-input kebanyakannya digunakan dalam FPGA, jadi setiap LUT boleh dianggap sebagai RAM dengan baris alamat 4-bit. Apabila pengguna menerangkan litar logik melalui gambarajah skematik atau bahasa HDL, perisian pembangunan PLD/FPGA secara automatik akan mengira semua kemungkinan keputusan litar logik dan menulis jadual kebenaran (iaitu, hasilnya) ke dalam RAM terlebih dahulu. setiap kali isyarat dimasukkan Menjalankan operasi logik adalah bersamaan dengan memasukkan alamat, mencari jadual, mencari kandungan yang sepadan dengan alamat, dan kemudian mengeluarkannya.

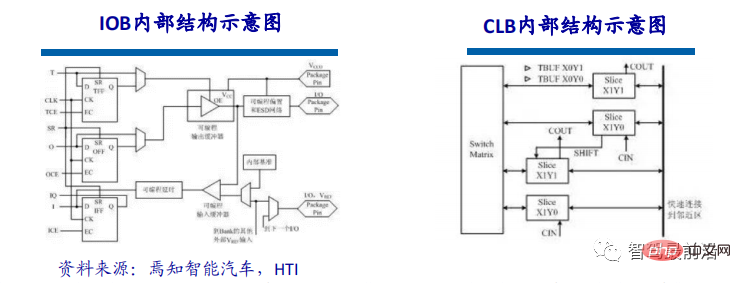

Unit input/output boleh atur cara, dirujuk sebagai unit I/O, ialah bahagian antara muka antara cip dan litar luaran, melengkapkan keperluan Pemanduan dan pemadanan yang berbeza untuk isyarat input/output di bawah ciri elektrik. I/O dalam FPGA dikelaskan kepada kumpulan, dan setiap kumpulan boleh menyokong piawaian I/O yang berbeza secara bebas. Melalui konfigurasi fleksibel perisian, ia boleh menyesuaikan diri dengan piawaian elektrik yang berbeza dan ciri fizikal I/O, melaraskan arus pemacu, dan menukar perintang tarik-turun dan tarik-turun. Pada masa ini, kekerapan port I/O semakin tinggi dan lebih tinggi, dan beberapa FPGA mewah boleh menyokong kadar data sehingga 2Gbps melalui teknologi daftar DDR.

CLB ialah unit logik asas dalam FPGA. Bilangan dan ciri sebenar CLB akan berbeza dari satu peranti ke peranti, tetapi setiap CLB mengandungi matriks suis boleh dikonfigurasikan yang terdiri daripada 4 atau 6 input, beberapa litar pemilihan (multiplexer, dsb.) dan komposisi flip-flop. Matriks suis sangat fleksibel dan boleh dikonfigurasikan untuk mengendalikan logik gabungan, daftar anjakan, atau RAM. Dalam peranti FPGA Xilinx, CLB terdiri daripada berbilang (biasanya 4 atau 2) Slice yang sama dan logik tambahan. Setiap modul CLB bukan sahaja boleh digunakan untuk melaksanakan logik gabungan dan logik jujukan, tetapi juga boleh dikonfigurasikan sebagai RAM teragih dan ROM teragih.

Pembunuh "teras" pemanduan autonomi

Segmen pasaran pemanduan autonomi dan sistem bantuan pemandu lanjutan (ADAS) sedang mengalami transformasi, meletakkan permintaan baharu dan kompleks pada keupayaan pengkomputeran dan sensor. FPGA mempunyai kelebihan unik yang tidak dapat dipadankan oleh penyelesaian cip lain dan merupakan pilihan terbaik untuk memenuhi pembangunan berterusan dan perubahan industri pemanduan autonomi. FPGA ialah teknologi khas dalam bidang cip Di satu pihak, ia boleh dikonfigurasikan berulang kali melalui alat perisian, dan sebaliknya, ia mempunyai antara muka IO yang kaya dan unit pengkomputeran. Oleh itu, FPGA boleh memproses keselarian saluran paip dan keselarian data pada masa yang sama mengikut keperluan khusus senario aplikasi, dan mempunyai kelebihan yang wujud dalam prestasi pengkomputeran yang tinggi, kependaman rendah dan penggunaan kuasa yang rendah.

FPGA mempunyai banyak kelebihan seperti daya pemprosesan yang tinggi, kecekapan tenaga yang tinggi dan pemprosesan masa nyata, yang sangat sesuai untuk keperluan teknikal pemanduan autonomi. Piawaian dan keperluan untuk aplikasi Advanced Assisted Driving Systems (ADAS) dan In-Vehicle Experience (IVE) berkembang pesat. Gabungan FPGA yang boleh diprogramkan semula dan portfolio produk gred automotif yang semakin berkembang membolehkan pereka automotif memenuhi keperluan reka bentuk dan terus mendahului industri automotif yang sentiasa berubah.

Platform yang lebih mudah disesuaikan

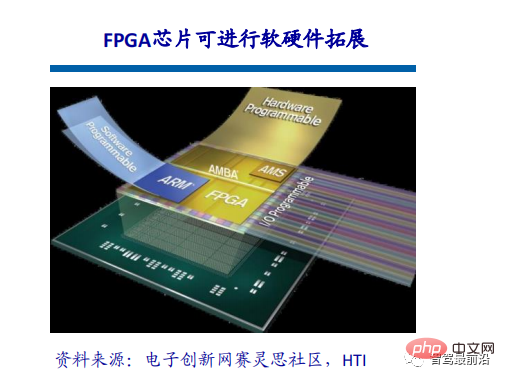

The nilai sebenar untuk cip pemanduan autonomi ialah penggunaan enjin pengkomputeran, iaitu perbezaan antara prestasi teori dan prestasi sebenar. FPGA mengandungi sejumlah besar pautan penghalaan serta sejumlah besar storan kecil. Gabungan sumber ini membolehkan pereka bentuk membuat rangkaian suapan data tersuai untuk enjin pengiraan mereka untuk tahap penggunaan yang lebih tinggi. Logik boleh atur cara menyediakan pelanggan dengan tahap fleksibiliti yang tinggi untuk menyesuaikan diri dengan perubahan keperluan bidang aplikasi yang muncul seperti ADAS dan pemanduan autonomi. Mengambil kesempatan daripada piawaian antara muka yang dipertingkatkan, inovasi algoritma dan teknologi penderia baharu memerlukan platform yang boleh disesuaikan yang boleh menyokong bukan sahaja perubahan perisian tetapi juga perubahan perkakasan, di mana cip FPGA cemerlang.

Cip FPGA boleh skala. Cip berskala mengubah jumlah logik boleh atur cara, kebanyakannya dalam pakej serasi pin. Ini bermakna pembangun boleh mencipta satu platform ECU untuk mengehoskan versi rendah, sederhana dan tinggi pakej ciri ADAS dan skala kos mengikut keperluan dengan memilih cip ketumpatan minimum yang diperlukan.

Penyelesaian yang berbeza

Cip FPGA membenarkan pembangun untuk mencipta penyelesaian pemprosesan yang unik dan berbeza yang boleh dioptimumkan untuk aplikasi atau penderia tertentu. Ini tidak boleh dilakukan dengan cip ASSP, malah yang menawarkan pemecut khusus adalah terhad dalam cara ia boleh digunakan dan tersedia kepada semua pesaing pada dasarnya. Pelanggan Xilinx lama, sebagai contoh, telah mencipta perpustakaan IP bernilai tinggi yang hanya boleh diakses oleh mereka, dan keupayaan tersebut boleh digunakan merentas pelbagai produk syarikat. Bermula dari nod 90nm, cip Xilinx telah sangat menjimatkan kos untuk aplikasi automotif volum tinggi, dengan lebih daripada 160 juta cip Xilinx digunakan dalam industri.

Penyelesaian ASIC

Takrifan dan ciri ASIC

Cip ASIC boleh dibahagikan kepada cip TPU, cip DPU dan cip NPU mengikut fungsi terminal yang berbeza. Antaranya, TPU ialah pemproses tensor khusus untuk pembelajaran mesin. Contohnya, Google telah membangunkan pemecut AI boleh atur cara untuk platform Tensorflow pada Mei 2016. Set arahan dalamannya boleh dijalankan apabila program Tensorflow berubah atau algoritma dikemas kini. DPU ialah Unit Pemprosesan Data, yang boleh menyediakan enjin untuk senario pengkomputeran seperti pusat data. NPU ialah pemproses rangkaian saraf yang mensimulasikan neuron manusia dan sinaps pada peringkat litar dan menggunakan set arahan pembelajaran mendalam untuk memproses terus neuron elektronik berskala besar dan data sinaptik.

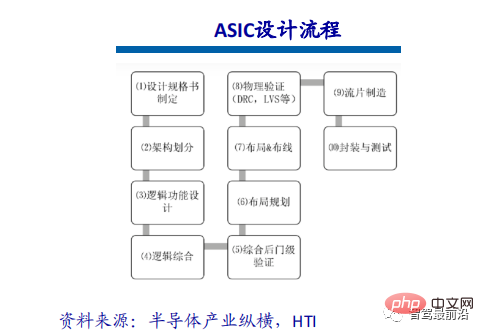

ASIC mempunyai dua kaedah reka bentuk: penyesuaian penuh dan separa penyesuaian. Penyesuaian penuh bergantung pada tenaga kerja dan kos masa yang besar untuk menyelesaikan keseluruhan proses reka bentuk litar bersepadu dengan cara yang bebas sepenuhnya Walaupun ia lebih fleksibel dan lebih baik daripada ASIC separa tersuai, kecekapan pembangunannya sangat rendah berbanding dengan separa tersuai.

Prestasi telah meningkat dengan ketara

Cip ASIC sangat sesuai untuk senario aplikasi kecerdasan buatan. Sebagai contoh, cip pertama NVIDIA, Tesla P100, direka dari awal untuk pembelajaran mendalam, mempunyai kelajuan pemprosesan data 12 kali ganda daripada siri GPU yang dilancarkan pada 2014. TPU cip tersuai Google untuk pembelajaran mesin telah meningkatkan prestasi perkakasan ke tahap yang setara dengan cip semasa tujuh tahun selepas pembangunan Undang-undang Moore. Sama seperti CPU mengubah komputer besar masa lalu, cip ASIC kecerdasan buatan juga akan mengubah wajah peranti perkakasan AI hari ini dengan ketara. Contohnya, AlphaGo yang terkenal menggunakan kira-kira 170 unit pemprosesan grafik (GPU) dan 1,200 unit pemprosesan pusat (CPU) Peranti ini memerlukan bilik komputer, penyaman udara berkuasa tinggi dan berbilang pakar untuk penyelenggaraan sistem. Dan jika semua cip khusus digunakan, kemungkinan besar ia hanya memerlukan ruang sebesar kotak penyimpanan biasa, dan penggunaan kuasa akan dikurangkan dengan banyak.

Laluan teknologi ASIC adalah terhad dan terbuka, dan syarikat cip perlu membangun untuk rangkaian arus perdana, model dan pengendali yang berkaitan dengan pemanduan. Di bawah prestasi yang sama, kawasan cip lebih kecil, kosnya lebih rendah, dan penggunaan kuasa lebih rendah. Laluan teknologi ASIC akan mempunyai potensi besar pada masa hadapan Memilih laluan ASIC tidak bermakna membangunkan ASIC yang berbeza untuk model yang berbeza atau melakukan pengesahan yang berbeza. Oleh kerana fungsi yang model berbeza perlu dilaksanakan adalah lebih kurang sama, dan cip mempunyai akses terhad kepada model dan pengendali, lelaran pantas algoritma tidak akan menjejaskan sokongan cip untuk fungsi lapisan atas. Pengeluar kereta bekerjasama dengan syarikat reka bentuk cip untuk melaksanakan penyesuaian yang berbeza, atau pilihan yang lebih baik. Kerana walaupun dengan penyesuaian yang berbeza, 50% bahagian dalaman cip adalah universal. Syarikat reka bentuk cip boleh menjalankan reka bentuk yang berbeza berdasarkan versi asal untuk mencapai beberapa fungsi yang berbeza.

Perbandingan penyelesaian seni bina arus perdana: tiga seni bina arus perdana

FPGA ialah produk yang dibangunkan lagi berdasarkan peranti boleh atur cara seperti PAL dan GAL . Ia muncul sebagai litar separa tersuai dalam bidang litar bersepadu khusus aplikasi, yang bukan sahaja menyelesaikan kekurangan litar tersuai, tetapi juga mengatasi kekurangan bilangan litar get yang terhad bagi peranti boleh atur cara asal. Kelebihan: pengaturcaraan tanpa had, kependaman rendah, keselarian saluran paip dan keselarian data, prestasi masa nyata terkuat dan kefleksibelan tertinggi. Kelemahan: Sukar untuk dibangunkan, hanya sesuai untuk operasi titik tetap, dan agak mahal.

Unit pemprosesan grafik (GPU), juga dikenali sebagai teras paparan, pemproses visual, cip paparan, ialah sejenis pemproses yang digunakan khas dalam komputer peribadi, stesen kerja, konsol permainan dan beberapa peranti mudah alih (seperti tablet), telefon mudah alih, dsb.) yang melakukan operasi berkaitan imej dan grafik. Kelebihan: Ia menyediakan struktur asas pengkomputeran selari berbilang teras, dan mempunyai bilangan teras yang sangat besar, yang boleh menyokong pengkomputeran selari sejumlah besar data dan mempunyai keupayaan pengkomputeran titik terapung yang lebih tinggi. Kelemahan: keupayaan kawalan pengurusan (paling lemah), penggunaan kuasa (paling tinggi).

ASIC, atau litar bersepadu khusus aplikasi, merujuk kepada litar bersepadu yang direka dan dihasilkan sebagai tindak balas kepada keperluan pengguna khusus dan keperluan sistem elektronik tertentu. Pada masa ini, salah satu cara paling popular untuk mereka bentuk ASIC ialah dengan CPLD (Complex Programmable Logic Device) dan FPGA (Field Programmable Logic Array). Kelebihan: Sebagai produk teknologi litar bersepadu dan teknologi mesin atau sistem lengkap pengguna tertentu, ia mempunyai saiz yang lebih kecil, berat yang lebih ringan, penggunaan kuasa yang lebih rendah, kebolehpercayaan yang lebih baik, prestasi yang lebih baik dan kerahsiaan berbanding dengan litar bersepadu tujuan umum. pengurangan kos dan kelebihan lain. Kelemahan: Fleksibiliti tidak mencukupi dan lebih mahal daripada FPGA.

Had teori kuasa pengkomputeran sahaja: Kuasa pengkomputeran TOPS tidak sepenuhnya sama dengan prestasi sebenar

Dengan peningkatan ADAS dan teknologi pemanduan autonomi, serta pendalaman beransur-ansur kereta yang ditakrifkan perisian, permintaan untuk kuasa pengkomputeran dan keupayaan pemprosesan data besar-besaran dalam kereta pintar telah melonjak, dan "timbunan" cip kereta tradisional mempunyai "Penyelesaian itu tidak lagi dapat memenuhi keperluan kuasa pengkomputeran pemanduan autonomi. Cip akhirnya berfungsi untuk platform pengkomputeran dalam kenderaan syarikat kereta Dalam kes "kereta yang ditakrifkan perisian", menyelesaikan masalah sokongan platform pengkomputeran sistem pemanduan pintar tidak boleh dicapai hanya dengan menyusun kuasa pengkomputeran.

Cip ialah peringkat untuk perisian Piawaian untuk mengukur kualiti cip bergantung pada sama ada perisian pada cip boleh memaksimumkan fungsinya kuasa pengkomputeran dan perisian. Apabila membandingkan dua cip dengan kuasa pengkomputeran yang sama, cip yang membolehkan perisian berjalan dengan lebih cekap ialah "cip yang baik". Faktor paling penting yang menentukan nilai sebenar kuasa pengkomputeran ialah lebar jalur memori (SRAM dan DRAM), serta kekerapan operasi sebenar (iaitu, voltan atau suhu bekalan), dan saiz kelompok algoritma.

Kuasa pengkomputeran cip tunggal TOPS ialah penunjuk utama, tetapi ia bukan satu-satunya Pemanduan Autonomi ialah sistem kompleks yang memerlukan kerjasama tepi awan dengan kenderaan. Oleh itu, sebagai tambahan kepada teras, persaingannya juga termasuk sinergi perisian dan perkakasan, platform, rantai alat, dsb. Pengembangan kuasa pengkomputeran cip dan perkakasan terbenam yang tidak terhingga tidak akan menjadi trend masa depan, dan perkakasan juga perlu sepadan dengan keadaan sebenar. Di sebalik yang tinggi adalah masalah penggunaan kuasa yang tinggi dan penggunaan yang rendah.

Pengenalan kepada kamera acara

Pengenalan dan mekanisme kerja

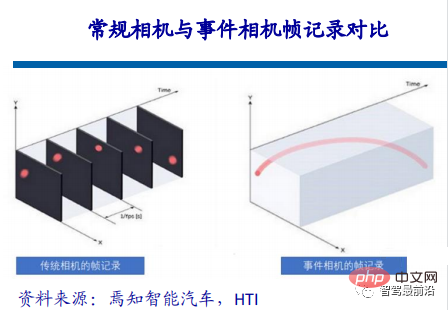

Kamera acara diilhamkan oleh penglihatan mata manusia dan haiwan, juga dipanggil retina silikon oleh sesetengah orang. Penglihatan biologi hanya sensitif kepada kawasan yang mengalami perubahan, dan kamera acara menangkap kejadian atau perubahan. ,

Dalam medan visual tradisional, maklumat yang dikembalikan oleh kamera disegerakkan Apa yang dipanggil penyegerakan bermakna pada masa tertentu t, kamera akan mendedahkan dan menggabungkan semua piksel. pada masa ini Isikan matriks dan hantar semula untuk menghasilkan foto. Semua piksel dalam foto sepadan dengan momen yang sama. Bagi video, ia hanyalah gambar banyak bingkai Selang masa antara gambar bersebelahan boleh menjadi besar atau kecil Ini adalah kadar bingkai (kadar bingkai), juga dipanggil kelewatan masa (latensi masa). Kamera acara adalah serupa dengan otak dan mata manusia, melangkau latar belakang yang tidak berkaitan dan mengesan secara langsung inti adegan, mencipta peristiwa tulen dan bukannya data.

Mekanisme kerja kamera acara ialah apabila kecerahan piksel tertentu berubah kepada ambang tertentu, kamera akan mengembalikan acara dalam format di atas, yang mana dua yang pertama item ialah koordinat piksel acara, item ketiga ialah cap masa acara dan item terakhir ialah kekutuban (kekutuban) 0, 1 (atau -1, 1), yang mewakili sama ada kecerahan adalah dari rendah ke tinggi atau dari tinggi ke rendah.

Dengan cara ini, selagi satu nilai piksel berubah dalam keseluruhan medan pandangan kamera, satu peristiwa akan dikembalikan secara tidak segerak (tidak kira selang masa yang kecil adalah) Ia adalah mustahil untuk menjadi serentak sepenuhnya), jadi cap masa peristiwa adalah berbeza Kerana pemulangan adalah mudah, berbanding dengan kamera tradisional, ia mempunyai ciri kependaman rendah dan boleh menangkap perubahan piksel dalam selang masa yang singkat kelewatan adalah mikro.

Aplikasi dalam bidang pemanduan autonomi

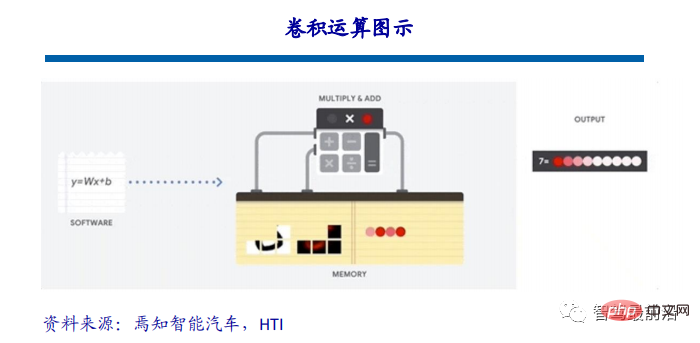

Algoritma pengecaman visual yang digunakan dalam bidang pemanduan autonomi hari ini pada asasnya adalah berdasarkan rangkaian neural konvolusi Operasi algoritma visual pada asasnya adalah operasi konvolusi. Pengiraan sebegini tidaklah rumit pada asasnya, ia hanya melibatkan operasi tambah, tolak, darab dan bahagi iaitu sejenis operasi darab, pengumpulan dan pengumpulan. Walau bagaimanapun, operasi mudah sedemikian wujud dalam kuantiti yang banyak dalam rangkaian saraf konvolusi, yang meletakkan permintaan yang tinggi terhadap prestasi pemproses.

Ambil ResNet-152 sebagai contoh Ini ialah rangkaian saraf konvolusi 152 lapisan Jumlah pengiraan yang diperlukan untuk memproses imej 224*224 adalah lebih kurang 22.6 bilion kali rangkaian ini ingin memproses kamera 1080P 30 bingkai, kuasa pengkomputeran yang diperlukannya adalah setinggi 33 trilion kali sesaat, yang sangat besar.

Jimat kuasa pengkomputeran dengan mengurangkan pengiraan tidak sah

99% data visual dalam bidang pemanduan autonomi adalah latar belakang yang tidak berguna dalam pemprosesan AI. Sebagai contoh, apabila mengesan probe hantu, kawasan yang diubah hanyalah sebahagian kecil, tetapi pemprosesan visual tradisional masih perlu memproses 99% kawasan latar belakang yang tidak berubah, yang bukan sahaja membazirkan banyak kuasa pengkomputeran, tetapi juga membuang masa. . Atau jika ada berlian di dalam kerikil, cip AI dan kamera tradisional perlu mengenal pasti setiap butiran pasir dan menyaring berlian, tetapi manusia boleh mengesan berlian dengan hanya melihat cip dan tradisional AI kamera mengambil masa lebih daripada manusia 100 kali atau 1000 kali.

Selain kelebihan maklumat berlebihan yang dikurangkan dan hampir tiada kelewatan, kelebihan kamera acara juga disebabkan oleh kependaman yang rendah Apabila merakam objek berkelajuan tinggi, kamera tradisional akan kabur kerana tempoh masa pendedahan , manakala kamera acara jarang dilakukan oleh kamera. Di samping itu, kamera acara mempunyai julat dinamik yang benar-benar tinggi Disebabkan oleh ciri-ciri kamera acara, kamera tradisional akan menjadi "buta" dalam persekitaran dengan keamatan cahaya yang kuat atau lemah, tetapi perubahan piksel masih wujud, jadi kamera acara boleh. masih melihat sesuatu dengan jelas.

Atas ialah kandungan terperinci Gambaran keseluruhan tiga seni bina cip arus perdana untuk pemanduan autonomi dalam satu artikel. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Artikel berkaitan

Lihat lagi- Aliran teknologi untuk ditonton pada tahun 2023

- Cara Kecerdasan Buatan Membawa Kerja Baharu Setiap Hari kepada Pasukan Pusat Data

- Bolehkah kecerdasan buatan atau automasi menyelesaikan masalah kecekapan tenaga yang rendah dalam bangunan?

- Pengasas bersama OpenAI ditemu bual oleh Huang Renxun: Keupayaan penaakulan GPT-4 belum mencapai jangkaan

- Bing Microsoft mengatasi Google dalam trafik carian terima kasih kepada teknologi OpenAI