Rumah >Operasi dan penyelenggaraan >operasi dan penyelenggaraan linux >apa itu linux vcs

apa itu linux vcs

- 藏色散人asal

- 2023-04-10 10:55:391590semak imbas

Linux vcs ialah simulator verilog yang disusun, alat yang digunakan untuk mensimulasikan dan melihat bentuk gelombang; ia serupa dengan alatan seperti modelsim dan questasim di bawah tingkap, serta operasi simulasi quartus dan vivado.

Persekitaran pengendalian tutorial ini: sistem linux5.9.8, komputer Dell G3.

Apakah itu linux vcs?

Penggunaan asas alatan VCS

VCS ialah alatan yang digunakan untuk mensimulasikan dan melihat bentuk gelombang di bawah Linux adalah serupa dengan alatan seperti modelsim dan questasim di bawah Windows, serta operasi simulasi quartus dan vivado.

1.Arahan asas untuk vcs

Imbuhan arahan biasa untuk vcs

| Arahan | Maksud | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

-l readme.log |

Digunakan untuk meletakkan maklumat yang dijana oleh penyusunan dalam fail log | ||||||||||||||||||||

+v2k |

adalah untuk membuat VCS Piawaian yang serasi sebelum verilog 2001 | ||||||||||||||||||||

-debug_all |

Digunakan untuk menjana fail yang diperlukan untuk nyahpepijat | ||||||||||||||||||||

-f verilog_file.f |

Boleh menyusun semua kod sumber dalam fail .f | ||||||||||||||||||||

-R

|

Jalankan serta-merta selepas penyusunan, iaitu, laksanakan serta-merta selepas penyusunan selesai

|

||||||||||||||||||||

-Mupdate

|

Apabila fail sumber diubah suai, hanya fail **.v** yang diubah suai akan dikompilasi semula untuk menjimatkan masa penyusunan. | ||||||||||||||||||||

-sverilog |

Hidupkan sokongan untuk Systemverilog dan susun Systemverilog

|

||||||||||||||||||||

-timescale=1ns/1ns |

Tetapkan ketepatan simulasi | ||||||||||||||||||||

-o simv_file |

Fail boleh laku yang dijana oleh kompilasi ialah simv secara lalai Anda boleh menggunakan -o untuk menukar boleh laku nama fail. Jika anda mengubah suainya di sini, anda tidak akan menggunakan simv tetapi nama o yang sepadan semasa melaksanakan simulasi. |

2. Contoh penggunaan vcs

menggunakan tutorial rasmi penambah penuh Pertama, proses pelaksanaan tanpa menggunakan skrip diperkenalkan.

(1) Mula-mula laksana vcs dan tambah fail full_adder yang sepadan

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

Tulis full_adder.v dahulu di sini kerana fail tb diperlukan Panggilnya, jadi tulis fail yang dipanggil dahulu Penyataan ini akan menghasilkan fail simv (jika -o simv_file digunakan, nama fail yang sepadan akan dihasilkan).

(2) Anda boleh menggunakan fail ./simv untuk melaksanakan antara muka bentuk gelombang, atau anda boleh menggunakan arahan berikut untuk membuka antara muka di latar belakang.

dve &或者 ./simv -l run.log -gui

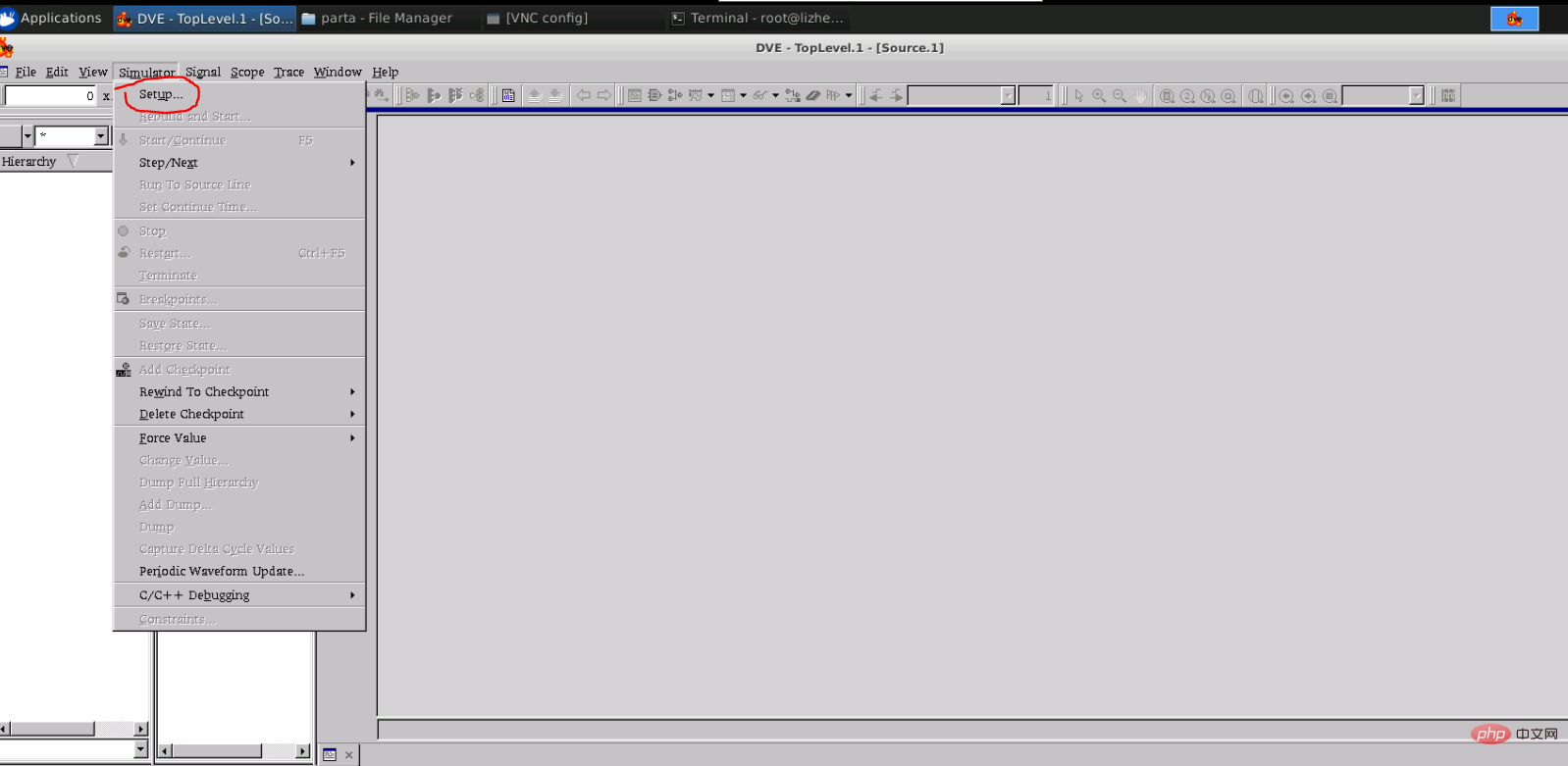

(3) Jika anda melaksanakannya dengan ./simv, anda akan melihat fail bentuk gelombang secara langsung Jika anda menggunakan dve &, anda perlu menambah fail simv sendiri untuk melihat bentuk gelombang , pilih simulator->Persediaan , tambah fail simv yang dijana.

Di bawah jalankan semua, jika tiada skala masa diberikan, ralat akan dilaporkan di sini. Jika tiada ralat bermakna fungsi kita betul-betul betul. Klik kanan untuk menambah fail bentuk gelombang dan tekan kekunci f untuk memaparkan bentuk gelombang.

(4) Empat fungsi butang berikut

Yang pertama: Jejaki siapa yang memacu isyarat ctrl+d

Yang kedua: Jejaki perubahan nilai isyarat ctrl+ shift+d

Ketiga: Jejaki keadaan tidak diketahui

Keempat: Jejaki siapa yang sedang dipandu

3.makefile Kaedah penulisan

kaedah penulisan skrip vcs boleh membantu ekspres ekspres untuk mensimulasikan dan mendapatkan fail bentuk gelombang.

Antaranya, .PHONY boleh menentukan kata kunci yang sesuai dengan operasi make.

.PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb

Dengan cara ini, buat vcs melaksanakan pernyataan vcs, buat sim melaksanakan pernyataan simv, buat dve membuka fail wave dan buat clean mengalih keluar beberapa fail berlebihan.

Antaranya, verilog_file.f ialah senarai fail, yang boleh dijana menggunakan pernyataan berikut, supaya semua nama fail yang berakhir dengan v ditulis pada fail sasaran.

find -name ".*v" > file.listCadangan berkaitan: "Tutorial Video Linux"

Atas ialah kandungan terperinci apa itu linux vcs. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!