Rumah >Peranti teknologi >AI >Inspirasi daripada seni bina cip yang dibangunkan sendiri oleh Tesla

Inspirasi daripada seni bina cip yang dibangunkan sendiri oleh Tesla

- PHPzke hadapan

- 2023-04-08 22:51:021080semak imbas

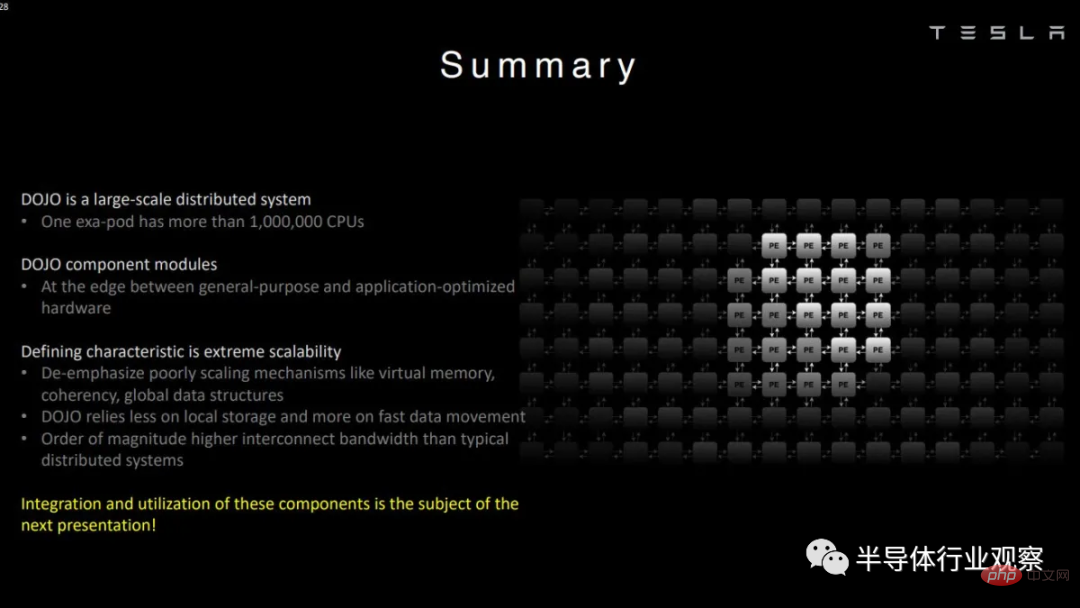

Untuk mengatakan Tesla hanya berminat dalam pembelajaran mesin adalah suatu pernyataan yang remeh. Malah, pembuat kereta elektrik itu membina superkomputer dalaman yang dipanggil Dojo yang dioptimumkan untuk melatih model pembelajaran mesinnya.

Tidak seperti kebanyakan superkomputer lain, Dojo tidak menggunakan CPU dan GPU luar biasa, seperti daripada AMD, Intel atau Nvidia. Tesla mereka bentuk seni bina mikronya berdasarkan keperluan mereka, membolehkan mereka membuat pertukaran yang tidak dapat dilakukan oleh seni bina tujuan umum.

Dalam artikel ini, kita akan melihat seni bina berdasarkan demo Tesla di Hot Chips. Seni bina tidak mempunyai nama yang berasingan, jadi untuk kesederhanaan, apabila kita merujuk kepada Dojo dalam perkara berikut, kita bercakap tentang seni bina.

Diagram Blok

Pada tahap tinggi, Dojo ialah teras 8 lebar dengan SMT empat hala berjalan pada 2 GHz konservatif, Mempunyai saluran paip gaya CPU menjadikannya lebih bertolak ansur dengan algoritma dan kod percabangan yang berbeza daripada GPU. Set arahan Dojo adalah serupa dengan RISC-V dari segi skalar, tetapi jurutera Tesla menambah set arahan vektor tersuai yang memfokuskan pada mempercepatkan pembelajaran mesin.

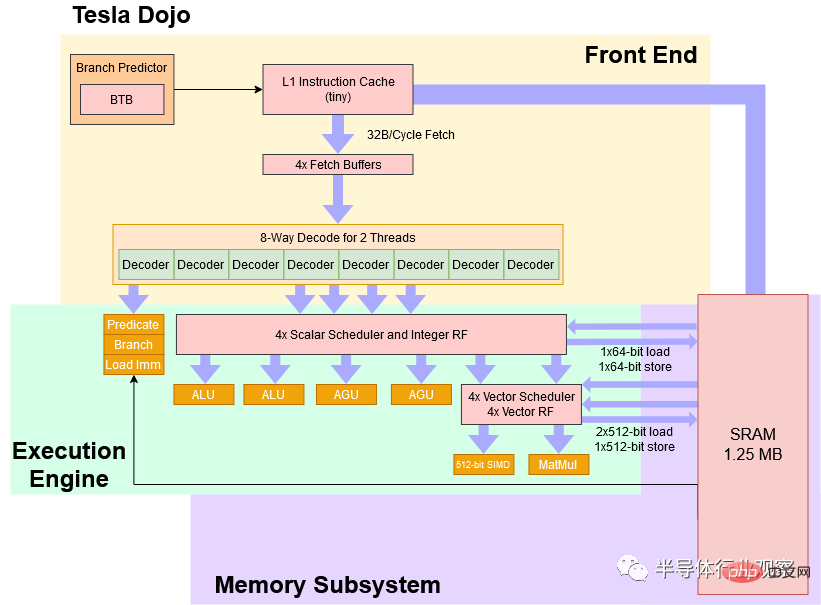

Rajah blok dipermudah teras Tesla Dojo

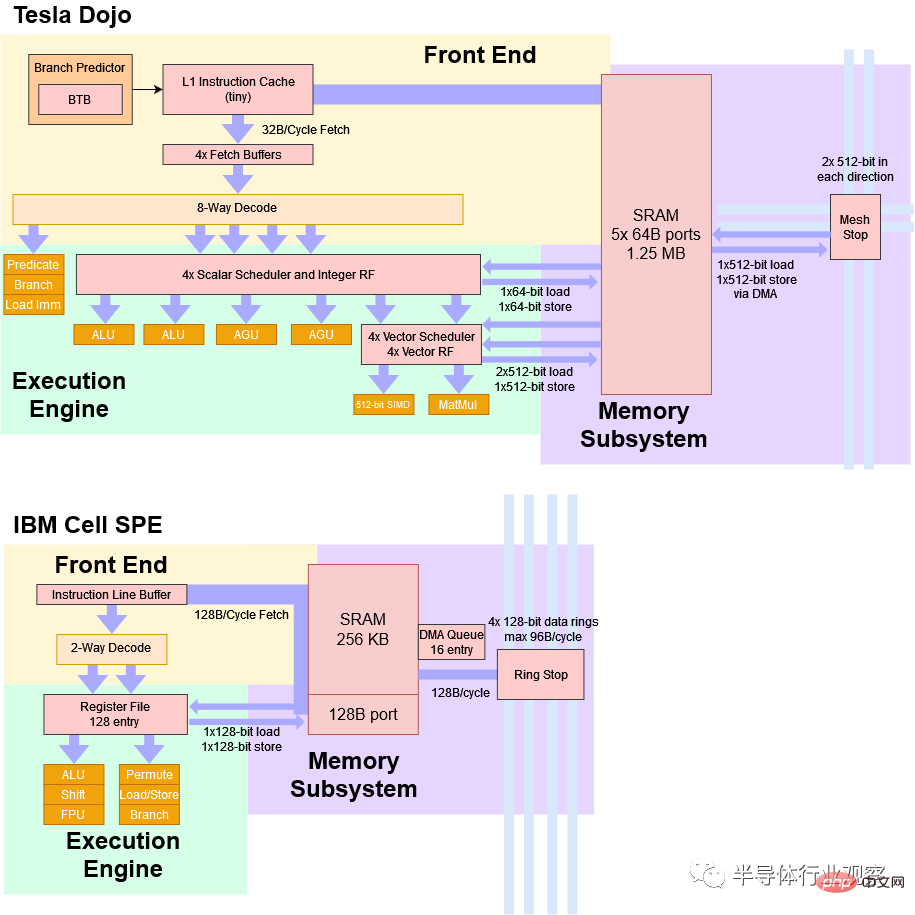

Tesla menghuraikan Dojo sebagai "CPU tujuan am yang berkeupayaan tinggi." Dari perspektif prestasi, pasti ada kebenarannya. Tetapi untuk meningkatkan ketumpatan pengkomputeran, Tesla melakukan pengorbanan, dan teras Dojo sangat sukar digunakan berbanding dengan CPU yang biasa kita gunakan dalam desktop, komputer riba dan telefon pintar. Dalam beberapa cara, kernel Dojo mengendalikan perkara yang lebih seperti SPE dalam Sel IBM daripada kernel CPU tujuan am tradisional.

Suka Cell’s SPE?

Diperkenalkan pada pertengahan 2000-an, pemproses IBM Cell menampilkan lapan "Elemen Pemprosesan Sinergis" atau SPE, yang terdiri daripada teras CPU berfungsi sepenuhnya ("Elemen Pemprosesan Kuasa" ” atau PPE: Elemen Pemprosesan Kuasa) kawalan. Pada pandangan pertama, Dojo mempunyai banyak persamaan dengan SPE.

Kedua-dua Dojo dan SPE dioptimumkan untuk pemprosesan vektor dan bergantung pada pemproses hos yang berasingan untuk pengedaran kerja. Kod yang dijalankan pada Dojo atau SPE tidak boleh mengakses terus memori sistem. Sebaliknya, aplikasi dijangka berfungsi terutamanya dalam sebahagian kecil SRAM tempatan. SRAM tempatan ini diuruskan oleh perisian dan tidak boleh digunakan sebagai cache. Jika data daripada memori utama diperlukan, ia mesti dibawa masuk menggunakan operasi DMA.

Akhir sekali, kedua-dua Dojo dan SPE Cell kekurangan sokongan untuk ingatan maya. Kami akan membincangkan butiran tentang maksud ini kemudian, tetapi secara ringkasnya, ia menyukarkan multitasking.

Perbandingan yang sangat mudah antara Tesla Dojo dan IBM Cell SPE

Dojo berbeza dalam beberapa cara penting. Oleh kerana Dojo tidak direka bentuk dengan mengambil kira penempatan berskala kecil, pemproses hos berada pada sistem hos yang berasingan. Sistem hos ini mempunyai kad PCIe dengan pemproses antara muka, yang kemudiannya disambungkan ke cip Dojo melalui pautan rangkaian berkelajuan tinggi. Sebaliknya, pemproses utama Cell berada pada cip yang sama. Ini memungkinkan untuk menggunakan cip Sel individu secara individu - sesuatu yang tidak boleh dilakukan dalam Dojo.

Blok tempatan SRAM 1.25 MB Dojo jauh lebih besar dan mempunyai lebar jalur yang lebih tinggi daripada Cell SPE yang hanya mempunyai 256 KB SRAM. SRAM 256 KB Cell hanya mempunyai satu port, mampu menghantar 128B setiap kitaran. SRAM Dojo mempunyai lima port 64B. Sudah tentu, matlamat seni bina sangat berbeza. Dojo adalah jam lebar dan jam rendah, manakala Cell SPE mempunyai saluran paip sempit dan dalam yang direka untuk jam tinggi.

Halaman hadapan: Keselesaan CPU, dsb.

Mari kami memperkenalkan secara ringkas saluran paip Dojo bermula dari bahagian hadapan. Terdapat beberapa jenis peramal cawangan, kerana rajah Tesla menunjukkan BTB (penampan sasaran cawangan: penimbal sasaran cawangan). Keupayaan ramalannya mungkin tidak mencapai tahap yang kita lihat pada teras berprestasi tinggi daripada AMD, ARM dan Intel, kerana Dojo perlu mengutamakan kawasan die perbelanjaan pada pelaksanaan vektor. Tetapi peramal cawangan asas adalah peningkatan yang besar berbanding tanpa peramal, dan keupayaan ramalan cawangan Dojo harus memberikan prestasi yang lebih baik daripada GPU apabila berurusan dengan kod bercabang atau jejak arahan yang lebih besar.

Setelah peramal cawangan menjana penunjuk pengambilan arahan seterusnya, Dojo boleh mengambil 32 bait setiap kitaran daripada cache arahan "kecil" ke dalam penimbal pengambilan setiap utas (penampan pengambilan setiap utas). Cache arahan ini boleh membantu mengurangkan tekanan lebar jalur arahan pada SRAM tempatan, memastikan bahagian data boleh mengakses SRAM dengan sedikit perbalahan yang mungkin. Selain itu, cache arahan tidak koheren. Jika kod baharu dimuatkan ke dalam SRAM tempatan, cache arahan mesti dibuang sebelum bercabang kepada kod baharu.

Pembentangan Hot Chips daripada Tesla

Dari penimbal pengambilan, penyahkod Dojo boleh memproses lapan arahan setiap kitaran daripada dua utas. Saya agak keliru tentang maksud "dua utas setiap kitaran", kerana CPU dengan SMT lazimnya mengendalikan satu utas setiap kitaran dan menukar benang pada sempadan kitaran. Mungkin Dojo membahagikan penyahkod kepada dua kelompok dan memilih dua utas untuk memberi mereka data dalam setiap gelung. Ini boleh mengurangkan penalti pemprosesan penyahkodan untuk cawangan yang diambil.

Semasa menyahkod, arahan tertentu (seperti cawangan, operasi berpredikat dan beban segera ("penghuraian senarai")) boleh dilaksanakan pada bahagian hadapan dan dikeluarkan daripada saluran paip. Ini sedikit seperti CPU x86 yang lebih baharu yang menghapuskan salinan daftar-untuk-daftar dalam penama semula. Tetapi anda mendengarnya betul - Dojo tidak menjejaki arahan "menghapuskan" melalui saluran paip untuk mengekalkan persaraan teratur. Pemproses lain menjejaki segala-galanya untuk keluar supaya mereka boleh berhenti di mana-mana sempadan arahan dan mengekalkan semua keadaan yang diperlukan untuk menyambung semula pelaksanaan. Keupayaan ini dipanggil "pengecualian tepat", dan sistem pengendalian moden menggunakannya untuk menyediakan semua jenis barang, seperti halaman ke cakera, atau memberitahu anda dengan tepat di mana kod anda rosak.

Tesla tidak mengambil berat tentang pengecualian yang tepat. Dojo memang mempunyai mod nyahpepijat di mana lebih banyak arahan dihantar melalui saluran paip untuk memberikan pengecualian "lebih tepat", tetapi tiada logik keluar yang teratur seperti CPU tersusun biasa.

Enjin pelaksanaan Dojo

Selepas melihat bahagian hadapan yang luas, saya melihat 4-lebar dengan hanya dua ALU dan dua AGU Integer enjin pelaksanaan boleh menjadi agak pelik. Tetapi saluran paip berbentuk corong ini masuk akal kerana beberapa arahan dilaksanakan dan dibuang pada bahagian hadapan.

Dojo juga tidak akan menjadikannya sebagai sistem pelanggan yang prestasi integer skalar adalah penting. Oleh itu, bahagian integer menyediakan daya pemprosesan yang mencukupi untuk mengendalikan aliran kawalan dan penjanaan alamat untuk memastikan sel vektor dan matriks diberi makan.

Tamat pelaksanaan vektor dan matriks Dojo diletakkan selepas enjin pelaksanaan skalar dalam saluran paip teras, dan terdapat dua saluran paip pelaksanaan. Dua saluran paip mungkin tidak begitu banyak bunyinya, tetapi Dojo mempunyai unit pelaksanaan yang sangat luas di belakang saluran paip ini. Satu saluran paip boleh melakukan pelaksanaan vektor 512-bit, manakala saluran paip yang lain melakukan pendaraban matriks 8x8x4. Oleh itu, selagi arahan mendedahkan keselarian eksplisit yang mencukupi, Dojo boleh mencapai daya pemprosesan yang sangat tinggi - terutamanya apabila menggunakan unit matriks. Tesla mendakwa bahawa cip dengan 354 teras Dojo boleh mencapai 362 BF16 TFLOPS pada 2 GHz, yang menunjukkan bahawa setiap teras boleh melakukan 512 BF16 FLOPS setiap kitaran.

Kami tidak pasti sama ada Dojo boleh melaksanakan sepenuhnya di luar perintah. Tetapi Tesla mengatakan bahawa bahagian integer boleh berjalan jauh di hadapan bahagian vektor, mencadangkan ia boleh melaksanakan arahan yang digunakan untuk berhenti sehingga salah satu penjadual diisi. Kekurangan persaraan yang diperintahkan juga menunjukkan keupayaan pelaksanaan yang tidak sesuai.

Secara amnya, melaksanakan pelaksanaan di luar perintah datang dengan banyak kerumitan. Ini kerana CPU mesti melaksanakan arahan mengikut urutan. CPU berprestasi tinggi daripada AMD, ARM dan Intel menggunakan penimbal susunan semula yang besar (dan struktur lain) untuk menjejaki arahan supaya keputusannya boleh dilakukan mengikut susunan program. Ini bermakna bahawa jika program melakukan sesuatu yang bodoh, seperti bahagi dengan sifar, teras ini boleh menunjukkan dengan tepat arahan yang salah. Tambahan pula, mereka boleh memaparkan keadaan CPU yang mencerminkan tindakan semua arahan sebelum kesalahan, tetapi tidak selepas. Ini bermakna anda boleh membetulkan apa sahaja yang menyebabkan arahan menjadi salah dan menyambung semula pelaksanaan. Dojo melepaskan keupayaan ini. Sebagai pertukaran, Dojo mengelak kuasa dan overhed kawasan yang berkaitan dengan penjejakan setiap arahan melalui saluran paipnya untuk memastikan keputusan dihantar mengikut susunan program.

Akses SRAM

Biasanya, kami akan bercakap tentang caching di sini. Tetapi Dojo tidak mempunyai akses langsung ke memori sistem, jadi kami akan membincangkan blok 1.25 MB SRAM. Ia boleh mengendalikan dua beban 512-bit setiap kitaran, memberikannya lebar jalur setiap kitaran untuk memadankan CPU Intel berkeupayaan AVX-512. Tesla mengatakan SRAM mempunyai lima port 512-bit (2 port muatan, 1 port stor dan dua port henti-ke-grid). Tetapi terdapat hanya dua AGU pada sisi skalar, yang mungkin bermakna teras tidak dapat mengendalikan dua beban 512-bit dan satu kedai 512-bit setiap kitaran.

Oleh kerana blok SRAM tempatan Dojo tidak dicache, ia tidak memerlukan teg dan bit status yang disimpan bersama data. SRAM juga tidak mempunyai cache L1D di hadapannya, jadi ia perlu cukup pantas untuk mengendalikan semua arahan memuatkan dan menyimpan tanpa menyebabkan kesesakan, walaupun saiznya lebih hampir dengan cache L2. Tidak melaksanakan SRAM sebagai cache mungkin merupakan cara Tesla untuk mengekalkan kependaman rendah. Jika kita melihat kembali kepada seni bina Hammer AMD sejak dahulu lagi, kita dapat melihat bahawa mengakses 1 MB L2 selepas mengesan ketinggalan L1D mengambil masa 8 kitaran (untuk jumlah kependaman 12 kitaran). Jika 1 MB SRAM dialamatkan secara langsung dan bukannya digunakan sebagai cache, tiga peringkat mungkin dialih keluar, menurunkan kependaman kepada 5 kitaran:

Daripada demo Hot Chips yang lebih lama Slaid ini menunjukkan peringkat saluran paip terlibat dalam akses cache L2. Jika L2 bukan cache, peringkat yang boleh dilangkau ditandakan dengan warna merah.

Memandangkan beberapa dekad peningkatan nod proses dan sasaran kelajuan jam yang lebih rendah daripada Athlon, adalah mudah untuk melihat cara Tesla boleh mengakses SRAM bersaiz L2 dengan sekeping kependaman seperti L1. Melangkau cache L1 sudah tentu menjimatkan kawasan dan kuasa.

Untuk mengurangkan lagi kependaman, kawasan dan kerumitan teras, Dojo tidak mempunyai sokongan memori maya. Oleh itu, ia tidak mempunyai mekanisme TLB atau page walk. Sistem pengendalian moden menggunakan memori maya untuk memberikan setiap proses pandangan memorinya sendiri. Alamat memori yang digunakan oleh program ini bukanlah akses terus ke alamat memori fizikal, tetapi ditukar kepada alamat fizikal oleh CPU menggunakan struktur paging yang ditetapkan oleh sistem pengendalian. Beginilah cara sistem pengendalian moden mengasingkan program antara satu sama lain dan menghalang satu aplikasi yang tidak berkelakuan daripada menjatuhkan keseluruhan sistem.

Memori maya juga ialah cara anda boleh menjalankan lebih banyak program daripada yang anda ada dalam ingatan fizikal. Apabila anda kehabisan memori sebenar, sistem pengendalian menyahpeta halaman, menulisnya ke cakera, dan memberikan program anda memori yang diperlukan. Apabila beberapa program jelek lain cuba mengakses memori itu, CPU cuba menterjemah alamat maya kepada alamat fizikal, tetapi mendapati terjemahan itu tidak wujud. CPU membuang pengecualian kesalahan halaman, yang dikendalikan oleh sistem pengendalian dengan membaca halaman yang diusir kembali ke dalam memori fizikal dan mengisi entri jadual halaman.

Tiada satu pun daripada ini boleh dilakukan di Dojo. Ciri SMT 4 hala kernel lebih kepada mendedahkan satu aplikasi kepada keselarian eksplisit daripada meningkatkan prestasi berbilang tugas. Contohnya, satu utas boleh melakukan pengiraan vektor manakala satu lagi utas tidak segerak memuatkan data daripada memori sistem ke SRAM (melalui DMA).

Untuk memudahkan lagi reka bentuk, Dojo boleh menangani SRAM dengan hanya 21 bit alamat, yang boleh memudahkan AGU Dojo dan bas pengalamatan. Pertukaran ini boleh membenarkan Tesla mengakses SRAM ini dengan kependaman yang cukup rendah untuk mengelak daripada melaksanakan cache data L1 yang berasingan di hadapannya.

Akses Memori

Bercakap tentang memori sistem, cip Dojo tidak disambungkan terus ke memori. Sebaliknya, mereka menyambung kepada pemproses antara muka yang dilengkapi dengan HBM. Pemproses antara muka ini juga bertanggungjawab untuk berkomunikasi dengan sistem hos.

Jubin Dojo dengan 25 cip bebas boleh mengakses 160 GB memori HBM Tesla berkata mereka boleh mengakses data dari setiap jubin merentasi sempadan cip pemindahan tepi 900 GB/s, yang bermaksud pemproses antara muka dan HBMnya boleh diakses dengan jalur lebar pautan 4.5 TB/s. Oleh kerana akses kepada HBM memerlukan melalui cip yang berasingan, kependaman akses boleh menjadi sangat tinggi.

kecil, macam mana nak buat?

Dojo ialah kernel 8 lebar dengan sekurang-kurangnya beberapa keupayaan pelaksanaan OoO, daya pemprosesan vektor yang baik dan unit pendaraban matriks. Tetapi walaupun dengan 1.25 MB SRAM tempatan, ia akhirnya menjadi teras yang sangat kecil. Sebagai perbandingan, A64FX Fujitsu menduduki lebih daripada dua kali ganda kawasan pada nod proses yang sama. Reka bentuk pemproses adalah tentang membuat pertukaran yang betul. Tesla mahu memaksimumkan pemprosesan pembelajaran mesin dengan membungkus sejumlah besar teras pada cip, jadi teras individu mestilah kecil. Untuk mencapai kecekapan zonnya, Dojo menggunakan beberapa teknik biasa. Ia berjalan pada 2 GHz konservatif. Litar jam yang lebih rendah cenderung untuk menduduki kawasan yang kurang. Ia mungkin mempunyai peramal cawangan asas dan cache arahan kecil. Jika program mempunyai jejak kod yang besar atau mempunyai banyak cawangan, ini akan mengorbankan beberapa prestasi.

Tetapi Tesla juga mengurangkan lagi kuasa dan penggunaan kawasan dengan memotong ciri yang tidak diperlukan untuk menjalankan beban kerja dalaman. Mereka tidak melakukan caching sisi data, tidak menyokong memori maya dan tidak menyokong pengecualian yang tepat.

Hasilnya ialah teras pemproses yang menawarkan fleksibiliti prestasi teras CPU moden sambil menjadi lebih rendah dalam banyak cara daripada Intel 8086 Mesra pengguna dan pengaturcara. Sebagai tambahan kepada teras, Tesla juga menjimatkan kawasan cip pada skala dengan mereka bentuk cip Dojo khusus untuk penggunaan.

Pelaksanaan Fizikal

Mengecut, teras Dojo dilaksanakan pada dadu 645 mm2 yang sangat besar yang dipanggil D1. Tidak seperti cip lain yang kita kenali, cip Dojo tunggal tidak boleh berdikari. Ia tidak mempunyai pengawal DDR atau PCIe. Terdapat antara muka IO di sekeliling tepi dadu yang membolehkan dadu berkomunikasi dengan dadu bersebelahan dengan kependaman kira-kira 100 ns.

Untuk mengakses memori sistem, cip Dojo D1 mesti berkomunikasi dengan pemproses antara muka yang mempunyai HBM onboard. Pemproses antara muka seterusnya disambungkan kepada sistem hos melalui PCIe (pemproses antara muka dipasang pada kad PCIe). Secara teorinya, penggunaan Dojo berfungsi yang minimum akan melibatkan cip Dojo, kad pemproses antara muka dan sistem hos. Tetapi Tesla menggunakan Dojo dies dalam modul yang mengandungi 25 dies setiap satu untuk memberikan rasa skala. Mati Dojo D1 direka khusus untuk menjadi blok binaan untuk superkomputer dan tidak lebih.

Pengkhususan ini boleh menjimatkan lebih banyak kawasan die. Dojo D1 tidak membuang ruang pada pengawal DDR dan PCIe. Kebanyakan dadu diambil oleh teras Dojo yang besar, kecuali penyambung IO tersuai di luar yang direka bentuk untuk bersambung dengan dadu bersebelahan.

Sebaliknya, cip yang direka dengan lebih fleksibiliti penggunaan dalam fikiran menghabiskan banyak ruang pada IO . Cip Zen 1 "Zeppelin" AMD menunjukkan ini dengan baik. Zeppelin boleh menyambung terus ke memori DDR4, peranti PCIe, pemacu SATA dan peranti USB – sesuai untuk keperluan pelanggan. Dalam pelayan, antara muka IFOP membolehkannya berkomunikasi dengan cip bersebelahan. Sebahagian besar SRAM yang terletak berhampiran IFOP mungkin merupakan penapis pengintip, membantu mengekalkan keselarasan cache dengan cekap dalam tetapan kiraan teras tinggi. Dojo tidak cuba mengekalkan keselarasan cache merentas teras, dan tidak menggunakan sebarang SRAM untuk penapisan pengintipan.

Demo ciplet daripada AMD di ISSCC 2021

AMD membayar untuk fleksibiliti ini dengan mendedikasikan kira-kira 44% daripada kawasan mati "Zeppelin" kepada logik selain daripada teras dan cache. Dojo hanya menggunakan 28.9% daripada kawasan die untuk perkara selain SRAM dan teras.

Kata Akhir

Senibina mikro di belakang superkomputer Tesla Dojo menunjukkan cara untuk mencapai ketumpatan pengiraan yang sangat tinggi sambil mengekalkan Keupayaan CPU untuk mengendalikan bercabang kod. Untuk sampai ke sana, anda perlu melepaskan kebanyakan keselesaan yang menentukan pengalaman pengkomputeran moden kami. Jika anda secara hipotesis boleh membina desktop anda di sekeliling teras Dojo, pengalaman itu mungkin akan terasa biasa kepada sesiapa sahaja yang telah menggunakan MS-DOS. Anda tidak boleh menjalankan berbilang aplikasi pada masa yang sama. Satu aplikasi yang tidak berkelakuan boleh memaksa anda untuk but semula sistem anda. Jika anda tidak mempunyai RAM yang mencukupi untuk menjalankan program, anda boleh melupakan menjalankannya sepenuhnya (tanpa halaman ke cakera).

Tetapi pertukaran ini masuk akal dalam superkomputer Tesla. Tesla tidak memerlukan teras Dojo untuk mengendalikan berbilang aplikasi berjalan secara serentak, Dojo hanya perlu menjalankan kod yang dipercayai di dalamnya. Jadi, Tesla tidak mengambil berat tentang sokongan memori maya. Begitu juga, program pembelajaran mesin yang dijalankan pada Dojo akan ditulis dengan mengambil kira sistem khusus tersebut. Anda tidak akan mempunyai kumpulan program sewenang-wenang yang mungkin memerlukan lebih banyak memori daripada yang tersedia. Ini bermakna anda tidak memerlukan pengecualian yang tepat (dan ingatan maya) untuk membenarkan teknik seperti overcommit memori, pemampatan memori atau menukar halaman memori antara cakera. Pengecualian yang tepat juga berguna untuk nyahpepijat, tetapi Tesla melakukannya dengan cara yang lebih murah melalui mod nyahpepijat yang berasingan.

Apa yang pasti ialah pertukaran yang digunakan Tesla untuk mencapai ketumpatan pengiraan yang tinggi tidak mungkin berlaku dalam CPU pengguna atau pelayan . Tetapi mereka sangat menyeronokkan dalam aksi, dan kami harus berterima kasih kepada Tesla kerana meluangkan masa untuk menunjukkannya di Hot Chips. Sepanjang dua dekad yang lalu, penambahbaikan dalam nod proses telah menjadi perlahan, menyebabkan kemajuan yang lebih perlahan dalam prestasi berbenang tunggal. Kekangan kuasa dan penyejukan telah mengurangkan prestasi berbilang benang selama lima tahun yang lalu. Tetapi keperluan untuk lebih kuasa pengkomputeran tidak menjadi perlahan, jadi syarikat beralih kepada perkakasan yang lebih khusus untuk mengikuti perkembangan.

Seni bina dalam superkomputer Dojo Tesla ialah contoh yang baik tentang cara pertukaran dibuat untuk meningkatkan ketumpatan pengiraan dan cara aliran semasa memihak kepada penyajian aplikasi terhalang daya pemprosesan Program ini memperkenalkan perkakasan khusus.

Atas ialah kandungan terperinci Inspirasi daripada seni bina cip yang dibangunkan sendiri oleh Tesla. Untuk maklumat lanjut, sila ikut artikel berkaitan lain di laman web China PHP!

Artikel berkaitan

Lihat lagi- Aliran teknologi untuk ditonton pada tahun 2023

- Cara Kecerdasan Buatan Membawa Kerja Baharu Setiap Hari kepada Pasukan Pusat Data

- Bolehkah kecerdasan buatan atau automasi menyelesaikan masalah kecekapan tenaga yang rendah dalam bangunan?

- Pengasas bersama OpenAI ditemu bual oleh Huang Renxun: Keupayaan penaakulan GPT-4 belum mencapai jangkaan

- Bing Microsoft mengatasi Google dalam trafik carian terima kasih kepada teknologi OpenAI