HBM4 메모리는 개발 중이며 더 넓은 2048비트 인터페이스를 사용할 예정입니다.

- 王林앞으로

- 2023-10-15 18:13:051349검색

삼성 공식 뉴스에 따르면 고성능 컴퓨팅(HPC)용 HBM 메모리가 새로운 진전을 이루었습니다. 9.8Gbps HBM3E 제품은 고객에게 샘플링을 시작했으며 HBM4 메모리는 2025년에 출시될 것으로 예상됩니다

아직 HBM4에 대한 공식 사양은 없지만 TSMC는 2023 OIP 포럼에서 개발 중인 몇 가지 표준을 공개했습니다. TSMC는 앞으로 HBM4 메모리의 인터페이스 비트 폭이 2048비트로 두 배가 될 것이라고 밝혔습니다

다양한 기술적인 이유로 HBM 메모리가 차지하는 공간을 늘리지 않기를 희망한다는 점도 언급할 가치가 있습니다. 이 목표를 달성하면 클럭 속도를 더 높이지 않고도 차세대 HBM 메모리의 상호 연결 밀도를 두 배로 늘릴 수 있습니다.

계획에 따르면 이를 통해 HBM4는 여러 기술 수준에서 획기적인 발전을 이룰 수 있습니다.

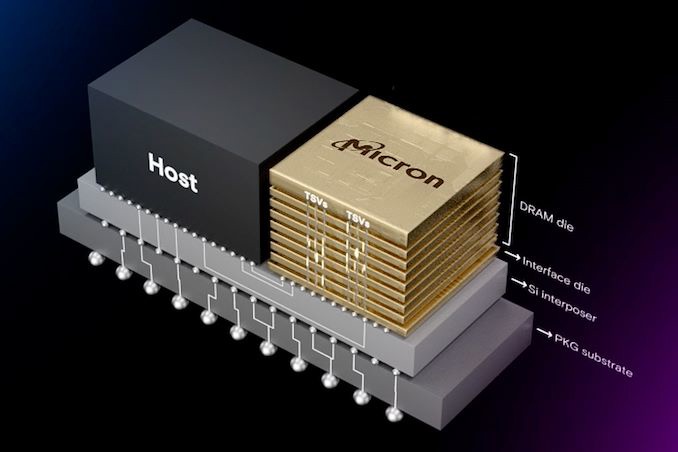

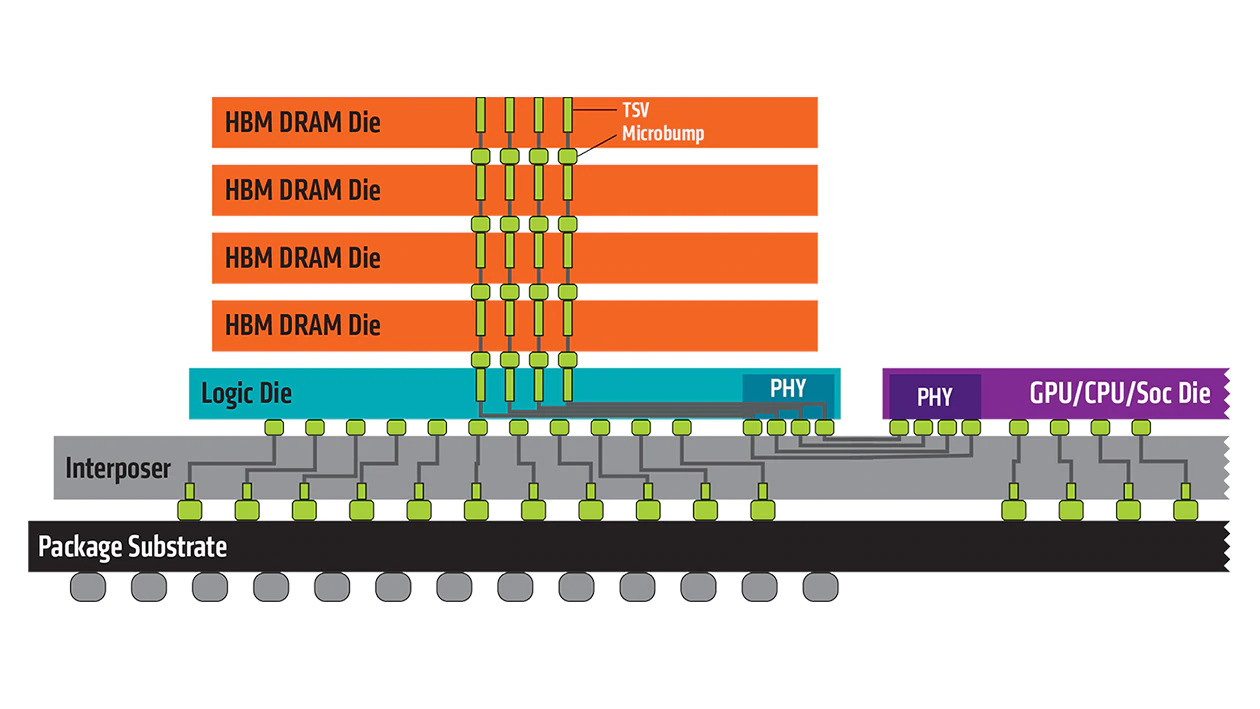

DRAM 스택 측면에서 2048비트 메모리 인터페이스는 실리콘 비아 수를 크게 늘려야 합니다. 동시에 외부 칩 인터페이스는 범프 피치를 55미크론 미만으로 줄이고 마이크로 범프 수를 크게 늘려야 합니다(이 사이트의 참고: HBM3에는 현재 약 3982개의 마이크로 범프가 있습니다).

또한 HBM4는 하나의 모듈에 16개의 메모리 칩을 쌓는 16-Hi 스태킹 모드를 채택하여 기술적 복잡성을 증가시킵니다(기술적 관점에서 볼 때 HBM3도 16-Hi 스태킹을 지원하지만 실제로 이 접근 방식을 채택한 제조업체는 없습니다.)

모든 새로운 측정 기준은 모든 것이 원활하게 실행되도록 하기 위해 칩 제조업체, 메모리 제조업체 및 칩 패키징 회사 간의 긴밀한 협력 접근 방식을 필요로 합니다.

암스테르담에서 열린 TSMC OIP 2023 컨퍼런스에서 TSMC의 설계 인프라 관리 책임자인 Dan Kochpatcharin은 다음과 같이 말했습니다. “속도를 두 배로 늘리는 대신 [인터페이스] 핀을 두 배로 늘렸기 때문입니다. 이것이 바로 우리가 HBM4를 사용하는 이유입니다. 우리는 세 파트너 모두와 협력하여 [고급 패키징을 통해] HBM4를 인증하고 RDL이나 중재자 또는 그 사이의 모든 콘텐츠가 HBM4의 레이아웃과 속도를 지원할 수 있는지 확인하기 위해 열심히 노력하고 있습니다. 따라서 우리는 삼성, SK하이닉스, 마이크론과 협력을 유지하고 있습니다.”

광고문: 기사에 포함된 외부 점프 링크(하이퍼링크, QR 코드, 비밀번호 등을 포함하되 이에 국한되지 않음)는 더 많은 정보를 전달하기 위해 사용됩니다. 선택 시간을 절약하세요. 결과는 참고용일 뿐입니다. 이 사이트의 모든 기사에는 이 내용이 포함되어 있습니다.

위 내용은 HBM4 메모리는 개발 중이며 더 넓은 2048비트 인터페이스를 사용할 예정입니다.의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!