여기에 트랜지스터 생명선이 있습니다. 3D 적층 CMOS, 무어의 법칙이 앞으로 10년 동안 계속될까요?

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWB앞으로

- 2023-04-14 16:13:031668검색

트랜지스터는 "20세기 최고의 발명품"으로 알려져 있습니다.

그것의 출현은 집적 회로, 마이크로 프로세서 및 컴퓨터 메모리 생산의 토대를 마련했습니다.

1965년에 "무어의 법칙"이 제안되어 수십 년 동안 반도체 산업의 황금률이 되었습니다.

18~24개월마다 마이크로칩에 패키징되는 트랜지스터의 수가 두 배로 늘어나고, 칩의 성능도 두 배로 증가한다는 것을 보여줍니다.

그러나 새로운 프로세스 노드가 지속적으로 도입되면서 트랜지스터의 원자 수가 점점 줄어들고 있으며 다양한 물리적 한계로 인해 무어의 법칙이 더 발전하는 것을 제한하고 있습니다.

무어의 법칙이 끝났다고 생각하는 사람들도 있습니다.

따라서 무어의 법칙을 '살리기' 위해 엔지니어들은 트랜지스터 구조를 바꾸고, 면적과 소비전력을 지속적으로 줄여 성능을 향상시켜야 합니다.

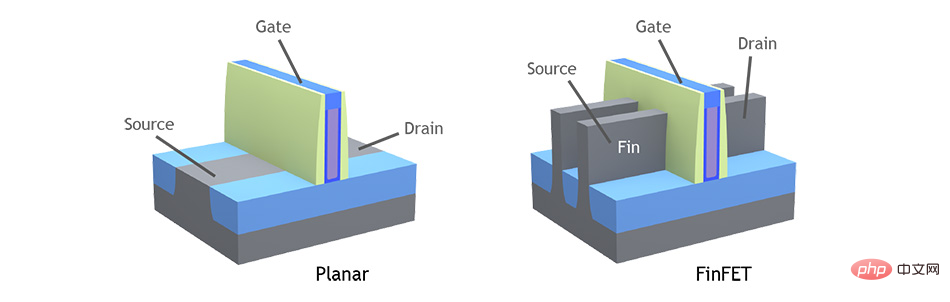

20세기 후반에는 평면 트랜지스터 설계(Planar Transistor)가 주로 유행했습니다. 2010년대에 들어서면서 점차 평면 디자인을 3D 핀 형태의 디바이스가 대체하게 되었습니다.

이제 완전히 새로운 트랜지스터 설계 구조인 GAA(Gate-All-Around Transistor)가 FinFET의 후속 제품으로 곧 생산에 들어갑니다.

하지만 좀 더 지켜봐야 합니다. Intel이 제안한 새로운 트랜지스터 아키텍처인 RibbonFET을 사용하더라도 크기를 줄이는 데는 한계가 있기 때문입니다.

3D 적층형 상보형 금속 산화물 반도체(CMOS) 또는 CFET(상보형 전계 효과 트랜지스터)가 무어의 법칙을 향후 10년까지 확장하는 열쇠가 될 것이라고 믿습니다.

트랜지스터의 진화

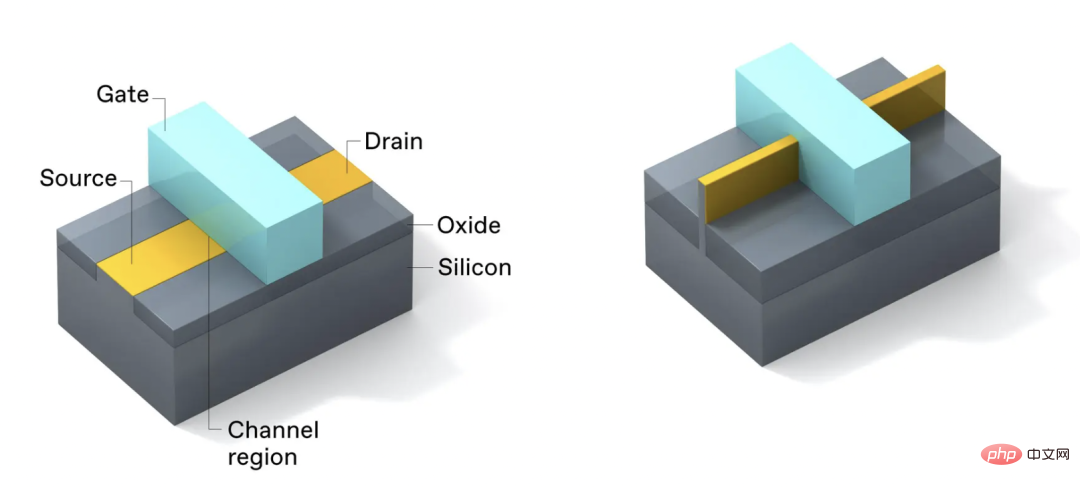

모든 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)에는 동일한 기본 구성 요소 세트가 있습니다.

게이트 스택, 채널 영역(채널 영역), 소스, 드레인

소스와 드레인은 화학적으로 도핑되어 이동형 전자가 풍부하거나(n형), 전자가 부족(p형)합니다. 채널 영역은 소스 및 드레인과 반대 방향으로 도핑됩니다.

2011년 이전 고급 마이크로프로세서의 트랜지스터 평면 버전에서는 MOSFET의 게이트 스택이 채널 영역 바로 위에 있었고 전기장을 채널 영역에 투영하는 데 사용되었습니다.

게이트에 소스에 비해 충분히 큰 전압을 가하면 채널 영역에 이동 전하 캐리어 층이 형성되어 소스와 드레인 사이에 전류가 흐를 수 있습니다.

평면 트랜지스터 설계의 크기를 줄이기 위해 "단채널 효과"가 물리학자들의 초점이 되었습니다.

공정 기술이 계속해서 향상되면서 트랜지스터의 게이트 전극 폭이 점점 작아지고 있습니다. 아시다시피, 게이트가 20nm보다 낮으면 전류는 제어할 수 없게 되고 소스 전류는 게이트를 관통하여 드레인에 직접 도달하게 됩니다.

이때 "누출"이 발생하여 칩의 에너지 소비가 급격히 증가합니다.

이 문제를 해결하기 위해 새로운 FinFET 트랜지스터 기술이 제안되었습니다. 더 나은 정적 제어를 제공하기 위해 3면의 채널 주위에 게이트를 감쌉니다.

FinFET은 이전 세대 평면 아키텍처와 동일한 성능 수준에서 전력 소비를 약 50% 줄입니다. FinFET은 또한 더 빠르게 전환하여 37% 성능 향상을 제공합니다.

인텔은 2011년 출시한 22nm 노드에 FinFET를 도입하여 3세대 코어 프로세서 생산에 사용했습니다.

이후 FinFET은 무어의 법칙을 실현하는 주체가 되었습니다.

하지만 FinFET으로 전환하면서 우리도 잃은 것이 있었습니다.

평면 디바이스에서 트랜지스터의 폭은 포토리소그래피에 의해 정의되므로 매우 유연한 매개변수입니다.

그러나 FinFET에서는 트랜지스터 폭이 개별적으로 증가하며 한 번에 하나의 핀이 추가됩니다. 이 속성을 흔히 핀 양자화라고 합니다.

FinFET의 유연성에도 불구하고 핀 양자화는 여전히 중요한 설계 제약으로 남아 있습니다. 이를 둘러싼 설계 규칙과 성능 향상을 위해 더 많은 핀을 추가하려는 욕구로 인해 로직 셀의 전체 면적이 늘어나고 단일 트랜지스터를 완전한 로직 회로로 바꾸는 상호 연결 스택이 복잡해집니다.

또한 트랜지스터의 커패시턴스를 증가시켜 스위칭 속도를 감소시킵니다. 따라서 FinFET은 업계의 주력 제품으로서 우리에게 큰 도움이 되었지만 새롭고 더욱 세련된 접근 방식이 필요합니다.

물리학자들이 곧 출시될 3D 트랜지스터인 RibbonFET을 발명하게 된 것은 바로 이러한 접근 방식입니다.

RibbonFET에서는 게이트가 트랜지스터 채널 영역을 둘러싸서 전하 캐리어 제어를 강화합니다. 새로운 구조는 또한 더 나은 성능과 보다 정교한 최적화를 가능하게 합니다.

구체적으로, 게이트는 채널을 완전히 둘러싸고 있어 채널 내의 전하 운반체를 더욱 엄격하게 제어할 수 있으며, 이는 이제 나노 크기의 실리콘 리본으로 형성됩니다.

이러한 나노리본(나노시트)을 이용하면 다시 포토리소그래피를 이용해 트랜지스터의 폭을 원하는 대로 바꾸는 것이 가능하다.

양자화 제약 조건을 제거한 후 애플리케이션에 적합한 크기의 너비를 생성할 수 있습니다. 이를 통해 전력, 성능, 비용의 균형을 맞출 수 있습니다.

더 중요한 것은 장치를 쌓아서 병렬로 작동함으로써 면적을 늘리지 않고도 장치가 더 많은 전류를 구동하고 성능을 향상시킬 수 있다는 것입니다.

따라서 인텔은 합리적인 전력으로 더 높은 성능을 달성하기 위해서는 RibbonFET이 최선의 선택이라고 믿습니다.

2024년에 Intel 20A 프로세스에 RibbonFET 구조를 도입할 예정입니다.

3D Stacked CMOS

Planar, FinFET, RibbonFET 트랜지스터의 공통점 중 하나는 모두 CMOS 기술을 사용한다는 것입니다. 앞서 언급했듯이 CMOS는 n형 트랜지스터와 p형 트랜지스터로 구성됩니다. . 이 기술은 다른 대안보다 훨씬 적은 전류를 소비하기 때문에 1980년대에 주류가 되었습니다. 전류가 적다는 것은 작동 주파수가 높고 트랜지스터 밀도가 높다는 것을 의미합니다.

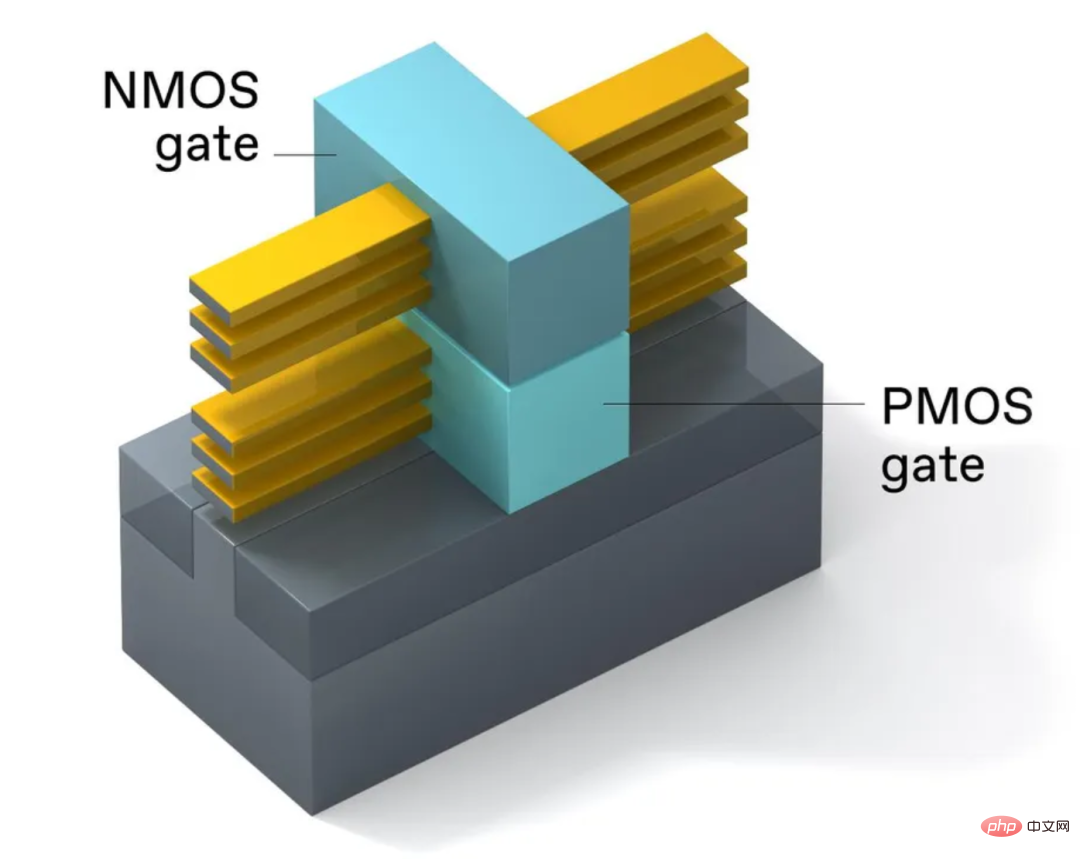

현재까지 모든 CMOS 기술은 NMOS 및 PMOS 트랜지스터의 표준 쌍을 나란히 배치했습니다. 그러나 2019년 IEEE 국제전자부품회의(IEDM) 기조연설에서는 PMOS 트랜지스터 위에 NMOS 트랜지스터를 배치하는 '3D 적층' 트랜지스터 개념이 제안됐다.

IEDM 2020에서는 이 3D 기술을 사용하여 논리 회로를 사용하여 설계된 최초의 인버터가 발표되었습니다. 3D 적층형 CMOS는 인버터 설치 공간을 효과적으로 절반으로 줄여 트랜지스터 면적 밀도를 두 배로 늘리고 무어의 법칙의 한계를 더욱 뛰어 넘습니다.

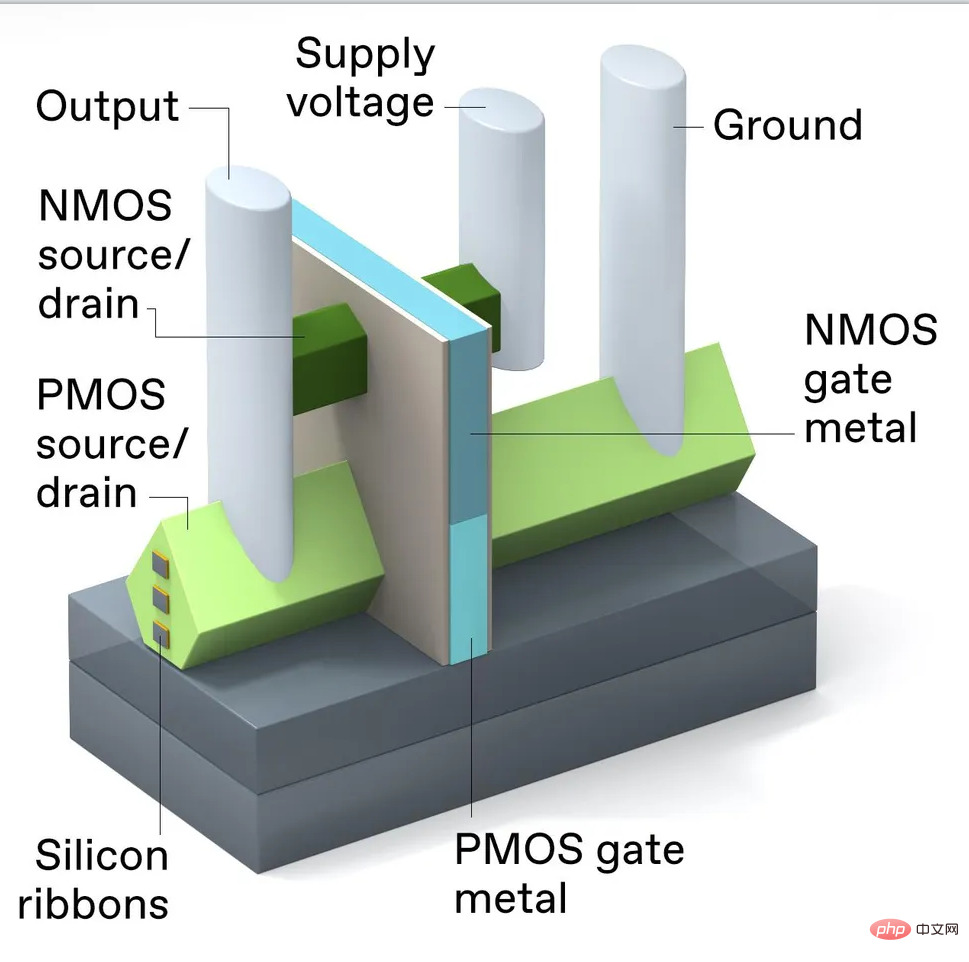

3D 적층형 CMOS 구조로 NMOS 장치 위에 PMOS 장치를 배치하고 전체 면적이 RibbonFET 면적 1개와 동일합니다. NMOS 및 PMOS 게이트는 서로 다른 금속 재료를 사용합니다.

3D 적층형 CMOS를 활용하려면 해결해야 할 프로세스 통합 문제가 많이 있으며, 그 중 일부는 CMOS 처리 및 제조의 한계와 관련이 있습니다.

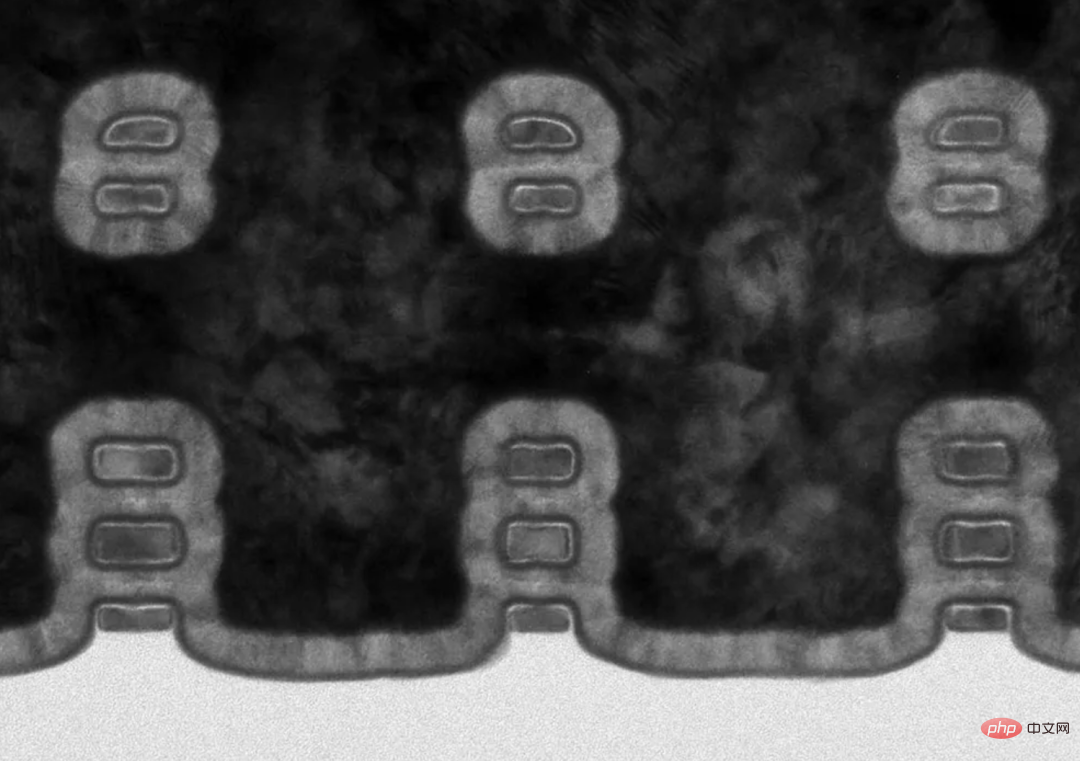

어떻게 달성하나요? 자체 정렬된 3D CMOS 제작은 실리콘 웨이퍼에서 시작됩니다. 웨이퍼 위에 우리는 "초격자"라고 불리는 구조인 실리콘과 실리콘 게르마늄 층을 층층이 증착합니다. 그런 다음 포토리소그래픽 패턴을 사용하여 초격자의 일부를 잘라내어 지느러미 모양의 구조를 남깁니다. 초격자 결정은 후속 개발 프로세스를 위한 강력한 지원 구조를 제공합니다.

다음으로, 다음 작업으로부터 전자를 보호하기 위해 "가짜" 폴리실리콘이 초격자 위에 배치됩니다. 수직 적층형 이중 소스/드레인 공정으로 알려진 이 단계는 상단 나노리본(미래 NMOS 사이트)의 양쪽 끝에서 인 도핑된 실리콘을 성장시키는 동시에 하단 나노리본(미래 PMOS 사이트)에서 도핑된 실리콘을 선택적으로 성장시킵니다. 그런 다음 전원 주위에 유전체를 배치하여 방전을 통해 전원을 서로 격리시킵니다.

3D 스태킹은 제곱밀리미터당 CMOS 트랜지스터 밀도를 효과적으로 두 배로 늘리며, 실제 밀도는 관련된 로직 셀의 복잡성에 따라 달라집니다.

드디어 문 공사가 시작됩니다. 먼저 이전에 설치된 거짓 도어를 제거하여 실리콘 나노리본을 노출시킵니다. 다음으로, 실리콘 게르마늄만 에칭되어 트랜지스터의 채널 영역인 평행한 실리콘 나노리본 더미가 형성됩니다.

그런 다음 나노리본의 네 면 모두에 매우 얇은 절연층을 코팅합니다. 이 절연층은 유전율이 높습니다. 나노리본 채널은 너무 작아서 평면 트랜지스터만큼 효율적으로 화학적으로 코팅할 수 없습니다.

금속을 사용하여 하단 나노리본을 둘러싸서 p-도핑 채널을 형성하고, 상단 나노리본은 다른 나노리본과 함께 n-도핑 채널을 형성합니다. 이러한 방식으로 게이트 스택이 구성되고 두 개의 트랜지스터가 설치됩니다.

이 과정은 복잡해 보일 수 있지만 다른 기술(Sequential 3D Stacking)보다 낫습니다. 후자를 사용하는 경우 NMOS 장치와 PMOS 장치를 별도의 웨이퍼에 장착한 다음 두 장치를 하나로 모아 PMOS 층을 NMOS 웨이퍼로 전사합니다. 자체 정렬된 3D 적층 방식은 처리 단계가 적고 제조 비용을 보다 엄격하게 제어할 수 있습니다.

그리고 더 중요한 것은 이 자체 정렬 방식으로 두 개의 웨이퍼를 연결할 때 발생할 수 있는 정렬 오류도 방지할 수 있다는 것입니다. 3D 적층형 CMOS에 필요한 모든 연결을 만드는 것은 매우 어렵습니다. 아래 장치 스택에서 전원을 연결해야 합니다. 설계상 NMOS 장치[위]와 PMOS 장치[아래]에는 별도의 소스/드레인 접점이 있지만 두 장치 모두 공통 게이트를 공유합니다.

NMOS와 PMOS 사이의 수직 간격을 최적화해야 한다는 점은 주목할 가치가 있습니다. 너무 짧으면 기생 용량이 증가하고, 너무 길면 상호 연결의 저항이 증가합니다. 두 장치 사이. 극단적인 상황에서는 회로 속도가 느려지고 더 많은 전력을 소비하게 됩니다.

IEDM 2021 컨퍼런스에서 American TEL Research Center가 발표한 것과 같은 많은 설계 연구에서는 3D CMOS의 제한된 공간 내에서 필요한 모든 상호 연결을 제공할 것을 제안하며, 이를 통해 논리 장치가 구성하는 영역을 크게 늘리지 않습니다. 연구 결과에 따르면 최고의 상호 연결 옵션을 찾는 데 혁신을 가져올 수 있는 기회가 많이 있습니다.

무어 법칙의 미래

스트립 전계 효과 트랜지스터와 3D CMOS를 사용하면 적어도 2024년과 그 이후까지 무어 법칙의 수명을 연장할 수 있는 명확한 경로가 있습니다.

무어의 법칙 제안자인 고든 무어는 2005년 인터뷰에서 “이루어진 진전에 가끔 놀랐다”고 인정했습니다.

"그 과정에서 이제 끝이라고 생각한 적도 있었지만, 우리 크리에이티브 엔지니어들이 그 어려움을 극복할 수 있는 방법을 생각해 냈습니다."

트랜지스터 제조 공정으로 FinFET를 거쳐, 지속적인 최적화를 통해 RibbonFET 시대를 맞이했고, 마침내 3D Stacked CMOS 공정으로 나아가게 되면서 Gordon Moore 씨에게 남은 놀라움이 곧 찾아올 것으로 예상됩니다.

위 내용은 여기에 트랜지스터 생명선이 있습니다. 3D 적층 CMOS, 무어의 법칙이 앞으로 10년 동안 계속될까요?의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!