Tesla가 자체 개발한 칩 아키텍처에서 영감을 얻었습니다.

- PHPz앞으로

- 2023-04-08 22:51:021077검색

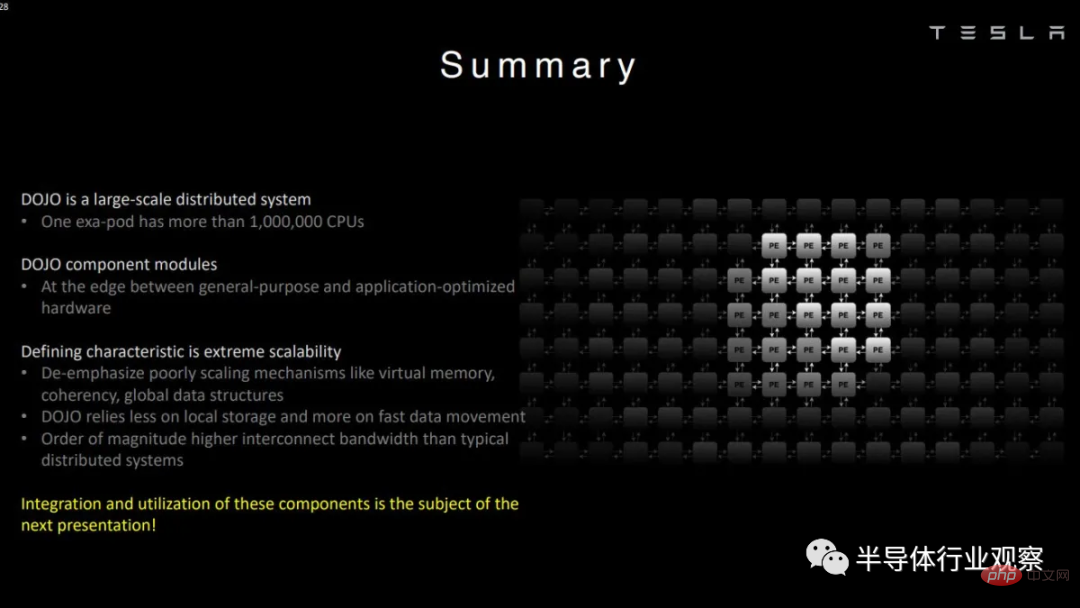

테슬라가 머신러닝에만 관심이 있다고 말하는 것은 절제된 표현일 것입니다. 실제로 전기차 제조업체는 기계 학습 모델 훈련에 최적화된 Dojo라는 자체 슈퍼컴퓨터를 구축했습니다.

다른 많은 슈퍼컴퓨터와 달리 Dojo는 AMD, Intel 또는 Nvidia 등의 상용 CPU 및 GPU를 사용하지 않습니다. Tesla는 요구 사항에 따라 마이크로 아키텍처를 설계하여 보다 범용적인 아키텍처에서는 불가능한 절충안을 만들 수 있었습니다.

이 기사에서는 Hot Chips에서 Tesla의 데모를 기반으로 한 아키텍처를 살펴보겠습니다. 아키텍처에는 별도의 이름이 없으므로 단순화를 위해 다음에서 Dojo를 언급할 때마다 아키텍처를 이야기합니다.

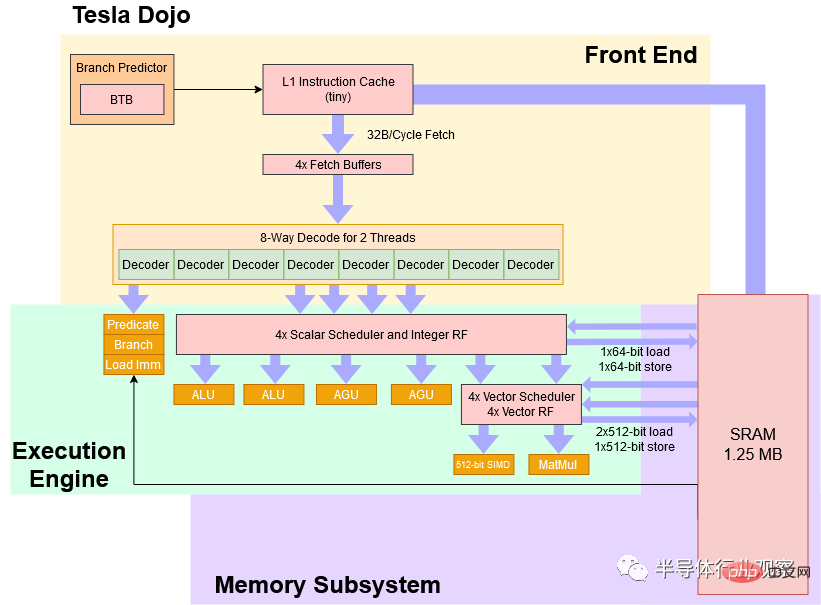

블록 다이어그램

높은 수준에서 Dojo는 보수적인 2GHz에서 실행되는 4방향 SMT가 있는 8와이드 코어이며, CPU 스타일 파이프라인을 사용하여 Dojo보다 다른 알고리즘에 더 잘 견딜 수 있습니다. GPU 및 분기 코드. Dojo의 명령어 세트는 스칼라 측면에서 RISC-V와 유사하지만 Tesla 엔지니어는 기계 학습 가속화에 초점을 맞춘 사용자 정의 벡터 명령어 세트를 추가했습니다.

Tesla Dojo 코어의 단순화된 블록 다이어그램

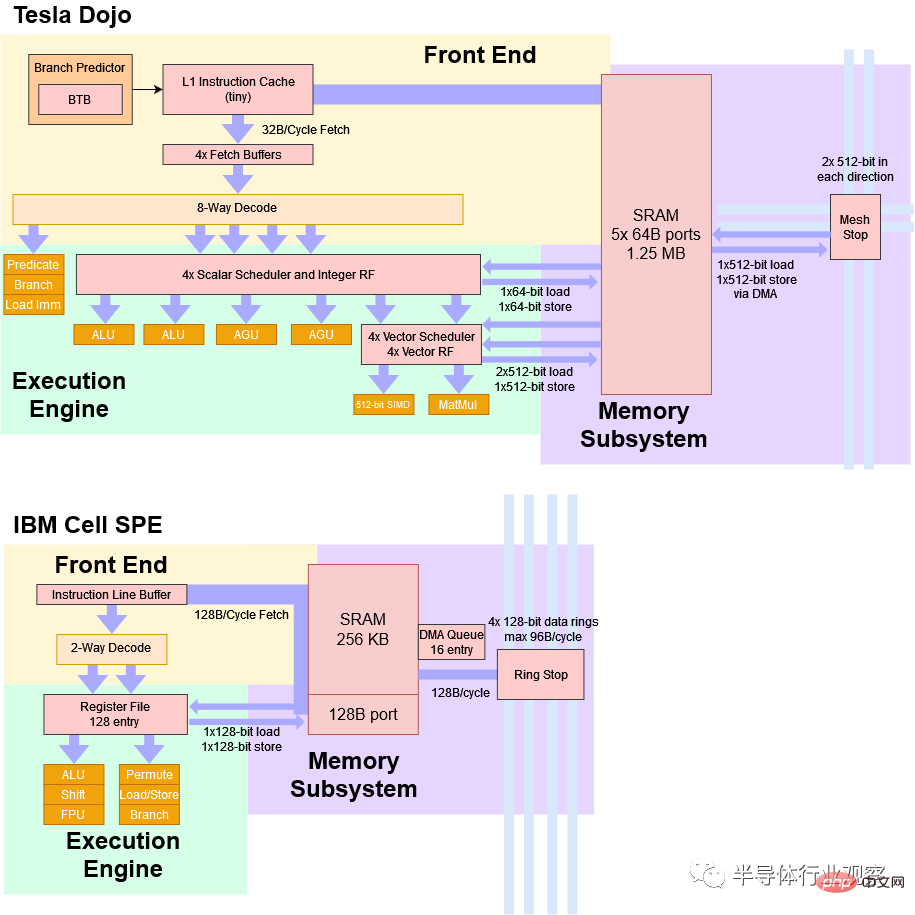

Tesla는 Dojo를 "고처리량의 범용 CPU"라고 설명합니다. 성능 관점에서 볼 때 여기에는 확실히 어느 정도 진실이 있습니다. 하지만 컴퓨팅 밀도를 높이기 위해 Tesla는 희생을 했고, Dojo 코어는 데스크톱, 노트북, 스마트폰에서 우리에게 익숙한 CPU에 비해 사용하기가 매우 어렵습니다. 어떤 면에서 Dojo 커널은 기존 범용 CPU 커널보다 IBM Cell의 SPE와 유사한 작업을 처리합니다.

셀의 SPE처럼요?

2000년대 중반에 출시된 IBM Cell 프로세서는 완전한 기능을 갖춘 CPU 코어("전력 처리 요소" 또는 PPE: 전력 처리 요소) 제어로 구성된 8개의 "시너지적 처리 요소" 또는 SPE를 갖추고 있습니다. 언뜻 보기에 Dojo는 SPE와 많은 유사점을 가지고 있습니다.

Dojo와 SPE는 모두 벡터 처리에 최적화되어 있으며 작업 분배를 위해 별도의 호스트 프로세서를 사용합니다. Dojo 또는 SPE에서 실행되는 코드는 시스템 메모리에 직접 액세스할 수 없습니다. 대신 애플리케이션은 주로 로컬 SRAM의 작은 부분에서 작동할 것으로 예상됩니다. 이 로컬 SRAM은 소프트웨어로 관리되며 캐시로 사용할 수 없습니다. 주 메모리의 데이터가 필요한 경우 DMA 작업을 사용하여 가져와야 합니다.

마지막으로 Dojo와 Cell의 SPE는 모두 가상 메모리를 지원하지 않습니다. 이것이 무엇을 의미하는지 자세히 알아보겠습니다. 간단히 말해서 멀티태스킹을 매우 어렵게 만듭니다.

Tesla Dojo와 IBM Cell SPE의 매우 간단한 비교

Dojo는 몇 가지 중요한 면에서 다릅니다. Dojo는 소규모 배포를 염두에 두고 설계되지 않았기 때문에 호스트 프로세서는 별도의 호스트 시스템에 있습니다. 이러한 호스트 시스템에는 인터페이스 프로세서가 포함된 PCIe 카드가 있으며 고속 네트워크 링크를 통해 Dojo 칩에 연결됩니다. 대조적으로 Cell의 메인 프로세서는 동일한 칩에 있습니다. 이를 통해 개별 Cell 칩을 개별적으로 배포할 수 있습니다. 이는 Dojo에서는 불가능한 일입니다.

Dojo의 1.25MB 로컬 SRAM 블록은 256KB SRAM만 있는 Cell SPE보다 훨씬 더 크고 대역폭도 더 높습니다. Cell의 256KB SRAM에는 사이클당 128B를 제공할 수 있는 포트가 하나만 있습니다. Dojo의 SRAM에는 5개의 64B 포트가 있습니다. 물론 아키텍처 목표는 매우 다릅니다. Dojo는 클럭이 넓고 클럭이 낮은 반면, Cell SPE는 클럭이 높도록 설계된 좁고 깊은 파이프라인을 가지고 있습니다.

프론트엔드: CPU 편의성 등

프론트엔드부터 시작하는 Dojo 파이프라인을 간략하게 소개하겠습니다. Tesla의 다이어그램에서 BTB(분기 대상 버퍼: 분기 대상 버퍼)를 보여주듯이 일종의 분기 예측자가 있습니다. Dojo는 벡터 실행에 다이 영역 지출을 우선시해야 하기 때문에 예측 기능은 AMD, ARM 및 Intel의 고성능 코어에서 볼 수 있는 수준에 도달하지 못할 수 있습니다. 그러나 기본 분기 예측자라도 예측자가 없는 것보다 크게 개선되었으며 Dojo의 분기 예측 기능은 분기된 코드나 더 큰 명령 공간을 처리할 때 GPU보다 더 나은 성능을 제공해야 합니다.

분기 예측기가 다음 명령 가져오기 포인터를 생성하면 Dojo는 "소형" 명령 캐시에서 스레드별 가져오기 버퍼로 주기당 32바이트를 가져올 수 있습니다. 이 명령어 캐시는 로컬 SRAM에 대한 명령어 대역폭 압력을 줄이는 데 도움이 되어 데이터 측이 가능한 한 적은 경합으로 SRAM에 액세스할 수 있도록 보장합니다. 또한 명령어 캐시가 일관되지 않습니다. 새 코드가 로컬 SRAM에 로드되면 새 코드로 분기하기 전에 명령 캐시를 플러시해야 합니다.

Hot Chips Presentation from Tesla

인출 버퍼에서 Dojo의 디코더는 2개의 스레드에서 사이클당 8개의 명령어를 처리할 수 있습니다. SMT가 있는 CPU는 일반적으로 사이클당 하나의 스레드를 처리하고 사이클 경계에서 스레드를 전환하기 때문에 "사이클당 스레드 2개"가 무엇을 의미하는지 약간 혼란스럽습니다. 어쩌면 Dojo는 디코더를 두 개의 클러스터로 분할하고 두 개의 스레드를 선택하여 각 루프에 데이터를 공급할 수도 있습니다. 이는 취해진 분기에 대한 디코딩 처리량 패널티를 줄일 수 있습니다.

디코딩하는 동안 특정 명령(예: 분기, 예측 작업 및 즉시 로드("목록 구문 분석"))이 프런트 엔드에서 실행되고 파이프라인에서 제거될 수 있습니다. 이는 이름 바꾸기에서 레지스터 간 복사본을 제거하는 최신 x86 CPU와 약간 비슷합니다. 하지만 들으셨죠. Dojo는 순서대로 폐기를 유지하기 위해 파이프라인을 통해 "제거" 지시사항을 추적하지 않습니다. 다른 프로세서는 명령 경계에서 중지하고 실행을 재개하는 데 필요한 모든 상태를 유지할 수 있도록 종료할 모든 것을 추적합니다. 이 기능을 "정확한 예외"라고 하며 최신 운영 체제에서는 이 기능을 사용하여 디스크에 페이징하거나 코드가 손상된 위치를 정확하게 알려주는 등 모든 종류의 유용한 기능을 제공합니다.

Tesla는 정확한 예외에는 관심이 없습니다. Dojo에는 "더 정확한" 예외를 제공하기 위해 더 많은 명령이 파이프라인을 통해 전달되는 디버그 모드가 있지만 일반적인 비순차적 CPU와 같은 순서대로 종료 논리는 없습니다.

Dojo의 실행 엔진

넓은 프런트 엔드를 본 후 ALU 2개와 AGU 2개만 있는 4폭 정수 실행 엔진을 보면 조금 이상할 수도 있습니다. 하지만 이 깔때기 모양의 파이프라인은 일부 명령이 프런트 엔드에서 실행되고 삭제되기 때문에 의미가 있습니다.

Dojo는 스칼라 정수 성능이 중요한 클라이언트 시스템에도 적용되지 않습니다. 따라서 정수 측은 벡터 및 행렬 셀을 계속 공급하기 위해 제어 흐름 및 주소 생성을 처리하는 데 충분한 처리량을 제공합니다.

Dojo의 벡터 및 행렬 실행 끝은 코어 파이프라인의 스칼라 실행 엔진 뒤에 배치되며 두 개의 실행 파이프라인이 있습니다. 두 개의 파이프라인이 별것 아닌 것 같지만 Dojo는 이러한 파이프라인 뒤에 매우 광범위한 실행 단위를 가지고 있습니다. 한 파이프라인은 512비트 벡터 실행을 수행할 수 있고 다른 파이프라인은 8x8x4 행렬 곱셈을 수행할 수 있습니다. 따라서 명령이 명시적 병렬성을 충분히 노출하는 한 Dojo는 특히 매트릭스 단위를 사용할 때 매우 높은 처리량을 달성할 수 있습니다. Tesla는 354개의 Dojo 코어가 있는 칩이 2GHz에서 362 BF16 TFLOPS를 달성할 수 있다고 주장합니다. 이는 각 코어가 사이클당 512 BF16 FLOPS를 수행할 수 있음을 의미합니다.

Dojo가 완전히 순서 없이 실행될 수 있는지 확실하지 않습니다. 그러나 Tesla는 정수 측이 벡터 측보다 훨씬 앞서 실행될 수 있다고 말했으며, 이는 스케줄러 중 하나가 가득 찰 때까지 멈추곤 했던 명령을 실행할 수 있음을 시사했습니다. 명령된 폐기가 부족하다는 것은 순서가 잘못된 실행 기능을 의미하기도 합니다.

일반적으로 비순차적 실행을 구현하는 것은 매우 복잡합니다. CPU가 명령을 순차적으로 실행해야 하기 때문입니다. AMD, ARM 및 Intel의 고성능 CPU는 대규모 재정렬 버퍼(및 기타 구조)를 사용하여 명령을 추적하여 해당 결과를 프로그램 순서대로 커밋할 수 있습니다. 즉, 프로그램이 0으로 나누기와 같은 어리석은 작업을 수행하는 경우 이러한 코어는 어떤 명령이 잘못되었는지 정확하게 보여줄 수 있습니다. 또한 오류 이전에는 모든 명령의 작업을 반영하지만 이후에는 반영하지 않는 CPU 상태를 표시할 수 있습니다. 이는 명령의 잘못된 원인을 수정하고 실행을 재개할 수 있음을 의미합니다. 도장은 이 능력을 포기합니다. 그 대신 Dojo는 파이프라인을 통해 각 명령을 추적하는 것과 관련된 전력 및 영역 오버헤드를 방지하여 결과가 프로그램 순서대로 전달되도록 합니다.

SRAM Access

일반적으로 여기서는 캐싱에 대해 이야기합니다. 그러나 Dojo는 시스템 메모리에 직접 액세스할 수 없으므로 SRAM의 1.25MB 블록에 대해 논의하겠습니다. 사이클당 2개의 512비트 로드를 처리할 수 있어 AVX-512 지원 Intel CPU와 일치하는 사이클당 대역폭을 제공합니다. Tesla는 SRAM에 5개의 512비트 포트(로드 포트 2개, 스토어 포트 1개, Stop-to-Grid 포트 2개)가 있다고 밝혔습니다. 그러나 스칼라 측에는 AGU가 두 개뿐입니다. 이는 아마도 코어가 사이클당 두 개의 512비트 로드와 하나의 512비트 저장소를 처리할 수 없음을 의미합니다.

Dojo의 로컬 SRAM 블록은 캐시되지 않기 때문에 데이터와 함께 저장된 태그 및 상태 비트가 필요하지 않습니다. 또한 SRAM에는 L1D 캐시가 없기 때문에 크기가 L2 캐시에 더 가깝더라도 병목 현상을 일으키지 않고 모든 로드 및 저장 명령을 처리할 수 있을 만큼 빨라야 합니다. SRAM을 캐시로 구현하지 않는 것이 Tesla가 지연 시간을 낮게 유지하는 방법일 수 있습니다. 오래 전 AMD의 Hammer 아키텍처를 되돌아보면 L1D 미스를 감지한 후 1MB의 L2에 액세스하는 데 8사이클이 걸렸다는 것을 알 수 있습니다(총 대기 시간은 12사이클). 1MB의 SRAM이 캐시로 사용되지 않고 직접 주소 지정되면 세 단계가 제거되어 대기 시간이 5주기로 줄어들 수 있습니다.

L2 캐시 액세스와 관련된 파이프라인 단계를 보여주는 이전 Hot Chips 프레젠테이션의 슬라이드입니다. L2가 캐시가 아닌 경우 건너뛸 수 있는 단계는 빨간색으로 표시됩니다.

수십년 간의 프로세스 노드 개선과 Athlon보다 훨씬 낮은 클럭 속도 목표를 고려하면 Tesla가 L1과 유사한 대기 시간으로 L2 크기 SRAM 블록에 어떻게 액세스할 수 있는지 쉽게 알 수 있습니다. L1 캐시를 건너뛰면 확실히 공간과 전력이 절약됩니다.

지연 시간, 영역 및 코어 복잡성을 더욱 줄이기 위해 Dojo는 가상 메모리를 지원하지 않습니다. 따라서 TLB 또는 페이지 탐색 메커니즘이 없습니다. 최신 운영 체제는 가상 메모리를 활용하여 각 프로세스에 고유한 메모리 보기를 제공합니다. 프로그램이 사용하는 메모리 주소는 물리 메모리 주소에 직접 접근하는 것이 아니라, 운영체제가 설정한 페이징 구조를 이용하여 CPU에서 물리 주소로 변환한다. 이것이 바로 최신 운영 체제가 프로그램을 서로 분리하고 오작동하는 응용 프로그램이 전체 시스템을 중단시키는 것을 방지하는 방법입니다.

가상 메모리는 물리적 메모리보다 더 많은 프로그램을 실행할 수 있는 방법이기도 합니다. 실제 메모리가 부족해지면 운영 체제는 페이지 매핑을 해제하고 이를 디스크에 쓴 다음 프로그램에 필요한 메모리를 제공합니다. 다른 형편없는 프로그램이 해당 메모리에 액세스하려고 하면 CPU는 가상 주소를 실제 주소로 변환하려고 시도하지만 변환이 존재하지 않음을 발견합니다. CPU는 페이지 오류 예외를 발생시킵니다. 운영 체제는 제거된 페이지를 물리적 메모리로 다시 읽고 페이지 테이블 항목을 채워 이를 처리합니다.

도장에서는 이 중 어떤 것도 불가능합니다. 커널의 4방향 SMT 기능은 멀티태스킹 성능을 향상시키는 것보다 단일 애플리케이션을 명시적인 병렬 처리에 노출시키는 데 더 중점을 둡니다. 예를 들어, 한 스레드는 벡터 계산을 수행하고 다른 스레드는 DMA를 통해 시스템 메모리에서 SRAM으로 데이터를 비동기적으로 로드할 수 있습니다.

설계를 더욱 단순화하기 위해 Dojo는 단 21개의 주소 비트만으로 SRAM의 주소를 지정할 수 있으며, 이는 Dojo의 AGU 및 주소 지정 버스를 단순화할 수 있습니다. 이러한 절충안을 통해 Tesla는 별도의 L1 데이터 캐시를 앞에 구현하는 것을 피할 수 있을 만큼 충분히 낮은 대기 시간으로 이 SRAM에 액세스할 수 있습니다.

Memory Access

시스템 메모리라고 하면 Dojo 칩은 메모리에 직접 연결되지 않습니다. 대신 HBM이 장착된 인터페이스 프로세서에 연결됩니다. 이러한 인터페이스 프로세서는 호스트 시스템과의 통신도 담당합니다.

25개의 독립적인 칩이 있는 Dojo 타일은 160GB의 HBM 메모리에 액세스할 수 있습니다. Tesla는 타일 경계를 넘어 각 칩 가장자리에서 900GB/s를 전송할 수 있다고 말합니다. 이는 4.5TB/s의 링크 대역폭에서 전송할 수 있음을 의미합니다. 액세스 인터페이스 프로세서 및 HBM. HBM에 액세스하려면 별도의 칩을 거쳐야 하기 때문에 액세스 지연 시간이 매우 길어질 수 있습니다.

작은데 어떻게 하나요?

Dojo는 최소한 일부 OoO 실행 기능, 적절한 벡터 처리량 및 행렬 곱셈 장치를 갖춘 8폭 커널입니다. 그러나 1.25MB의 로컬 SRAM을 사용하더라도 결국 매우 작은 코어가 됩니다. 이에 비해 Fujitsu의 A64FX는 동일한 프로세스 노드에서 두 배 이상의 영역을 차지합니다. 프로세서 설계는 올바른 절충안을 만드는 것입니다. Tesla는 다수의 코어를 칩에 담아 기계 학습 처리량을 극대화하고자 하므로 개별 코어는 작아야 합니다. 영역 효율성을 달성하기 위해 Dojo는 몇 가지 친숙한 기술을 사용합니다. 보수적인 2GHz에서 실행됩니다. 낮은 클럭 회로는 더 적은 면적을 차지하는 경향이 있습니다. 기본 분기 예측기와 작은 명령 캐시가 있을 수 있습니다. 프로그램의 코드 공간이 크거나 분기가 많은 경우 일부 성능이 저하됩니다.

하지만 Tesla는 내부 작업 부하를 실행하는 데 필요하지 않은 기능을 제거하여 전력 및 면적 사용량을 더욱 줄입니다. 데이터 측 캐싱을 수행하지 않고 가상 메모리를 지원하지 않으며 정확한 예외를 지원하지 않습니다.

그 결과 Intel 8086보다 여러 면에서 사용자 및 프로그래머 친화적이지 않으면서 최신 CPU 코어의 성능 유연성을 제공하는 프로세서 코어가 탄생했습니다. 코어 외에도 Tesla는 배포용으로 특별히 Dojo 칩을 설계하여 칩 면적을 대규모로 절약하고 있습니다.

물리적 구현

축소된 Dojo 코어는 D1이라는 매우 큰 645mm2 다이에 구현됩니다. 우리에게 익숙한 다른 칩과 달리 단일 Dojo 칩은 자급자족할 수 없습니다. DDR이나 PCIe 컨트롤러가 없습니다. 다이가 약 100ns의 지연 시간으로 인접한 다이와 통신할 수 있도록 하는 IO 인터페이스가 다이 가장자리 주변에 있습니다.

시스템 메모리에 액세스하려면 Dojo D1 칩이 온보드 HBM이 있는 인터페이스 프로세서와 통신해야 합니다. 인터페이스 프로세서는 PCIe를 통해 호스트 시스템에 연결됩니다(인터페이스 프로세서는 PCIe 카드에 설치됨). 이론적으로 최소 기능 Dojo 배치에는 Dojo 칩, 인터페이스 프로세서 카드 및 호스트 시스템이 포함됩니다. 그러나 Tesla는 규모감을 제공하기 위해 각각 25개의 다이가 포함된 모듈에 Dojo 다이를 배치합니다. Dojo D1 다이는 슈퍼컴퓨터를 위한 빌딩 블록으로 특별히 설계되었습니다.

이 전문화는 더 많은 다이 면적을 절약할 수 있습니다. Dojo D1은 DDR 및 PCIe 컨트롤러의 공간을 낭비하지 않습니다. 인접한 다이와 인터페이스하도록 설계된 외부의 맞춤형 IO 커넥터를 제외하고 다이의 대부분은 대규모 Dojo 코어가 차지합니다.

반대로 배포 유연성을 높이기 위해 설계된 칩은 IO에서 많은 공간을 소비합니다. AMD의 Zen 1 "Zeppelin" 칩은 이를 매우 잘 보여줍니다. Zeppelin은 DDR4 메모리, PCIe 장치, SATA 드라이브 및 USB 장치에 직접 연결할 수 있어 고객 요구 사항에 완벽하게 부합합니다. 서버에서는 IFOP 인터페이스를 통해 인접한 칩과 통신할 수 있습니다. IFOP 근처에 위치한 SRAM의 큰 덩어리는 스누프 필터일 수 있으며, 이는 높은 코어 수 설정에서 캐시 일관성을 효율적으로 유지하는 데 도움이 됩니다. Dojo는 코어 전반에 걸쳐 캐시 일관성을 유지하려고 시도하지 않으며 스누프 필터링을 위해 SRAM을 사용하지 않습니다.

ISSCC 2021에서 열린 AMD의 칩렛 데모에서

AMD는 "Zeppelin" 다이 영역의 약 44%를 코어 및 캐시 이외의 로직에 할당하여 이를 달성했습니다. 유연성. Dojo는 SRAM과 코어 이외의 용도로 다이 면적의 28.9%만을 사용합니다.

마지막 단어

Tesla Dojo 슈퍼컴퓨터 뒤에 있는 마이크로 아키텍처는 CPU의 분기 코드 처리 기능을 유지하면서 매우 높은 계산 밀도를 달성하는 방법을 보여줍니다. 거기에 도달하려면 현대적인 컴퓨팅 경험을 정의하는 대부분의 편안함을 포기해야 합니다. Dojo 코어를 중심으로 데스크탑을 가상으로 구축할 수 있다면 아마도 MS-DOS를 사용해 본 사람이라면 누구나 그 경험이 친숙하게 느껴질 것입니다. 동시에 여러 응용 프로그램을 실행할 수 없습니다. 오작동하는 응용 프로그램 하나로 인해 시스템을 재부팅해야 할 수도 있습니다. 프로그램을 실행하기에 충분한 RAM이 없으면 프로그램을 완전히 실행하는 것을 잊어버릴 수 있습니다(디스크에 페이징하지 않고).

그러나 이러한 절충안은 Tesla의 슈퍼컴퓨터에서 완벽하게 이해됩니다. Tesla는 실행 중인 여러 애플리케이션을 동시에 처리하기 위해 Dojo 코어가 필요하지 않으며 Dojo는 내부에서 신뢰할 수 있는 코드만 실행하면 됩니다. 따라서 Tesla는 가상 메모리 지원에 관심이 없습니다. 마찬가지로 Dojo에서 실행되는 기계 학습 프로그램은 특정 시스템을 염두에 두고 작성됩니다. 사용 가능한 것보다 더 많은 메모리가 필요할 수 있는 임의의 프로그램 배치는 없습니다. 즉, 메모리 오버커밋, 메모리 압축 또는 디스크 간 메모리 페이지 교환과 같은 기술을 허용하기 위해 정확한 예외(및 가상 메모리)가 필요하지 않습니다. 정확한 예외는 디버깅에도 유용하지만 Tesla는 별도의 디버그 모드를 통해 더 저렴한 방법으로 이를 수행합니다.

높은 컴퓨팅 밀도를 달성하기 위해 Tesla가 채택한 절충안은 소비자 또는 서버 CPU에서는 불가능하다는 것이 안전한 내기입니다. 그러나 그것들은 실제로 매우 재미있습니다. 그리고 우리는 Hot Chips에서 그것들을 선보일 시간을 내준 Tesla에게 감사해야 합니다. 지난 20년 동안 프로세스 노드의 개선이 둔화되어 단일 스레드 성능의 발전이 더욱 느려졌습니다. 전력 및 냉각 제약으로 인해 지난 5년 동안 멀티스레드 성능이 저하되었습니다. 그러나 더 많은 컴퓨팅 성능에 대한 요구가 줄어들지 않기 때문에 기업들은 이에 보조를 맞추기 위해 보다 전문화된 하드웨어로 눈을 돌리고 있습니다.

Tesla Dojo 슈퍼컴퓨터의 아키텍처는 계산 밀도를 높이기 위해 어떻게 절충하는지, 처리량이 제한된 애플리케이션을 위해 특수 하드웨어 도입을 선호하는 현재 추세를 보여주는 좋은 예입니다.

위 내용은 Tesla가 자체 개발한 칩 아키텍처에서 영감을 얻었습니다.의 상세 내용입니다. 자세한 내용은 PHP 중국어 웹사이트의 기타 관련 기사를 참조하세요!