このサイトの 4 月 5 日のニュースによると、ソースの Moore's Law is Dead は、最新のビデオで AMD Zen 5 プロセッサ実行エンジン (Execution Engine) に関する情報を共有し、真の 512 ビット浮動小数点を使用すると述べました。ユニット(FPU)。

ソースによって共有されたスライドによると、真の 512 ビット FPU を使用した Zen 5 の実行エンジンが詳細に説明されています。

AMD Zen 4 プロセッサーは、AVX-512 命令ワークロードの実行時にデュアルチャネル 256 ビット FPU を使用しますが、Zen 5 は実際の 512 ビット FPU を使用して 512 ビットを処理します。 AVX または VNNI 命令。

このサイトは、AMD が 512 ビット FPU に関連するコンポーネントをアップグレードし、L1 DTLB の容量を増加し、ロードストア キューを拡張し、L1 データ キャッシュの帯域幅を 2 倍にしたこともレポートから知りました。サイズが50%増加しました。 L1Dのサイズは、「Zen 4」の32KBから現在は48KBに増加しています。

FPU MADD レイテンシが 1 サイクル短縮されました。 FPU に加えて、AMD は整数実行パイプの数を 8 (Zen 4) から 10 に増やしましたが、コアあたりの専用 L2 キャッシュ サイズは依然として 1 MB です。

以上がAMD Zen 5 実行エンジンを公開: 真の 512 ビット FPU を使用の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

2025年にプレイするのに最適なJRPGApr 11, 2025 am 11:39 AM

2025年にプレイするのに最適なJRPGApr 11, 2025 am 11:39 AM2025年の最高のJRPG(日本のロールプレイングゲーム)は、劇場ストーリーテリングと活気に満ちたアンサンブルキャストを使用して、コントローラーを下に置いた後もずっと私たちと一緒にいる強力な体験を織ります。

最高のホラーゲーム:2025年にプレイする最も恐ろしいタイトルApr 11, 2025 am 11:09 AM

最高のホラーゲーム:2025年にプレイする最も恐ろしいタイトルApr 11, 2025 am 11:09 AM2025年の最高のホラーゲームは、プレイするのに最も心地よいものではないかもしれませんが、アドレナリンを急ぐことが保証されています。最近、ホラーゲームのジャンルに素晴らしい追加がありました。アラン・ウェイク2、バイオハザード4レマック

2025年のベストアサシン’のクリードゲーム:すべてのシリーズエントリがランク付けされていますApr 11, 2025 am 10:42 AM

2025年のベストアサシン’のクリードゲーム:すべてのシリーズエントリがランク付けされていますApr 11, 2025 am 10:42 AM最高の暗殺者のクリードゲームは、2025年にまだ維持され、歴史的な陰謀とステルスに焦点を当てたアクションの山を組み合わせています。そして、このシリーズは長年にわたって多くの変化を経験してきましたが、それはまだ周りの最大の名前の1つであり、たくさんあります

最高のクロスプレイゲーム2025:クロスプラットフォームの友達とのトップタイトルApr 11, 2025 am 09:41 AM

最高のクロスプレイゲーム2025:クロスプラットフォームの友達とのトップタイトルApr 11, 2025 am 09:41 AM2025年の最高のクロスプレイゲームは、どこでプレイしているかに関係なく、すべての友人と簡単にプレイできます。彼らはまた、最初からやり直さずに別のプラットフォームであなたのゲームを拾うのに役立ち、彼らは一緒に遊ぶことを示しています

Nintendo Switch 2 Pro Controller&ndashを事前注文する場所は次のとおりです。英国のファンはパッドを買うことができますが、米国のゲーマーは待たなければなりませんApr 11, 2025 am 09:02 AM

Nintendo Switch 2 Pro Controller&ndashを事前注文する場所は次のとおりです。英国のファンはパッドを買うことができますが、米国のゲーマーは待たなければなりませんApr 11, 2025 am 09:02 AM最近いくつかの地域でライブになったより広い任天堂スイッチ2プリオーダーと並んで、在庫が利用可能なファンは、新しい任天堂スイッチ2プロコントローラーを事前注文することもできます。

iPhoneで長い電子メールスレッドをミュートする方法Apr 10, 2025 pm 09:01 PM

iPhoneで長い電子メールスレッドをミュートする方法Apr 10, 2025 pm 09:01 PMAppleのMessagesアプリで忙しいグループチャットに参加すると、通知は速くなり、同じチャットスレッドで他の人ほど積極的に参加していないとすぐに面倒になります。そのため、Appleには沈黙するミュートオプションが含まれています

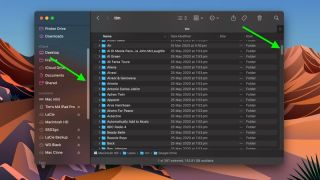

MacOS:Finderでクイックアクションを使用する方法Apr 10, 2025 pm 12:33 PM

MacOS:Finderでクイックアクションを使用する方法Apr 10, 2025 pm 12:33 PMMacos Mojaveが2018年に導入されたとき、AppleはFinderにクイックアクションを追加し、それらに関連付けられたアプリを開くことなくファイルの迅速な編集を簡単に実行できるようにしました。 Macos Venturaとその後、Appleはあなたができることを拡大しましたd

スクロールバーを常にMacOSで見えるようにする方法Apr 10, 2025 pm 12:17 PM

スクロールバーを常にMacOSで見えるようにする方法Apr 10, 2025 pm 12:17 PMMacos Ventura以来、Appleはオペレーティングシステムのデフォルトの動作を使用していないときに隠れ巻物バーを作成しましたが、どこを見るべきかを知っていれば、これが起こらないようにすることができます。それがどのように行われるかを学び続けてください

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

AI Hentai Generator

AIヘンタイを無料で生成します。

人気の記事

ホットツール

SublimeText3 Mac版

神レベルのコード編集ソフト(SublimeText3)

SublimeText3 中国語版

中国語版、とても使いやすい

ゼンドスタジオ 13.0.1

強力な PHP 統合開発環境

メモ帳++7.3.1

使いやすく無料のコードエディター

SAP NetWeaver Server Adapter for Eclipse

Eclipse を SAP NetWeaver アプリケーション サーバーと統合します。