トランジスタは「20世紀最大の発明」として知られています。

# その出現により、集積回路、マイクロプロセッサ、コンピュータ メモリの製造の基礎が築かれました。

#1965 年、「ムーアの法則」の提案は、数十年にわたって半導体業界の黄金律となりました。

これは、18 ~ 24 か月ごとに、マイクロチップにパッケージされるトランジスタの数が 2 倍になり、それに伴いチップの性能も 2 倍になることを示しています。

しかし、新しいプロセスノードの継続的な導入により、トランジスタ内の原子の数はますます減少しています。 、およびさまざまな物理的な極端な制限により、ムーアの法則のさらなる発展が制限されます。

# ムーアの法則は終わったと考える人さえいます。

したがって、ムーアの法則を「保存」するには、エンジニアはトランジスタ構造を変更し、面積と消費電力を削減し続け、その性能を向上させる必要があります。

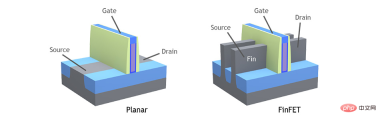

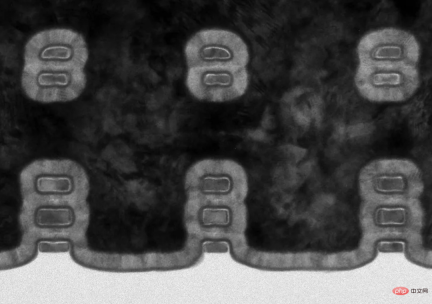

20 世紀後半には、主にプレーナー トランジスタ設計 (Planar Transistor) が普及しました。 2010 年代に入ると、平面デザインから 3D フィン型デバイスが徐々に置き換えられました。

#現在、全く新しいトランジスタ設計構造であるゲートオールアラウンドトランジスタ (GAA) が FinFET の後継となり、量産に入ろうとしています。 。

#しかし、さらに検討する必要があります。なぜなら、インテルが提案したこの新しいトランジスター・アーキテクチャーのRibbonFETでも、サイズを縮小する能力には限界があるからです。

3D 積層相補型金属酸化物半導体 (CMOS) または CFET (相補型電界効果トランジスタ) は、ムーアの法則を次の 10 年に拡張すると信じています。今年の鍵。

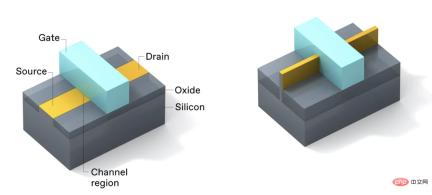

トランジスタの進化すべての金属酸化物半導体電界効果トランジスタ (MOSFET) には、同じ基本コンポーネントのセットがあります。

# ゲートスタック、チャネル領域、ソース、ドレイン

ソースとドレインは化学的にドーピングされているため、それらは可動電子が豊富であるか (n 型)、または可動電子が欠如している (p 型) かのいずれかです。チャネル領域には、ソースおよびドレインとは逆のドーピングが施されています。

2011 年以前の高度なマイクロプロセッサのトランジスタのプレーナ バージョンでは、MOSFET のゲート スタックはチャネル領域のすぐ上にありました。チャネル領域。

ゲートに (ソースに対して) 十分大きな電圧を印加すると、チャネル領域に移動電荷キャリアの層が形成され、電流が流れるようになります。ソースとドレインの間。

プレーナー トランジスタ設計のサイズを縮小するために、「短チャネル効果」が物理学者の焦点になっています。 。

#プロセス技術が向上し続けるにつれて、トランジスタのゲート電極の幅はますます狭くなっているためです。ご存知のとおり、ゲートが 20nm より低いと、電流が制御できなくなり、ソース電流がゲートを突き抜けてドレインに直接到達します。

#このとき「リーク」が発生し、チップの消費電力が急増します。

この問題を解決するために、新しい FinFET トランジスタ技術が提案されました。ゲートをチャネルの 3 つの側面で包み込み、より優れた静的制御を提供します。

FinFET は、前世代のプレーナ アーキテクチャと同じパフォーマンス レベルで消費電力を約 50% 削減します。 FinFET はスイッチング速度も速く、パフォーマンスが 37% 向上します。

#2011 年、インテルは 22nm ノードに FinFET を導入し、第 3 世代 Core プロセッサの生産に使用しました。

#それ以来、FinFET はムーアの法則の主力となりました。

#しかし、FinFET に移行したときに失ったものもあります。

#プレーナーデバイスでは、トランジスタの幅はフォトリソグラフィーによって定義されるため、非常に柔軟なパラメータになります。

#しかし、FinFET では、トランジスタ幅は一度に 1 つのフィンごとに個別に増分されます。このプロパティは、フィン量子化と呼ばれることがよくあります。

#FinFET の柔軟性にもかかわらず、フィンの量子化は依然として重要な設計上の制約です。それを取り巻く設計ルール、および性能を向上させるためにより多くのフィンを追加したいという要望により、論理セルの全体面積が増加し、単一のトランジスタを完全な論理回路に変える相互接続スタックが複雑になります。

# また、トランジスタの静電容量も増加するため、スイッチング速度が低下します。したがって、FinFET は業界の主力製品として私たちに十分に役立ってきましたが、より洗練された新しいアプローチが必要とされています。

# このアプローチが、物理学者を次期 3D トランジスタ、RibbonFET の発明に導いたのです。

#RibbonFET では、ゲートがトランジスタのチャネル領域を囲んで、電荷キャリアの制御を強化します。新しい構造により、パフォーマンスの向上とより洗練された最適化も可能になります。

具体的には、ゲートがチャネルを完全に取り囲み、ナノスケールのシリコンリボンフォームで作られたチャネル内の電荷キャリアをより厳密に制御します。

これらのナノリボン (ナノシート) を使用すると、フォトリソグラフィーを使用して必要に応じてトランジスタの幅を変更することが可能になります。

量子化制約が削除されると、アプリケーションに適切なサイズの幅を生成できます。これにより、電力、パフォーマンス、コストのバランスをとることができます。

#さらに重要なのは、スタックして並列動作させることで、デバイスはより多くの電流を駆動でき、面積を増やすことなくパフォーマンスを向上させることができます。

# したがって、インテルは、妥当な電力でより高いパフォーマンスを達成するには、RibbonFET が最良の選択であると考えています。

彼らは、2024 年に Intel 20A プロセスにリボン FET 構造を導入する予定です。

3D 積層型 CMOS

3D 積層型 CMOS

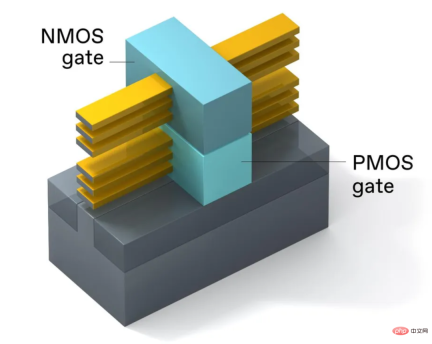

プレーナー、FinFET、RibbonFET トランジスタの共通点の 1 つは次のとおりです。前述したように、CMOS テクノロジーを使用して、CMOS は n 型トランジスタと p 型トランジスタで構成されます。この技術は、他の代替技術に比べて消費電流がはるかに少ないため、1980 年代に主流になりました。電流が少ないということは、動作周波数が高く、トランジスタ密度が高いことを意味します。 これまで、すべての CMOS テクノロジでは、NMOS トランジスタと PMOS トランジスタの標準ペアが並べて配置されていました。しかし、2019年のIEEE国際電子部品会議(IEDM)の基調講演では、PMOSトランジスタの上にNMOSトランジスタを配置する「3Dスタック」トランジスタの概念が提案された。 #IEDM 2020 では、この 3D テクノロジーを使用して設計された論理回路用の最初のインバーターがデバイスとして発表されました。 3D スタック型 CMOS は、インバータの設置面積を効果的に半分に削減し、トランジスタの面積密度を 2 倍にし、ムーアの法則の限界をさらに押し広げます。 PMOS デバイスを NMOS デバイスの上に配置した 3D 積層 CMOS 構造。総面積は、RibbonFET の面積と同じです。 NMOS ゲートと PMOS ゲートは異なる金属材料を使用します 3D 積層 CMOS を利用するには、解決すべきプロセス統合の課題が数多くあり、その中には CMOS の処理と製造が含まれます。限界です。 それを達成するにはどうすればよいですか?自己整合 3D CMOS の製造はシリコン ウェーハから始まります。ウェーハ上に、「超格子」と呼ばれるシリコンとシリコンゲルマニウムの層を次々と堆積させます。次に、フォトリソグラフィー パターンを使用して超格子の一部を切り取り、フィン状の構造を残します。超格子結晶は、その後の開発プロセスに強力なサポート構造を提供します。 次に、超格子を次の操作から保護するために、「偽の」ポリシリコンが超格子上に配置されます。このステップは、垂直に積層されたデュアル ソース/ドレイン プロセスとして知られ、上部ナノリボン (将来の NMOS サイト) の両端にリンドープ シリコンを成長させ、同時に下部ナノリボン (将来の PMOS サイト) にドープされたシリコンを選択的に成長させます。その後、誘電体が電源の周囲に配置され、放電によって電源が互いに絶縁されます。 #3D スタッキングにより、平方ミリメートルあたりの CMOS トランジスタの密度が効果的に 2 倍になります。実際の密度は、複雑さを伴うロジック セルに依存します。 。 #いよいよドアの施工です。まず、以前に取り付けられた偽のドアを取り外して、シリコン ナノリボンを露出させます。次に、シリコン ゲルマニウムのみがエッチングで除去され、トランジスタのチャネル領域である平行なシリコン ナノリボンの山が解放されます。 次に、非常に薄い絶縁層がナノリボンの 4 つの側面すべてにコーティングされますが、この絶縁層は非常に高い誘電率を持っています。ナノリボン チャネルは非常に小さいため、プレーナ トランジスタほど効率的に化学的にコーティングすることができません。 下部ナノリボンを金属で囲んで p ドープ チャネルを形成し、上部のナノリボンは別のナノリボンと n ドープ チャネルを形成します。このようにして、ゲートスタックが構築され、2 つのトランジスタが取り付けられます。 このプロセスは複雑に見えるかもしれませんが、別の手法 (順次 3D スタッキング) よりも優れています。後者を使用する場合、NMOS デバイスと PMOS デバイスは別々のウェーハに実装され、その後 2 つが一緒にされて、PMOS 層が NMOS ウェーハに転写されます。セルフアライン 3D 積層法は、加工工程が少なく、製造コストをより厳密に制御できます。 #そしてさらに重要なことに、このセルフアライメント方法は、2 つのウェーハを接続するときに発生する可能性のあるアライメントエラーも回避します。 3D スタック型 CMOS に必要な接続をすべて行うのは非常に困難です。以下のデバイス スタックからの電源接続が必要になります。設計上、NMOS デバイス [上] と PMOS デバイス [下] には別々のソース/ドレイン コンタクトがありますが、両方のデバイスは共通のゲートを共有します。 NMOS と PMOS 間の垂直間隔を最適化する必要があることに注意してください。短すぎると寄生容量が増加します。長すぎると、2 つのデバイス間の相互接続の抵抗が増加します。どちらの極端な状況でも、回路の速度が低下し、より多くの電力が消費されます。 アメリカの TEL Research Center が IEDM 2021 カンファレンスで発表したものなど、多くの設計研究では、3D CMOS の限られたスペース内に必要なすべての相互接続を提供することが提案されていますが、そうすることで大きな影響を受けることはありません。形成する論理セルの面積を増やします。この調査は、最適な相互接続オプションを見つける上でイノベーションの機会が数多くあることを示しています。 ストリップ電界効果トランジスタと 3D CMOS により、ムーアの法則を継続するための明確な道筋が得られます。この路線は少なくとも2024年以降まで延長される可能性がある。 #ムーアの法則の創始者であるゴードン・ムーアは、2005 年のインタビューで次のように認めました。 。」

### ####################彼は次のように述べています。 ################## トランジスタの製造プロセスが FinFET を経て、継続的な最適化が行われると、RibbonFET の時代が到来し、最終的には 3D へと移行します。積層型CMOSプロセスを開発したことで、ゴードン・ムーア氏もすぐに驚かれることが予想されます。 #########

ムーアの法則の未来

以上がトランジスタの生命線がここにあります: 3D 積層 CMOS、ムーアの法則はあと 10 年続くでしょうか?の詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

生成エンジン最適化に関するビジネスリーダーのガイド(GEO)May 03, 2025 am 11:14 AM

生成エンジン最適化に関するビジネスリーダーのガイド(GEO)May 03, 2025 am 11:14 AMGoogleはこのシフトをリードしています。その「AIの概要」機能はすでに10億人以上のユーザーにサービスを提供しており、誰もがリンクをクリックする前に完全な回答を提供しています。[^2] 他のプレイヤーも速く地位を獲得しています。 ChatGpt、Microsoft Copilot、およびPE

このスタートアップは、AIエージェントを使用して悪意のある広告となりすましアカウントと戦っていますMay 03, 2025 am 11:13 AM

このスタートアップは、AIエージェントを使用して悪意のある広告となりすましアカウントと戦っていますMay 03, 2025 am 11:13 AM2022年、彼はソーシャルエンジニアリング防衛のスタートアップDoppelを設立してまさにそれを行いました。そして、サイバー犯罪者が攻撃をターボチャージするためのより高度なAIモデルをハーネスするにつれて、DoppelのAIシステムは、企業が大規模に戦うのに役立ちました。

世界モデルがどのように生成AIとLLMの未来を根本的に再形成しているかMay 03, 2025 am 11:12 AM

世界モデルがどのように生成AIとLLMの未来を根本的に再形成しているかMay 03, 2025 am 11:12 AM出来上がりは、適切な世界モデルとの対話を介して、生成AIとLLMを実質的に後押しすることができます。 それについて話しましょう。 革新的なAIブレークスルーのこの分析は、最新のAIで進行中のForbes列のカバレッジの一部であり、

2050年5月:私たちは祝うために何を残しましたか?May 03, 2025 am 11:11 AM

2050年5月:私たちは祝うために何を残しましたか?May 03, 2025 am 11:11 AM労働者2050年。全国の公園は、ノスタルジックなパレードが街の通りを通り抜ける一方で、伝統的なバーベキューを楽しんでいる家族でいっぱいです。しかし、お祝いは現在、博物館のような品質を持っています。

あなたが聞いたことがないディープフェイク検出器はそれが98%正確ですMay 03, 2025 am 11:10 AM

あなたが聞いたことがないディープフェイク検出器はそれが98%正確ですMay 03, 2025 am 11:10 AMこの緊急かつ不安な傾向に対処するために、TEM Journalの2025年2月版の査読済みの記事は、その技術のディープフェイクが現在存在する場所に関する最も明確でデータ駆動型の評価の1つを提供します。 研究者

Quantum Talent Wars:The Hidden Crisis Treatenting Tech'の次のフロンティアMay 03, 2025 am 11:09 AM

Quantum Talent Wars:The Hidden Crisis Treatenting Tech'の次のフロンティアMay 03, 2025 am 11:09 AM新薬を策定するのにかかる時間を大幅に短縮することから、より環境に優しいエネルギーを生み出すまで、企業が新境地を破る大きな機会があります。 しかし、大きな問題があります:スキルを持っている人々が深刻な不足があります

プロトタイプ:これらの細菌は電気を生成できますMay 03, 2025 am 11:08 AM

プロトタイプ:これらの細菌は電気を生成できますMay 03, 2025 am 11:08 AM数年前、科学者は、特定の種類のバクテリアが酸素を摂取するのではなく、電気を生成することで呼吸するように見えることを発見しましたが、どのようにしたのかは謎でした。 Journal Cellに掲載された新しい研究は、これがどのように起こるかを特定しています:微生物

AIとサイバーセキュリティ:新政権の100日間の計算May 03, 2025 am 11:07 AM

AIとサイバーセキュリティ:新政権の100日間の計算May 03, 2025 am 11:07 AM今週のRSAC 2025会議で、SNYKは「The First 100 Days:How AI、Policy&Cybersecurity Collide」というタイトルのタイムリーなパネルを開催しました。ニコール・ペルロス、元ジャーナリストとパートネ

ホットAIツール

Undresser.AI Undress

リアルなヌード写真を作成する AI 搭載アプリ

AI Clothes Remover

写真から衣服を削除するオンライン AI ツール。

Undress AI Tool

脱衣画像を無料で

Clothoff.io

AI衣類リムーバー

Video Face Swap

完全無料の AI 顔交換ツールを使用して、あらゆるビデオの顔を簡単に交換できます。

人気の記事

ホットツール

Dreamweaver Mac版

ビジュアル Web 開発ツール

MinGW - Minimalist GNU for Windows

このプロジェクトは osdn.net/projects/mingw に移行中です。引き続きそこでフォローしていただけます。 MinGW: GNU Compiler Collection (GCC) のネイティブ Windows ポートであり、ネイティブ Windows アプリケーションを構築するための自由に配布可能なインポート ライブラリとヘッダー ファイルであり、C99 機能をサポートする MSVC ランタイムの拡張機能が含まれています。すべての MinGW ソフトウェアは 64 ビット Windows プラットフォームで実行できます。

PhpStorm Mac バージョン

最新(2018.2.1)のプロフェッショナル向けPHP統合開発ツール

SublimeText3 英語版

推奨: Win バージョン、コードプロンプトをサポート!

SAP NetWeaver Server Adapter for Eclipse

Eclipse を SAP NetWeaver アプリケーション サーバーと統合します。

ホットトピック

7943

7943 15

15 1652

1652 14

14 1412

1412 52

52 1303

1303 25

25 1250

1250 29

29