ホームページ >運用・保守 >Linuxの運用と保守 >Linux vcsとは何ですか

Linux vcsとは何ですか

- 藏色散人オリジナル

- 2023-04-10 10:55:391702ブラウズ

Linux vcs は、コンパイルされた Verilog シミュレーターであり、波形のシミュレーションと表示に使用されるツールです。これは、Windows 上の modelsim や Questasim などのツールや、quartus および vivado シミュレーション操作に似ています。

#このチュートリアルの動作環境: linux5.9.8 システム、Dell G3 コンピューター。

Linux vcs とは何ですか?

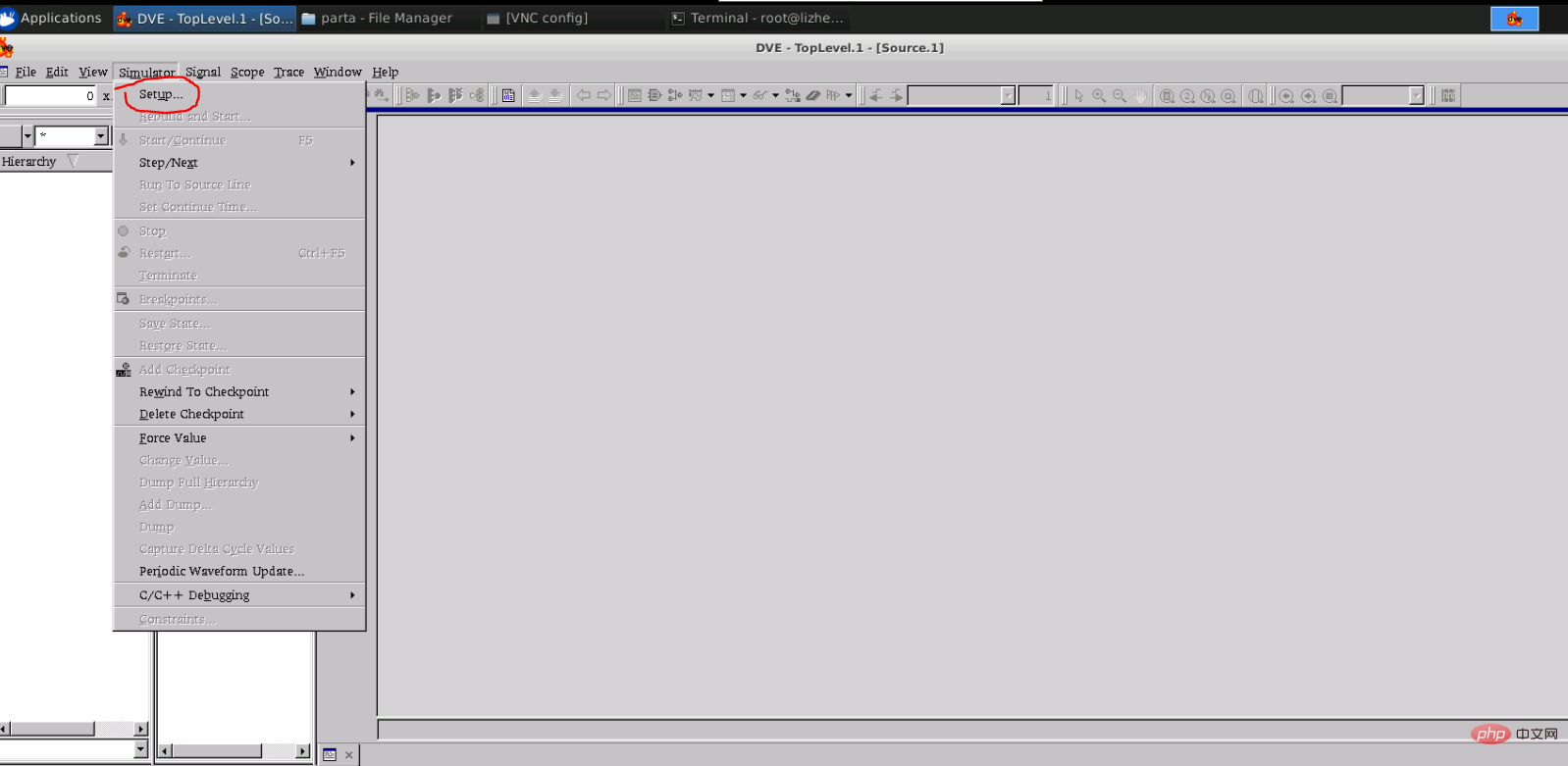

VCS ツールの基本的な使用方法

VCS は次のとおりです。 Linux で波形をシミュレーションおよび表示するために使用されるツールは、Windows での modelsim や Questasim などのツールや、quartus および vivado シミュレーション操作と似ています。

1.vcs の基本手順

vcs の一般的な命令サフィックス

| コマンド | 意味 |

|---|---|

-l readme.log |

は、生成された情報を編集するために使用されます。これをログ ファイルに配置します。 |

# v2k | # は、VCS を 2001 年以前の Verilog と互換性を持たせるための標準です。|

-debug_all |

|

.f ファイルのすべてのソース コードをコンパイルできます。 |

-R |

コンパイル直後に実行します。つまり、コンパイル直後に実行します。が完了しました./simv

|

-Mupdate |

ソース ファイルが変更されると、変更された ** のみが表示されます。 v* ファイルが再コンパイルされます * ので、コンパイル時間が節約されます。 |

-sverilog |

Systemverilog のサポートを有効にし、 | Systemverilogファイルのコンパイル時に使用します。 。 | -timescale=1ns/1ns

シミュレーション精度の設定 |

-o simv_file |

コンパイルによって生成される実行可能ファイルは、デフォルトでは simv ですが、 | -oを使用して実行可能ファイル名を変更できます。ここで変更すると、シミュレーション実行時に simv ではなく、対応する o 名が使用されます。 | #simv の一般的なコマンド

コマンド

以上がLinux vcsとは何ですかの詳細内容です。詳細については、PHP 中国語 Web サイトの他の関連記事を参照してください。

声明:

この記事の内容はネチズンが自主的に寄稿したものであり、著作権は原著者に帰属します。このサイトは、それに相当する法的責任を負いません。盗作または侵害の疑いのあるコンテンツを見つけた場合は、admin@php.cn までご連絡ください。