Maison >Périphériques technologiques >Industrie informatique >La mémoire HBM4 est en cours de développement et utilisera une interface plus large de 2048 bits

La mémoire HBM4 est en cours de développement et utilisera une interface plus large de 2048 bits

- 王林avant

- 2023-10-15 18:13:051393parcourir

Les nouvelles officielles de Samsung montrent que la mémoire HBM pour le calcul haute performance (HPC) a fait de nouveaux progrès. Le produit HBM3E à 9,8 Gbit/s a commencé à être échantillonné auprès des clients, tandis que la mémoire HBM4 devrait être lancée en 2025

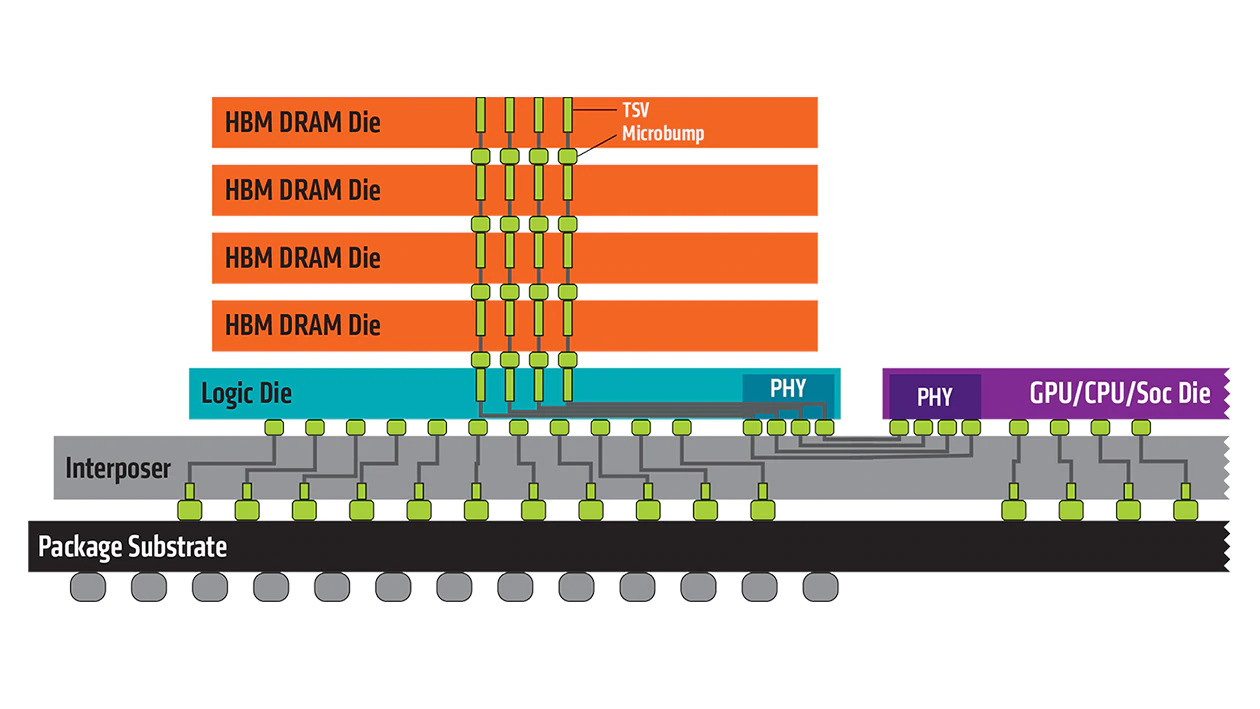

Bien qu'il n'y ait pas encore de spécifications officielles pour HBM4, TSMC a révélé certaines normes en cours de développement lors du forum OIP 2023. TSMC a déclaré qu'à l'avenir, la largeur de bit de l'interface de la mémoire HBM4 doublera pour atteindre 2048 bits

Il convient de mentionner que pour diverses raisons techniques, ils espèrent également le faire sans augmenter l'espace occupé par la pile de mémoire HBM. Atteindre cet objectif doublera également la densité d'interconnexion de la mémoire HBM de nouvelle génération sans augmenter davantage les vitesses d'horloge.

Selon le plan, cela permettra à HBM4 de réaliser des avancées majeures à plusieurs niveaux techniques

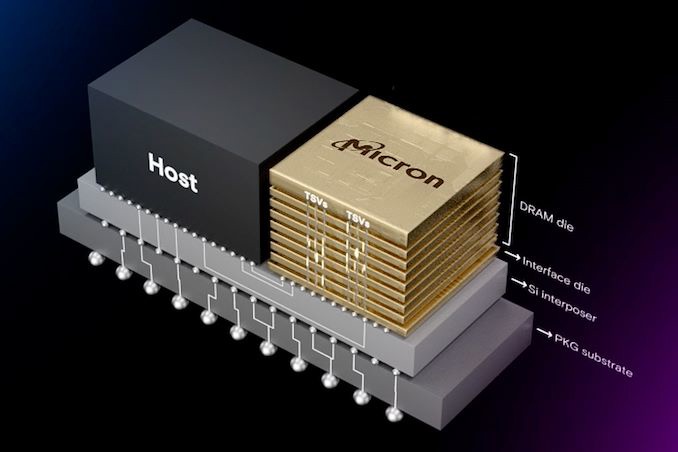

En termes d'empilement de DRAM, une interface mémoire de 2048 bits nécessite une augmentation significative du nombre de vias traversants en silicium. Dans le même temps, l'interface de la puce externe devra réduire le pas des bosses à moins de 55 microns et augmenter considérablement le nombre de micro-bosses (Remarque sur ce site : le HBM3 compte actuellement environ 3982 micro-bosses).

De plus, HBM4 adoptera le mode d'empilement 16-Hi, qui empile 16 puces mémoire dans un module, augmentant ainsi la complexité technique (bien que d'un point de vue technique, HBM3 prenne également en charge l'empilement 16-Hi, mais donc jusqu'à présent, aucun fabricant n'a adopté cette approche)

Tous ces nouveaux paramètres nécessitent à leur tour une approche collaborative plus étroite entre les fabricants de puces, les fabricants de mémoire et les entreprises d'emballage de puces pour garantir que tout se passe bien.

Lors de la conférence TSMC OIP 2023 à Amsterdam, Dan Kochpatcharin, responsable de la gestion de l'infrastructure de conception chez TSMC, a déclaré : « Parce qu'au lieu de doubler la vitesse, ils ont doublé les broches [de l'interface] [Avec HBM4] C'est pourquoi nous travaillons dur pour assurez-vous que nous travaillons avec les trois partenaires pour rendre leur HBM4 [disponible via notre emballage avancé] qualifié et assurez-vous que le RDL ou le médiateur ou tout ce qui se trouve entre les deux. Tout le contenu peut prendre en charge la mise en page et la vitesse de HBM4. Par conséquent, nous maintenons. coopération avec Samsung, SK Hynix et Micron. Les résultats sont à titre de référence uniquement. Tous les articles de ce site contiennent cette déclaration.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Quelle fréquence de mémoire le Intel Core i5-9400F prend-il en charge ?

- Qu'est-ce que la mémoire courante

- Que dois-je faire si mon ordinateur portable Samsung a un écran noir et ne répond pas lorsque je l'allume ?

- Les séries Samsung Galaxy Z Fold et Z Flip pourraient lancer des versions plus abordables

- Le chiffre d'affaires de Micron au quatrième trimestre fiscal 2023 a chuté de 40 % sur un an, avec une perte nette d'environ 1,43 milliard de dollars.