Maison >Périphériques technologiques >IA >NVIDIA utilise l'IA pour concevoir des circuits arithmétiques GPU, qui réduisent la surface de 25 % par rapport à l'EDA le plus avancé, le rendant plus rapide et plus efficace.

NVIDIA utilise l'IA pour concevoir des circuits arithmétiques GPU, qui réduisent la surface de 25 % par rapport à l'EDA le plus avancé, le rendant plus rapide et plus efficace.

- 王林avant

- 2023-04-12 21:13:072106parcourir

Une vaste gamme de circuits arithmétiques alimente les GPU NVIDIA pour permettre une accélération sans précédent de l'IA, du calcul haute performance et de l'infographie. Par conséquent, l’amélioration de la conception de ces circuits arithmétiques est essentielle pour améliorer les performances et l’efficacité du GPU. Et si l’IA apprenait à concevoir ces circuits ? Dans un récent article de NVIDIA, « PrefixRL : Optimization of Parallel Prefix Circuits using Deep Reinforcement Learning », les chercheurs ont démontré que l'IA peut non seulement concevoir ces circuits à partir de zéro, mais également que les circuits conçus par l'IA sont meilleurs que ceux conçus par l'état de l'art. Les outils d'automatisation de la conception électronique (EDA) de pointe sont plus petits et plus rapides.

Adresse papier : https://arxiv.org/pdf/2205.07000.pdf

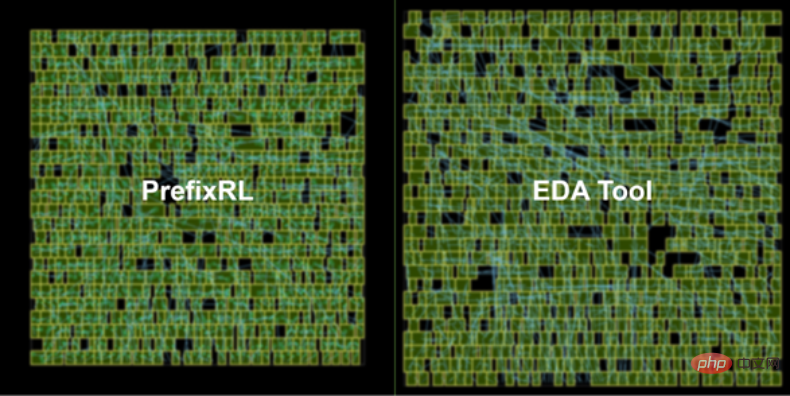

La dernière architecture GPU NVIDIA Hopper compte près de 13 000 exemples de circuits conçus par l'IA. Figure 1 ci-dessous : Le circuit additionneur 64b conçu par PrefixRL AI à gauche est 25 % plus petit que le circuit conçu par l'outil EDA le plus avancé à droite de la figure 1.

Aperçu de la conception des circuits

Les circuits arithmétiques dans les puces informatiques sont constitués d'un réseau de portes logiques (telles que NAND, NOR et XOR) et de fils. Un circuit idéal devrait avoir les attributs suivants :

- Petit : zone plus petite, plus de circuits peuvent être intégrés sur la puce ;

- Rapide : latence plus faible, performances de la puce améliorées ;

- Dans cette étude NVIDIA, les chercheurs se sont concentrés sur la surface du circuit et la latence. Ils ont constaté que la consommation d’énergie était étroitement liée à la zone du circuit d’intérêt. La surface du circuit et le délai sont souvent des propriétés concurrentes, il est donc souhaitable de trouver une frontière de Pareto pour une conception qui équilibre efficacement ces propriétés. Bref, les chercheurs espèrent que la surface du circuit soit minimisée à chaque retard.

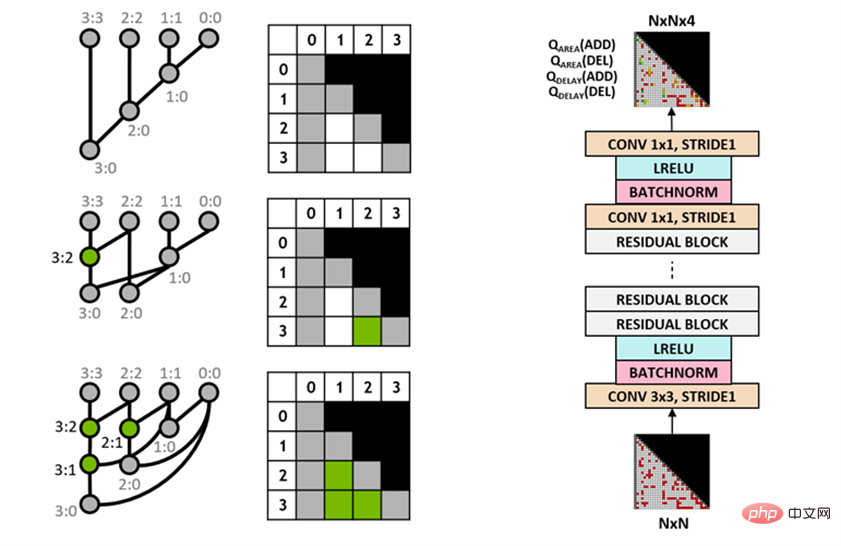

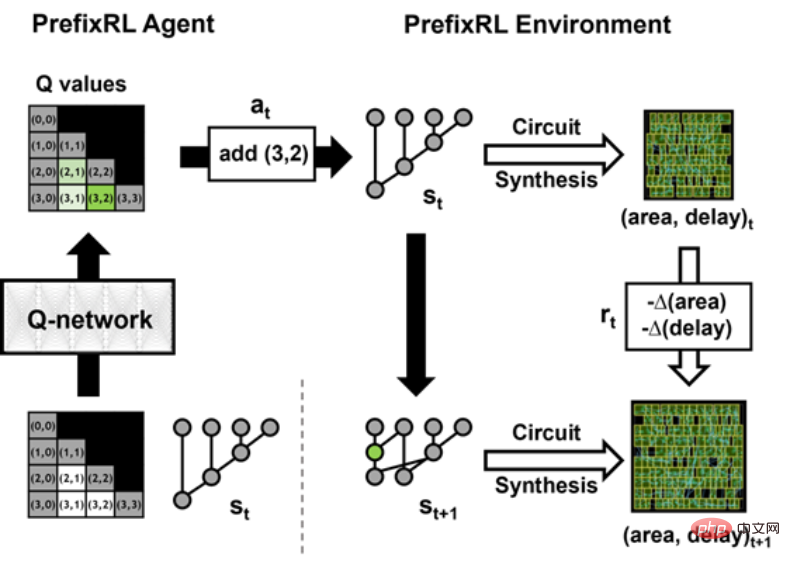

La question est alors : les agents d’IA peuvent-ils concevoir de bonnes cartes de préfixes ? L'espace d'état de tous les graphiques de préfixes est très grand O(2^n^n) et ne peut pas être exploré à l'aide de méthodes de force brute. La figure 2 ci-dessous montre une itération de PrefixRL avec une instance de circuit 4b.

Les chercheurs ont utilisé Circuit Generator pour convertir le diagramme de préfixe en un circuit avec des fils et des portes logiques. Ensuite, ces circuits générés sont optimisés grâce à un outil de synthèse physique qui utilise des optimisations de synthèse physique telles que la taille de porte, la duplication et l'insertion de tampon.

En raison de ces optimisations de synthèse physique, les propriétés finales du circuit (délai, surface et puissance) ne sont pas directement converties à partir des propriétés du graphique de préfixe d'origine (telles que les niveaux et le nombre de nœuds). C'est pourquoi l'agent IA apprend à concevoir des graphes de préfixes mais optimise les propriétés du circuit final généré à partir des graphes de préfixes.

Les chercheurs traitent la conception de circuits arithmétiques

comme une tâche d'apprentissage par renforcement (RL), dans laquelle un agent est formé pour optimiser la surface et les propriétés de retard du circuitarithmétique. Pour le circuit de préfixes, ils ont conçu un environnement dans lequel l'agent RL peut ajouter ou supprimer des nœuds dans le graphe de préfixes, puis effectuer les étapes suivantes : Le graphe de préfixes est normalisé pour toujours maintenir le calcul correct de la somme des préfixes ;

- Générer des circuits à partir de graphiques de préfixes normalisés ;

- Utiliser des outils de synthèse physique pour effectuer une optimisation de synthèse physique des circuits ;

- Mesurer la surface du circuit et les caractéristiques de retard.

- Dans l'animation suivante, l'agent RL construit le graphe de préfixes étape par étape en ajoutant ou en supprimant des nœuds. À chaque étape, l’agent est récompensé par des améliorations en termes de surface de circuit et de latence.

L'image originale est une version interactive.

Agent Q-learning entièrement convolutif

Les chercheurs utilisent l'algorithme Q-learning (Q-learning) pour entraîner la conception du circuit de l'agent. Comme le montre la figure 3 ci-dessous, ils décomposent le graphique de préfixe en une représentation en grille, où chaque élément de la grille est mappé de manière unique à un nœud de préfixe. Cette grille représente les entrées et sorties utilisées pour le réseau Q. Chaque élément de la grille d'entrée indique si le nœud existe ou non. Chaque élément de la grille de sortie représente la valeur Q d'un nœud ajouté ou supprimé.

Les chercheurs ont adopté une architecture de réseau neuronal entièrement convolutive car l'entrée et la sortie de l'agent d'apprentissage Q sont des représentations en grille. L'agent prédit les valeurs Q pour les attributs de zone et de retard séparément, car les récompenses pour la zone et le retard sont observables séparément pendant l'entraînement.

Figure 3 : représentation graphique du préfixe 4b (à gauche) et architecture d'agent Q-learning entièrement convolutive (à droite).

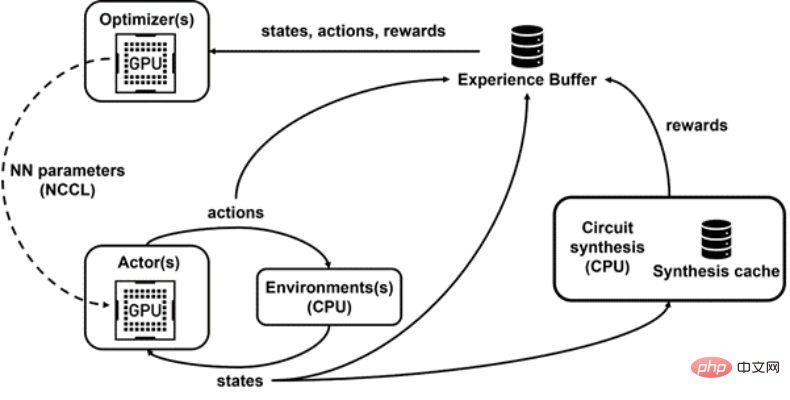

Raptor pour la formation distribuée

PrefixRL est gourmand en calcul, nécessitant 256 processeurs par GPU dans une simulation physique, et la formation d'une tâche 64b a nécessité plus de 32 000 heures GPU. Cette fois, NVIDIA a développé une plate-forme interne d'apprentissage par renforcement distribué, Raptor, qui exploite pleinement les avantages matériels de NVIDIA pour réaliser ce type d'apprentissage par renforcement au niveau industriel (Figure 4 ci-dessous).

Raptor peut améliorer l'évolutivité et la vitesse de formation des modèles de formation, tels que la planification des tâches, les réseaux personnalisés et les structures de données compatibles GPU. Dans le contexte de PrefixRL, Raptor permet une allocation hybride entre CPU, GPU et instances Spot. Les réseaux de cette application d'apprentissage par renforcement sont divers et bénéficient des éléments suivants :- Raptor bascule entre les NCCL pour un transfert point à point, transférant les paramètres du modèle directement du GPU de l'apprenant au GPU d'inférence

- Redis ; pour les messages asynchrones et plus petits, tels que les récompenses ou les statistiques ;

- pour les RPC compilés JIT, utilisés pour gérer des requêtes à volume élevé et à faible latence, telles que le téléchargement de données d'expérience.

Enfin, Raptor fournit des structures de données compatibles GPU telles que des tampons de relecture avec des services multithread pour recevoir les expériences de plusieurs travailleurs, regrouper des données en parallèle et les précharger sur le GPU.

La figure 4 ci-dessous montre que le framework PrefixRL prend en charge la formation et la collecte de données simultanées, et utilise NCCL pour envoyer efficacement les derniers paramètres aux participants (acteurs dans la figure ci-dessous).

Figure 4 : Les chercheurs utilisent Raptor pour découpler l'entraînement parallèle et le calcul de récompense afin de surmonter le retard de synthèse des circuits.

Calcul de la récompense

Les chercheurs ont utilisé un poids de compromis w (plage [0,1]) pour combiner les objectifs de zone et de retard. Ils entraînent divers agents avec des poids différents pour obtenir les frontières de Pareto, équilibrant ainsi le compromis entre surface et latence.

L'optimisation physiquement synthétisée dans un environnement RL peut générer diverses solutions qui compromettent la surface et la latence. Les chercheurs pilotent des outils de synthèse physique en utilisant les mêmes poids de compromis que ceux utilisés pour former des agents spécifiques.

L'optimisation de la synthèse physique dans la boucle de calcul des récompenses présente les avantages suivants :- L'agent RL apprend à optimiser directement les propriétés du circuit final des nœuds et des bibliothèques technologiques cibles

- L'agent RL est inclus dans la physique ; traiter la synthèse de la logique périphérique du circuit d'algorithme cible, optimisant ainsi conjointement les performances du circuit d'algorithme cible et de sa logique périphérique.

Cependant, faire de la synthèse physique est un processus lent (~ 35 secondes pour un additionneur 64b), ce qui peut ralentir considérablement l'entraînement et l'exploration RL.

Les chercheurs dissocient le calcul des récompenses des mises à jour d'état, car l'agent n'a besoin que de l'état actuel du graphique de préfixe pour agir, sans synthèse de circuit ni récompenses précédentes. Grâce à Raptor, ils peuvent confier de longs calculs de récompense à un pool de travailleurs CPU pour effectuer une synthèse physique en parallèle, tandis que les agents acteurs peuvent s'exécuter dans l'environnement sans attendre.

Lorsque le travailleur CPU renvoie la récompense, la transition peut être intégrée dans le tampon de relecture. Des récompenses complètes sont mises en cache pour éviter les calculs redondants lorsqu'un état est à nouveau rencontré.Résultats et perspectives

La figure 5 ci-dessous montre la zone et le retard du circuit additionneur 64b conçu à l'aide de PrefixRL et du circuit additionneur dominé par Pareto à partir des outils EDA les plus avancés.

Les meilleurs additionneurs PrefixRL atteignent 25 % de surface en moins que les additionneurs d'outils EDA avec la même latence. Ces graphiques de préfixes mappés sur des circuits additionneurs optimaux de Pareto après optimisation de la synthèse physique ont des structures irrégulières.

Figure 5 : Les circuits arithmétiques conçus par PrefixRL sont plus petits et plus rapides que les circuits conçus par des outils EDA de pointe.

(à gauche) architecture du circuit ; (à droite) diagramme des caractéristiques du circuit de l'additionneur 64b correspondant

Il est entendu qu'il s'agit de la première méthode utilisant des agents d'apprentissage par renforcement profond pour concevoir des circuits arithmétiques. NVIDIA envisage un modèle pour appliquer l'IA à des problèmes de conception de circuits du monde réel, créer des espaces d'action, des représentations d'état, des modèles d'agents RL, optimiser pour plusieurs objectifs concurrents et surmonter la lenteur des calculs de récompense.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Tendances technologiques à surveiller en 2023

- Comment l'intelligence artificielle apporte un nouveau travail quotidien aux équipes des centres de données

- L'intelligence artificielle ou l'automatisation peuvent-elles résoudre le problème de la faible efficacité énergétique des bâtiments ?

- Co-fondateur d'OpenAI interviewé par Huang Renxun : les capacités de raisonnement de GPT-4 n'ont pas encore atteint les attentes

- Bing de Microsoft surpasse Google en termes de trafic de recherche grâce à la technologie OpenAI