Maison >Périphériques technologiques >IA >Les détails de l'architecture du supercalculateur Tesla Dojo divulgués pour la première fois ! 'Fucked to Pieces' pour la conduite autonome

Les détails de l'architecture du supercalculateur Tesla Dojo divulgués pour la première fois ! 'Fucked to Pieces' pour la conduite autonome

- PHPzavant

- 2023-04-11 21:46:251472parcourir

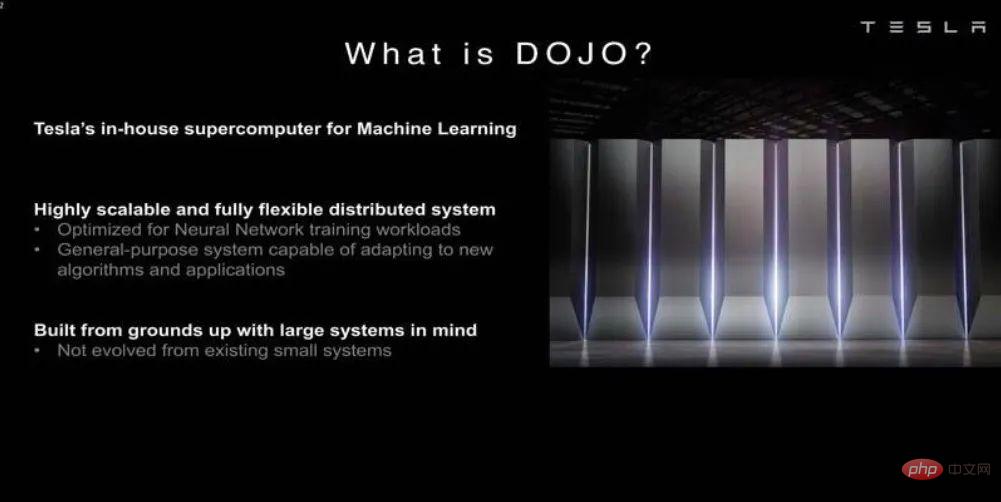

Pour répondre à la demande croissante de modèles d'intelligence artificielle et d'apprentissage automatique, Tesla a créé sa propre technologie d'intelligence artificielle pour apprendre aux voitures Tesla à conduire automatiquement.

Récemment, Tesla a divulgué de nombreux détails sur l'architecture de supercalcul Dojo lors de la conférence Hot Chips 34.

Essentiellement, Dojo est un superordinateur composable géant construit à partir d'une architecture entièrement personnalisée couvrant le calcul, la mise en réseau, les puces d'entrée/sortie (E/S) jusqu'à l'architecture du jeu d'instructions (ISA), la transmission de puissance, le conditionnement et le refroidissement. Tout cela est fait pour exécuter des algorithmes de formation d’apprentissage automatique personnalisés et spécifiques à grande échelle.

Ganesh Venkataramanan est le directeur principal du matériel de conduite autonome de Tesla, responsable du projet Dojo et de l'équipe de conception de processeurs d'AMD. Lors de la conférence Hot Chips 34, lui et un groupe d'ingénieurs en puces, systèmes et logiciels ont dévoilé pour la première fois de nombreuses caractéristiques architecturales de la machine.

Data Center "Sandwich"

"De manière générale, le processus que nous utilisons pour fabriquer des puces consiste à les mettre sur un emballage, à placer l'emballage sur le circuit imprimé, puis à entrer dans le système. Le système entre dans le support.", explique Venkataramanan.

Mais il y a un problème avec ce processus : chaque fois que les données passent de la puce au boîtier et hors du boîtier, il y a une latence et une perte de bande passante.

Pour contourner ces limitations, Venkataramanan et son équipe ont décidé de repartir de zéro.

Ainsi, les tuiles d’entraînement du Dojo sont nées.

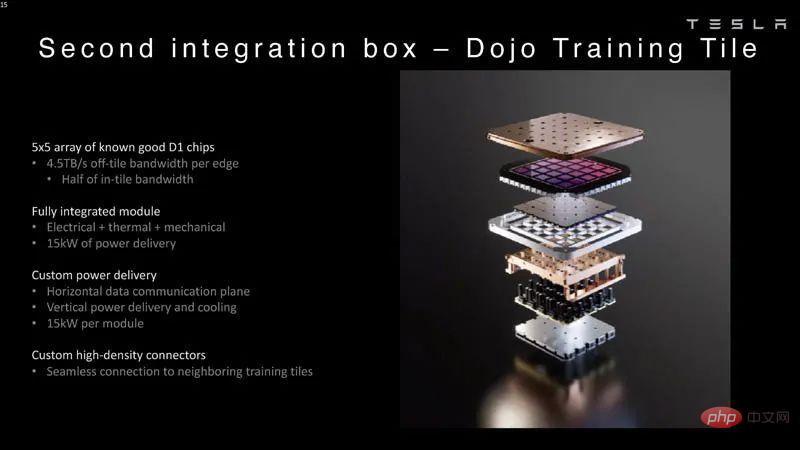

Il s'agit d'un cluster informatique autonome qui occupe un demi-pied cube et est capable de 556 TFLOPS de performances FP32 dans un boîtier de 15 kW refroidi par liquide.

Chaque tuile est équipée de 11 Go de SRAM et connectée via une structure de 9 To/s à l'aide d'un protocole de transfert personnalisé dans toute la pile.

Venkataramanan a déclaré : "Cette carte de formation représente un niveau d'intégration inégalé de l'ordinateur à la mémoire, en passant par l'alimentation électrique et la communication, sans avoir besoin de commutateurs supplémentaires.

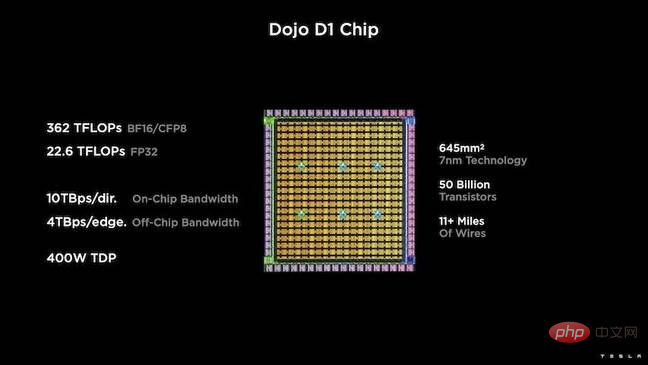

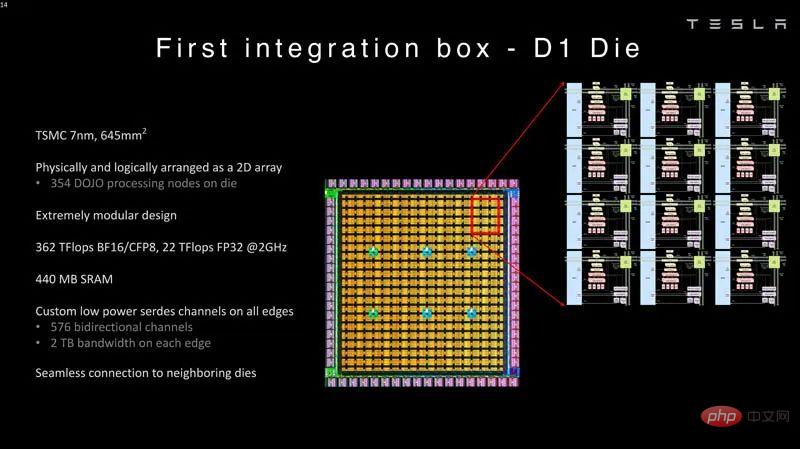

Le cœur de la tuile de formation est un." le D1 spécial de Tesla, qui est une puce de 50 milliards de transistors basée sur le processus 7 nm de TSMC. Tesla affirme que chaque D1 est capable d'atteindre 22TFLOPS de performances FP32 avec un TDP de 400W.

Tesla a ensuite pris 25 D1, les a divisés dans de bons moules connus, puis les a emballés à l'aide de la technologie système sur plaquette de TSMC avec une latence extrêmement faible et une bande passante extrêmement élevée permettant une intégration informatique massive.

Cependant, la conception du système et l'architecture d'empilement vertical sur la puce posent des défis en matière de fourniture d'énergie.

Selon Venkataramanan, la plupart des accélérateurs actuels placent l'alimentation directement à côté de la plaquette de silicium. Il a expliqué que cette approche, bien qu'efficace, signifiait qu'une grande partie de l'accélérateur devait être dédiée à ces composants, ce qui n'était pas pratique pour Dojo. Par conséquent, Tesla a choisi de fournir de l’énergie directement par le bas de la puce.

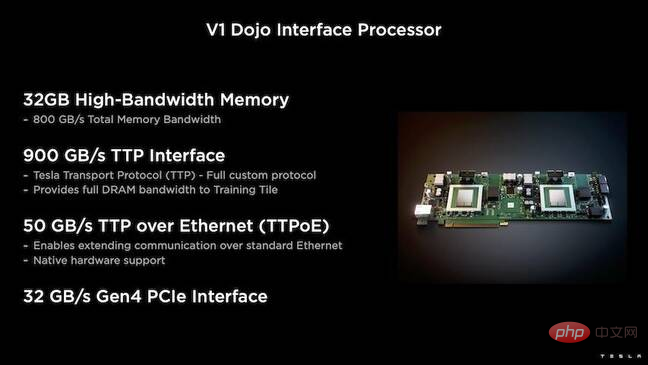

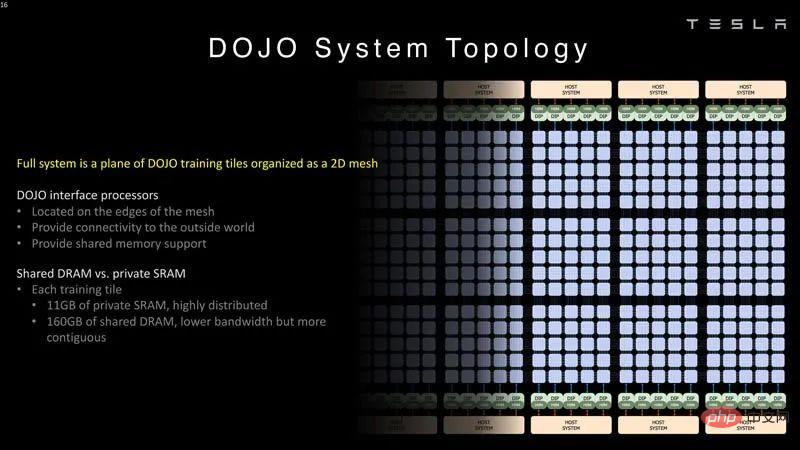

De plus, Tesla a développé le Dojo Interface Processor (DIP), qui est le pont entre le CPU hôte et le processeur de formation.

Chaque DIP dispose de 32 Go de HBM et jusqu'à cinq de ces cartes peuvent être connectées à une tuile de formation à 900 Go/s pour un total de 4,5 To/s pour un total de 160 Go par tuile HBM.

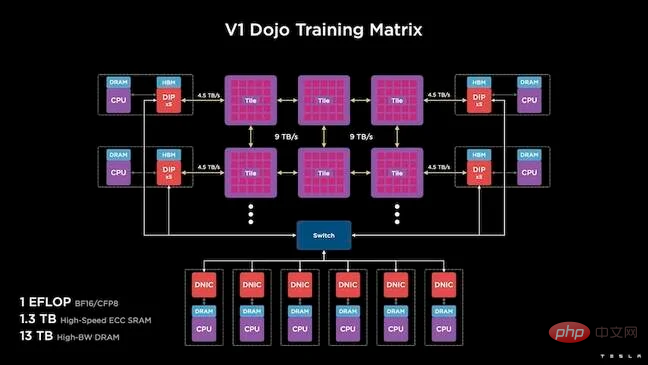

La configuration V1 de Tesla associe ces tuiles – ou 150 matrices D1 – dans un tableau pour prendre en charge quatre processeurs hôtes, chacun équipé de cinq cartes DIP, pour atteindre la revendication d'un exaflop de performances BF16 ou CFP8.

Logiciel

Une telle architecture informatique spécialisée nécessite une pile logicielle spécialisée. Cependant, Venkataramanan et son équipe ont reconnu que la programmabilité déterminerait le succès ou l'échec du Dojo.

"Lorsque nous concevons ces systèmes, la facilité de programmation par les pairs logiciels est primordiale. Les chercheurs n'attendent pas que vos développeurs écrivent un noyau écrit à la main pour s'adapter aux nouveaux algorithmes que nous voulons exécuter

." Pour ce faire, Tesla a abandonné l'idée d'utiliser un noyau et a conçu l'architecture de Dojo autour d'un compilateur.

"Ce que nous faisons, c'est utiliser PiTorch. Nous créons une couche intermédiaire qui nous aide à paralléliser pour faire évoluer le matériel en dessous. Sous tout se trouve du code compilé." Pour créer un cadre qui peut s'adapter à tout travail futur, une pile logicielle chargée, c'est le seul moyen.

Tout en soulignant la flexibilité du logiciel, Venkataramanan a souligné que la plateforme qui fonctionne actuellement dans son laboratoire est pour le moment limitée à Tesla.

Vue d'ensemble de l'architecture du Dojo

Après avoir lu ce qui précède, examinons de plus près l'architecture du Dojo.

Tesla dispose d'un système d'intelligence artificielle exascale pour l'apprentissage automatique. Tesla dispose de suffisamment de capital pour embaucher des employés et construire des puces et des systèmes spécifiquement pour ses applications, tout comme les systèmes embarqués de Tesla.

Tesla construit non seulement sa propre puce IA, mais aussi un supercalculateur.

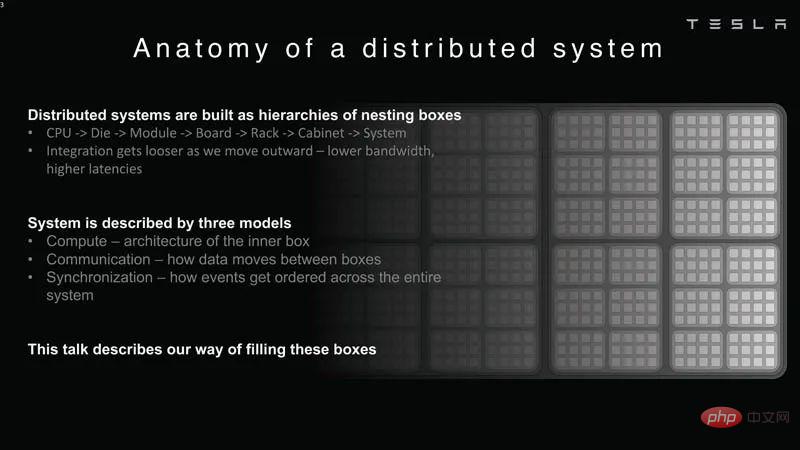

Analyse du système distribué

Chaque nœud de Dojo possède son propre processeur, mémoire et interface de communication.

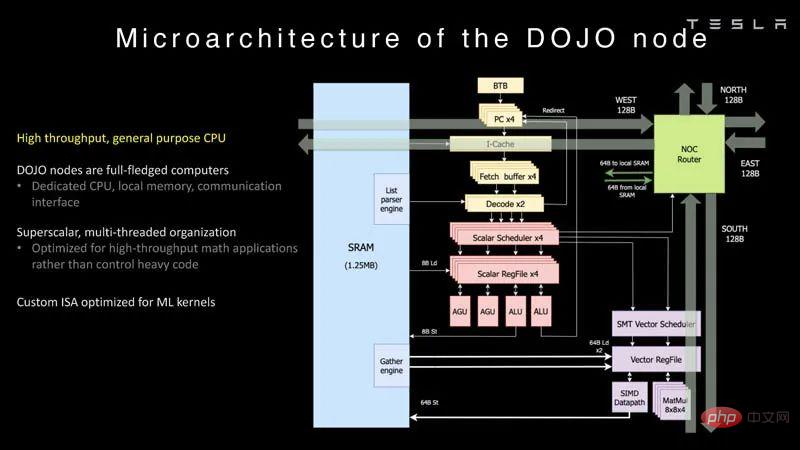

Dojo Node

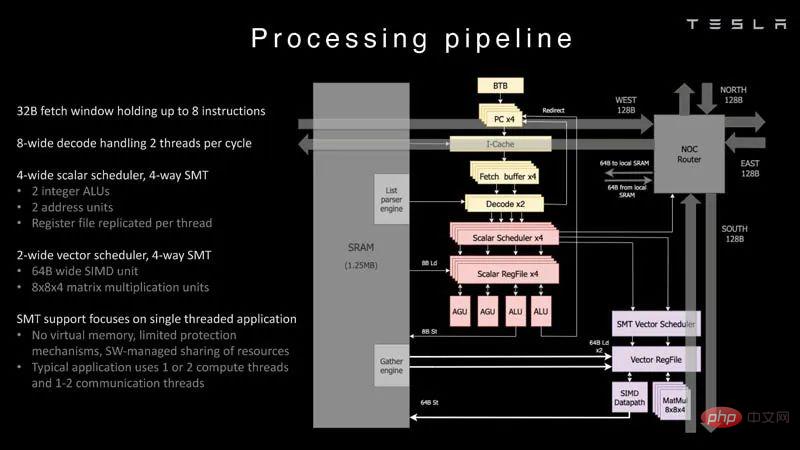

Il s'agit du pipeline de traitement du processeur Dojo.

Pipeline de traitement

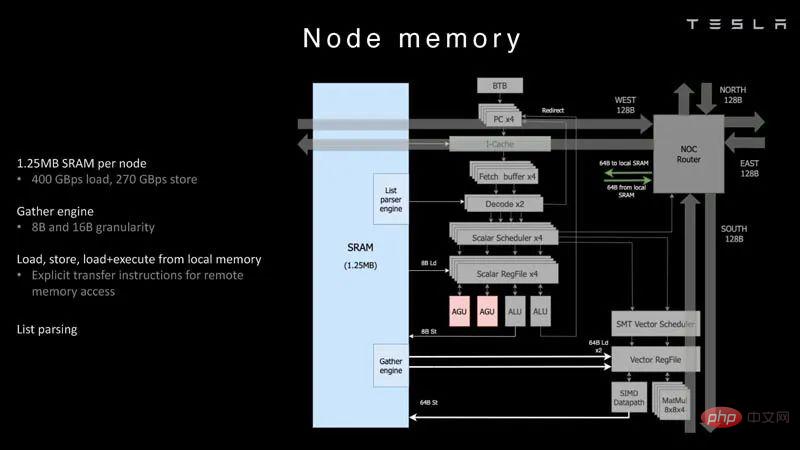

Chaque nœud dispose de 1,25 Mo de SRAM. Dans les puces de formation et d’inférence de l’IA, une technique courante consiste à colocaliser la mémoire avec le calcul afin de minimiser les transferts de données, qui sont très coûteux du point de vue de la puissance et des performances.

Node Memory

Ensuite, chaque nœud est connecté à une grille 2D.

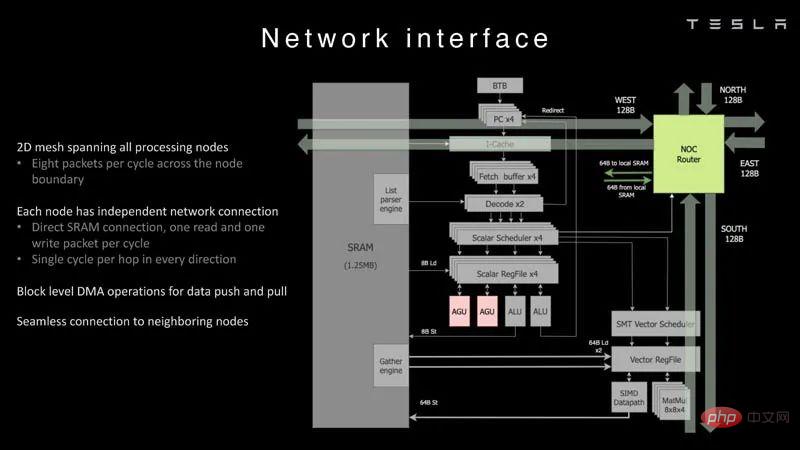

Interface réseau

Ceci est un aperçu du chemin des données.

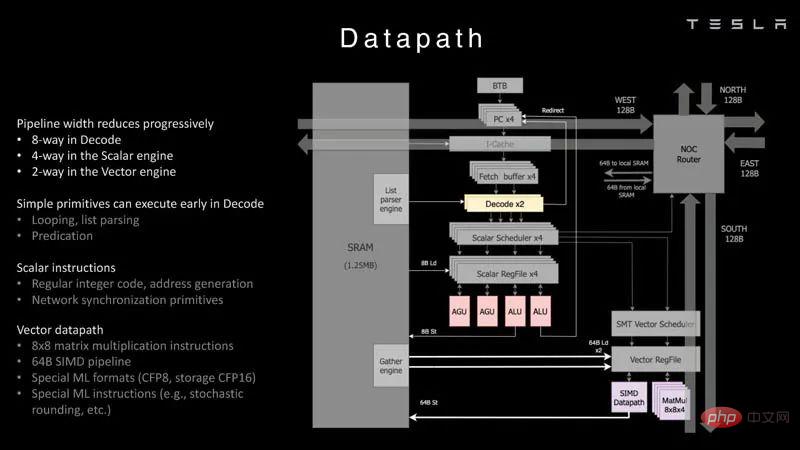

Chemin de données

Voici un exemple de compréhension de liste que la puce peut faire.

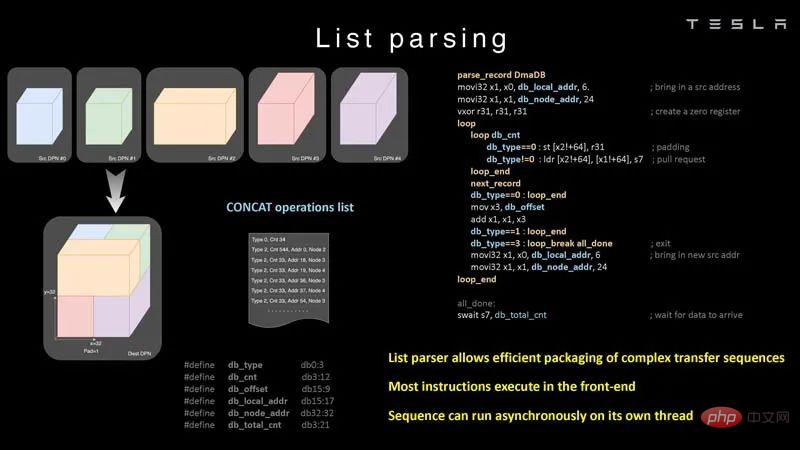

List Parsing

Voici plus sur le jeu d'instructions, original de Tesla, plutôt que sur le jeu d'instructions d'un CPU/GPU Intel, Arm, NVIDIA ou AMD typique.

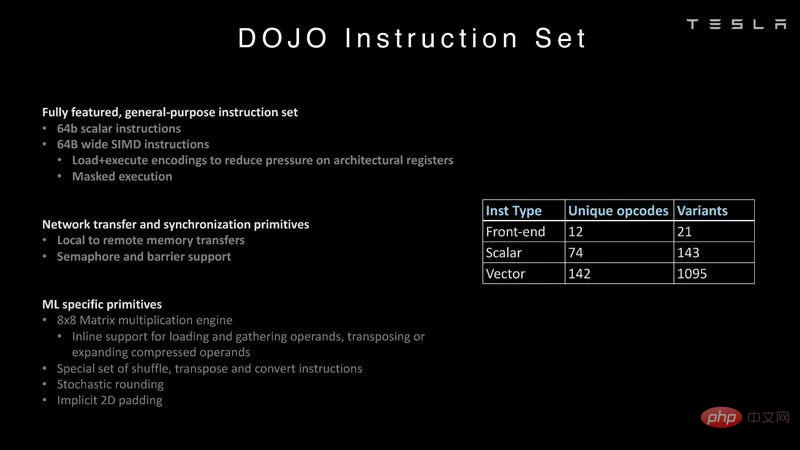

Jeu d'instructions

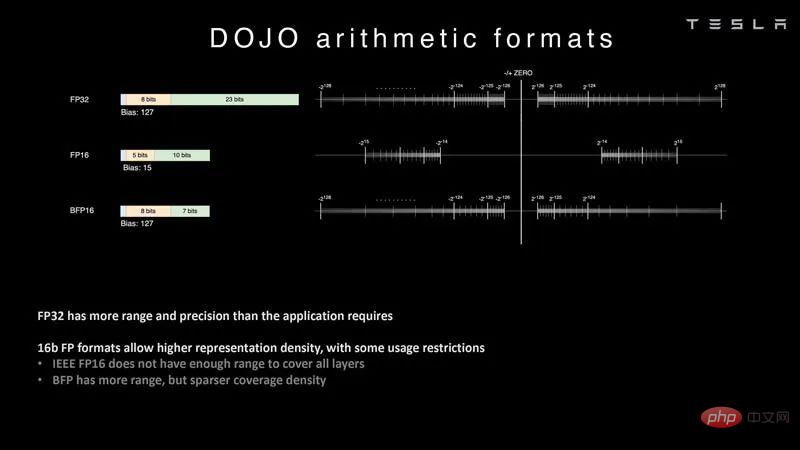

Dans l'intelligence artificielle, les formats arithmétiques sont importants, en particulier les formats pris en charge par la puce. Grâce à DOJO, Tesla peut étudier des formats courants tels que FP32, FP16 et BFP16. Ce sont des formats courants dans l’industrie.

Format arithmétique

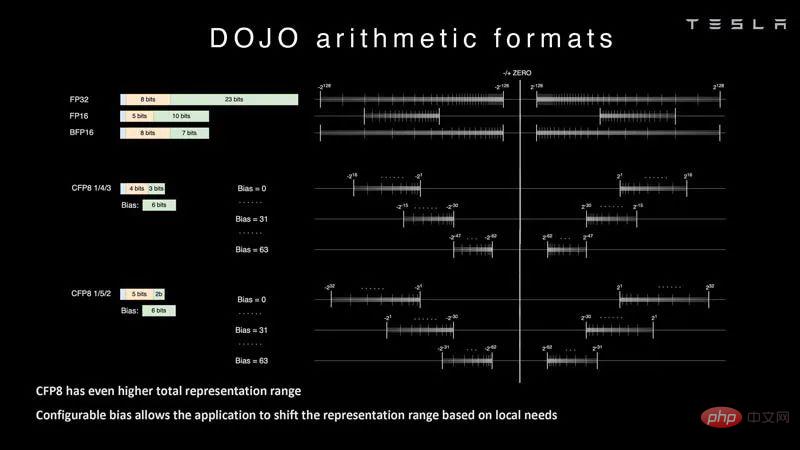

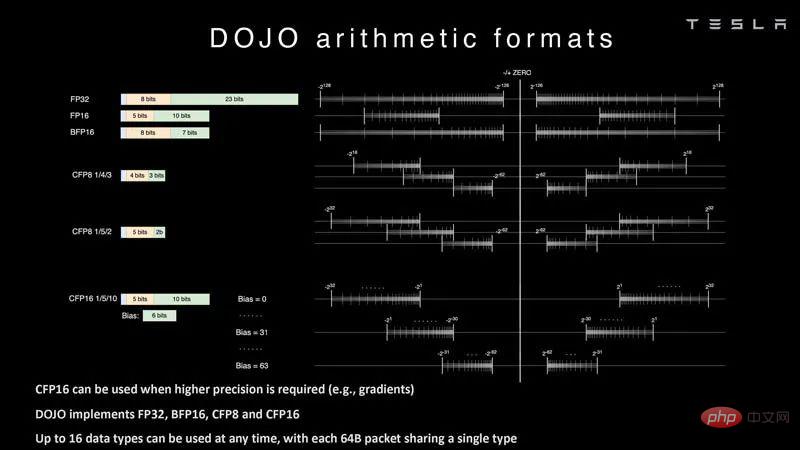

Tesla travaille également sur le FP8 ou CFP8 configurable. Il est disponible en options de gamme 4/3 et 5/2. Ceci est similaire à la configuration NVIDIA H100 Hopper du FP8. Nous voyons également l'accélérateur d'IA de base Untether.AI Boqueria 1458 RISC-V se concentrant sur différents types de FP8.

Format arithmétique 2

Dojo propose également différents formats CFP16 pour une plus grande précision et prend en charge FP32, BFP16, CFP8 et CFP16.

Format Arithmétique 3

Ces noyaux sont ensuite intégrés dans le moule fabriqué. La puce D1 de Tesla est fabriquée par TSMC selon un processus de 7 nm. Chaque puce dispose de 354 nœuds de traitement Dojo et de 440 Mo de SRAM.

Première boîte d'intégration D1 Mold

Ces puces D1 sont emballées sur une tuile d'entraînement dojo. Les puces D1 sont testées puis assemblées en une tuile 5×5. Ces tuiles ont une bande passante de 4,5 To/s par bord. Ils ont également une enveloppe de puissance de 15 kW par module, soit environ 600 W par puce D1 après soustraction de la puissance utilisée par les 40 matrices d'E/S. La comparaison montre pourquoi quelque chose comme Lightmatter Passage serait plus attrayant si une entreprise ne souhaitait pas concevoir une telle chose.

Boitier d'intégration secondaire Tuile de formation Dojo

Le processeur d'interface du Dojo est situé en bordure de la grille 2D. Chaque bloc de formation dispose de 11 Go de SRAM et de 160 Go de DRAM partagée.

Topologie du système Dojo

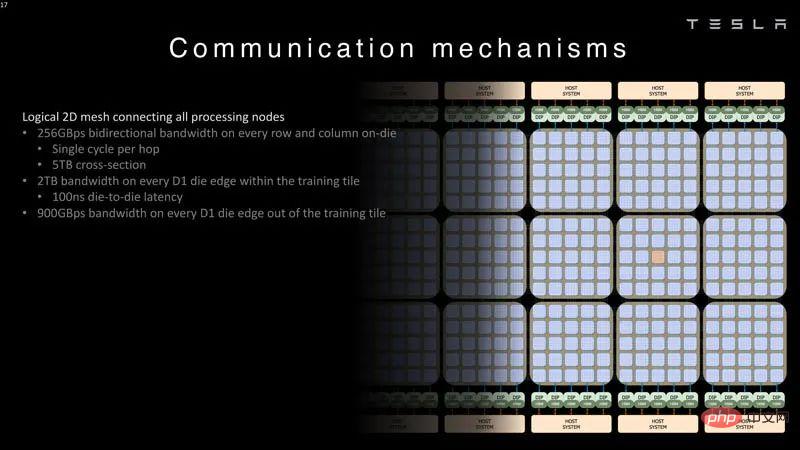

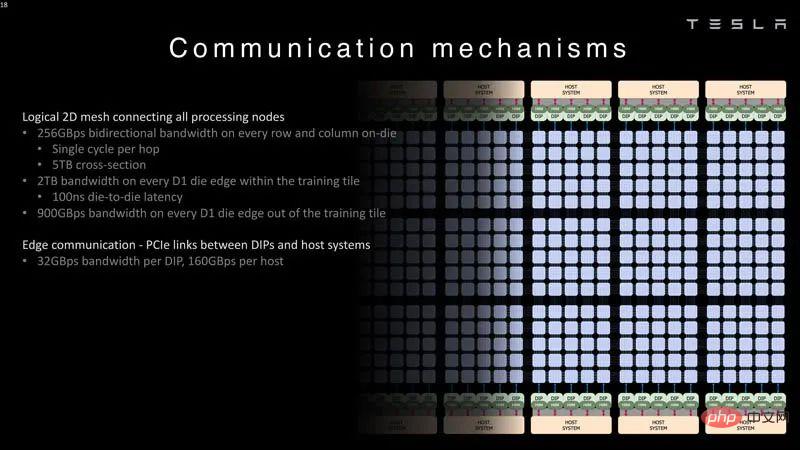

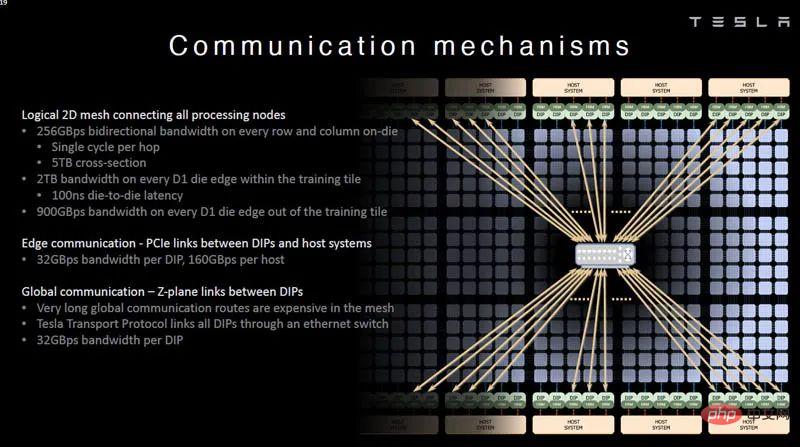

Ce qui suit sont les données de bande passante pour la grille 2D reliant les nœuds de traitement.

Grille 2D logique de communication du système Dojo

Chaque système DIP et hôte fournit une liaison de 32 Go/s.

Communication système Dojo Liaison PCIe DIP et hôte

Tesla propose également des liaisons Z-plane pour les itinéraires plus longs. Dans le reste du discours, Tesla a parlé d’innovation au niveau du système.

Mécanisme de communication

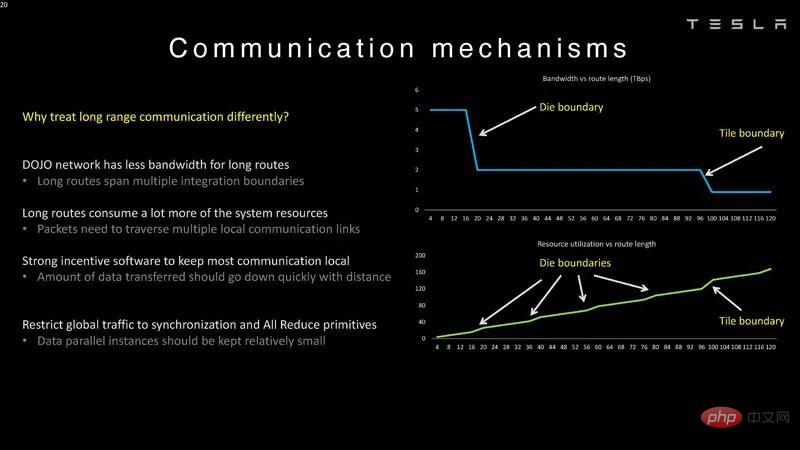

Voici les limites de latence pour les dés et les tuiles, c'est pourquoi elles sont traitées différemment dans Dojo. La raison pour laquelle les liaisons dans le plan Z sont nécessaires est que les longs chemins sont coûteux.

Mécanisme de communication du système Dojo

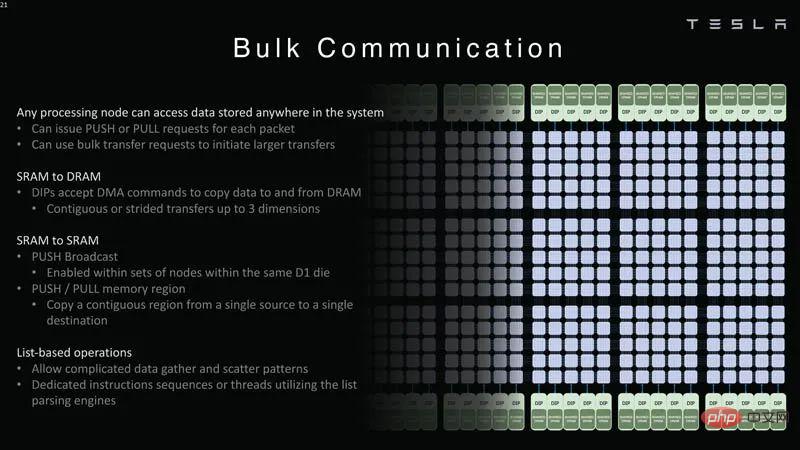

Tout nœud de traitement peut accéder aux données à travers le système. Chaque nœud peut transmettre ou extraire des données vers SRAM ou DRAM.

Communication par lots du système Dojo

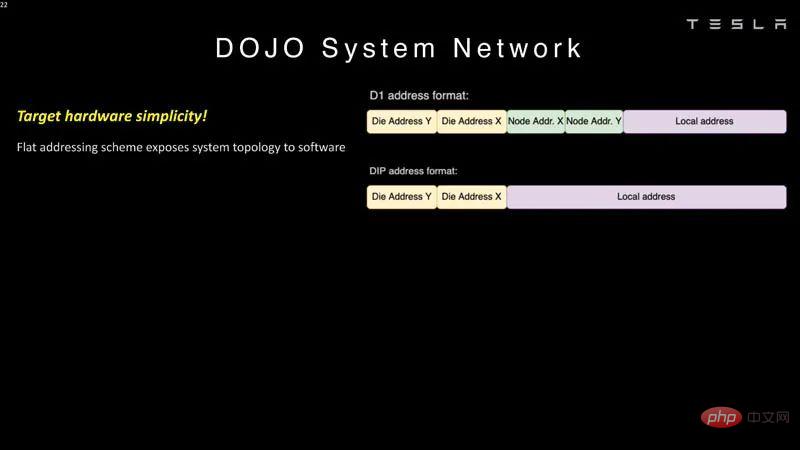

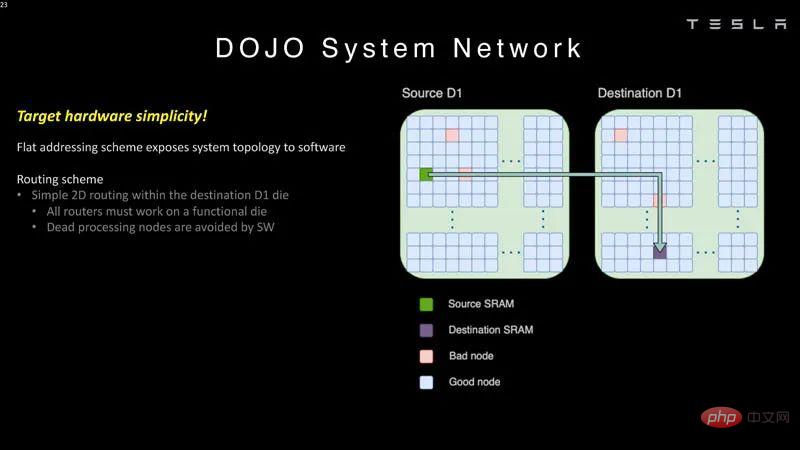

Dojo utilise un schéma d'adressage plat pour la communication.

Réseau système 1

Ces puces peuvent contourner les nœuds de traitement défectueux dans le logiciel.

Réseau système 2

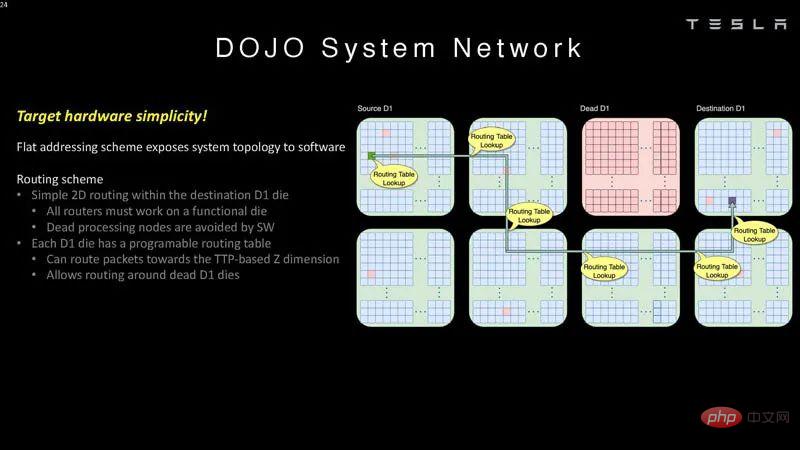

Cela signifie que le logiciel doit comprendre la topologie du système.

System Network 3

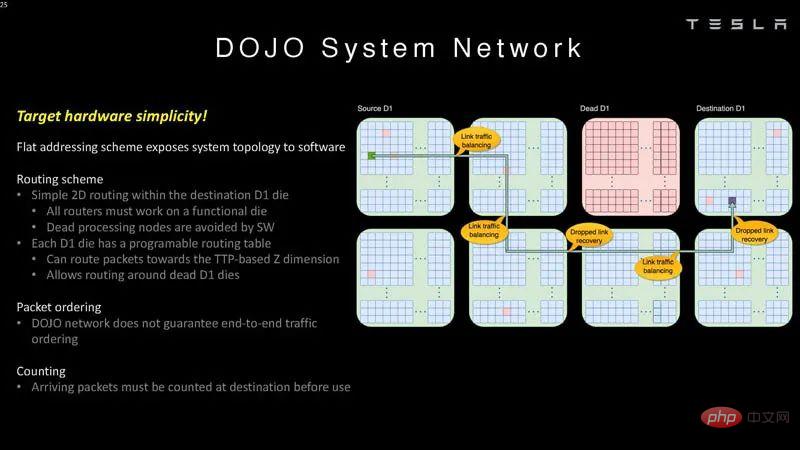

Dojo ne garantit pas l'ordre du trafic de bout en bout, les paquets doivent donc être comptés à destination.

Réseau système 4

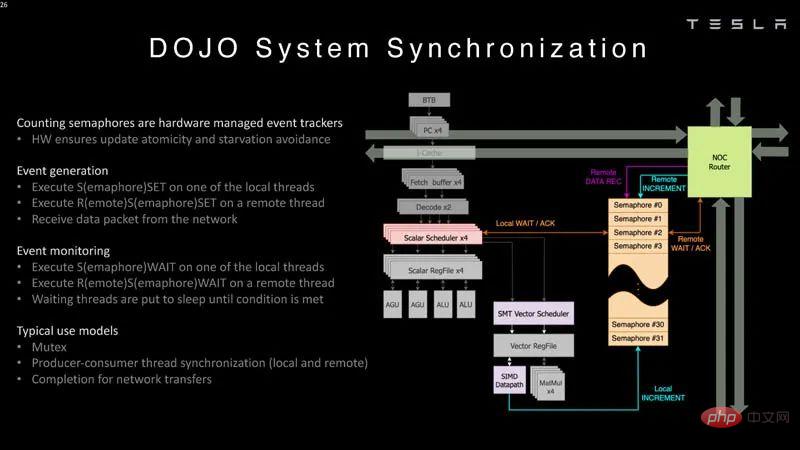

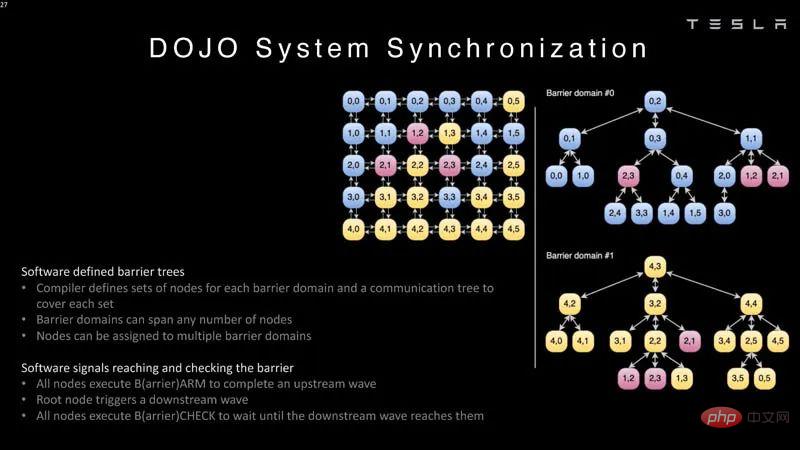

Voici comment les paquets comptent dans le cadre de la synchronisation du système.

Synchronisation du système

Le compilateur doit définir un arbre avec des nœuds

.

System Sync 2

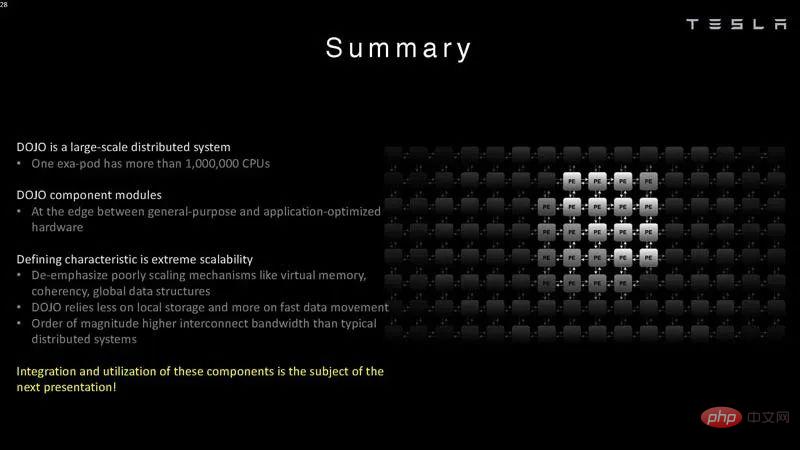

Tesla dit qu'un exa-pod possède plus d'un million de processeurs (ou nœuds de calcul). Ce sont de grands systèmes.

Résumé

Tesla a construit le Dojo spécifiquement pour fonctionner à grande échelle. En règle générale, les startups cherchent à créer une ou plusieurs puces IA par système. De toute évidence, Tesla se concentre sur une plus grande échelle.

À bien des égards, il est logique que Tesla dispose d’un immense terrain d’entraînement en IA. Ce qui est encore plus excitant, c'est qu'il utilise non seulement des systèmes disponibles dans le commerce, mais qu'il construit également ses propres puces et systèmes. Certains ISA du côté scalaire sont empruntés à RISC-V, mais le côté vectoriel et de nombreuses architectures personnalisées par Tesla, cela nécessite donc beaucoup de travail.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Tendances technologiques à surveiller en 2023

- Comment l'intelligence artificielle apporte un nouveau travail quotidien aux équipes des centres de données

- L'intelligence artificielle ou l'automatisation peuvent-elles résoudre le problème de la faible efficacité énergétique des bâtiments ?

- Co-fondateur d'OpenAI interviewé par Huang Renxun : les capacités de raisonnement de GPT-4 n'ont pas encore atteint les attentes

- Bing de Microsoft surpasse Google en termes de trafic de recherche grâce à la technologie OpenAI