Maison >Périphériques technologiques >IA >Inspiration de l'architecture de puce développée par Tesla

Inspiration de l'architecture de puce développée par Tesla

- PHPzavant

- 2023-04-08 22:51:021086parcourir

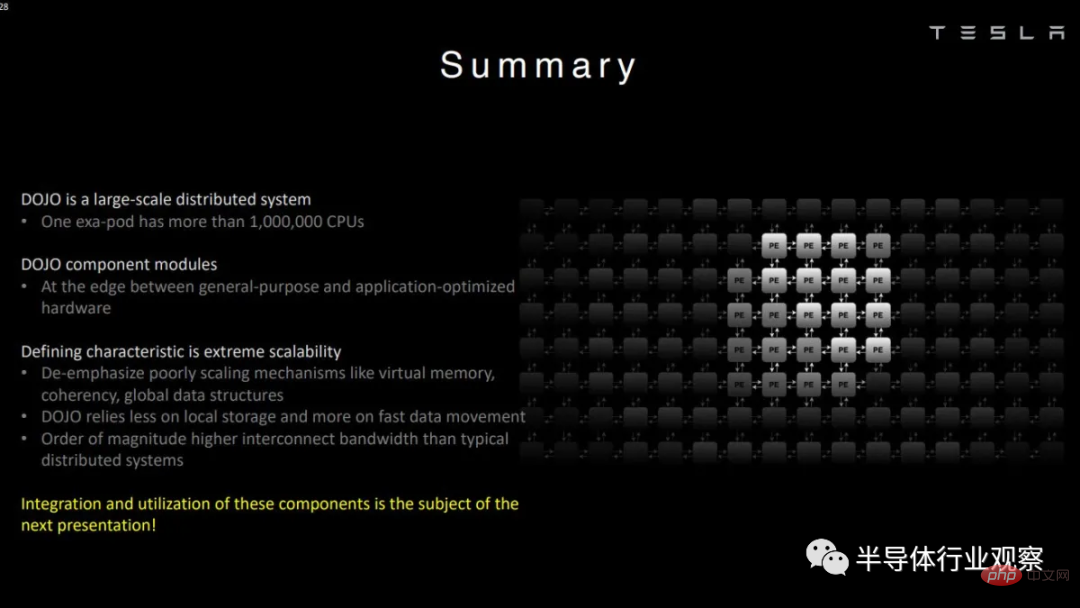

Dire que Tesla ne s’intéresse qu’au machine learning serait un euphémisme. En fait, le constructeur de voitures électriques a construit un superordinateur interne appelé Dojo, optimisé pour la formation de ses modèles d'apprentissage automatique.

Contrairement à de nombreux autres supercalculateurs, Dojo n'utilise pas de processeurs et de GPU disponibles dans le commerce, comme ceux d'AMD, d'Intel ou de Nvidia. Tesla a conçu sa microarchitecture en fonction de ses besoins, ce qui lui a permis de faire des compromis que des architectures plus générales ne pourraient pas faire.

Dans cet article, nous examinerons l'architecture basée sur la démo de Tesla chez Hot Chips. L'architecture n'a pas de nom distinct, donc par souci de simplicité, chaque fois que nous faisons référence à Dojo dans ce qui suit, nous parlons de l'architecture.

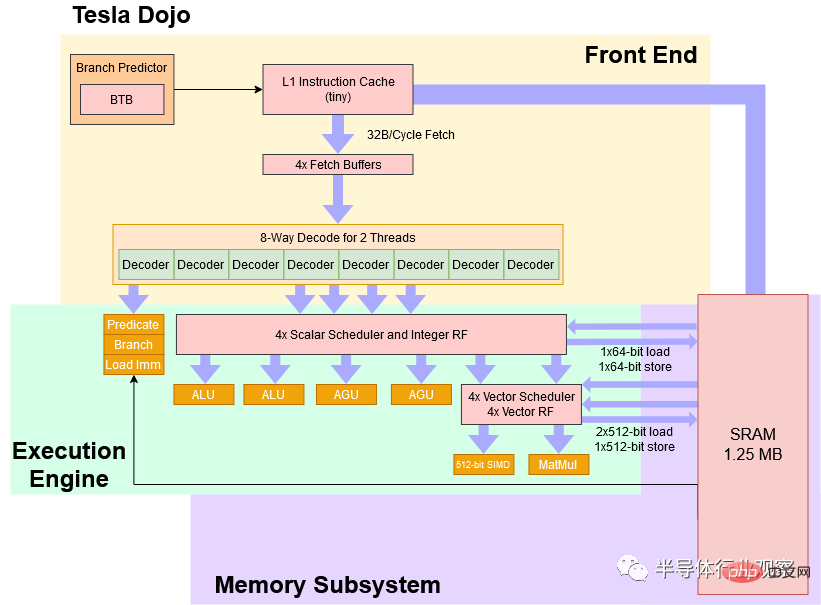

Schéma fonctionnel

À un niveau élevé, Dojo est un cœur à 8 largeurs avec un SMT à quatre voies fonctionnant à une fréquence conservatrice de 2 GHz, avec un pipeline de type CPU qui le rend plus tolérant aux différents algorithmes qu'un GPU et code de branche. Le jeu d'instructions de Dojo est similaire à RISC-V en termes scalaires, mais les ingénieurs de Tesla ont ajouté un ensemble personnalisé d'instructions vectorielles axées sur l'accélération de l'apprentissage automatique.

Schéma fonctionnel simplifié du noyau Tesla Dojo

Tesla décrit Dojo comme un "processeur à haut débit et à usage général". Du point de vue des performances, il y a certainement une part de vérité là-dedans. Mais pour augmenter la densité de calcul, Tesla a fait un sacrifice, et le cœur Dojo est très difficile à utiliser par rapport aux processeurs que nous connaissons sur les ordinateurs de bureau, les ordinateurs portables et les smartphones. D'une certaine manière, le noyau Dojo gère les choses plus comme le SPE dans Cell d'IBM que comme un noyau CPU à usage général traditionnel.

Vous aimez le SPE de Cell ?

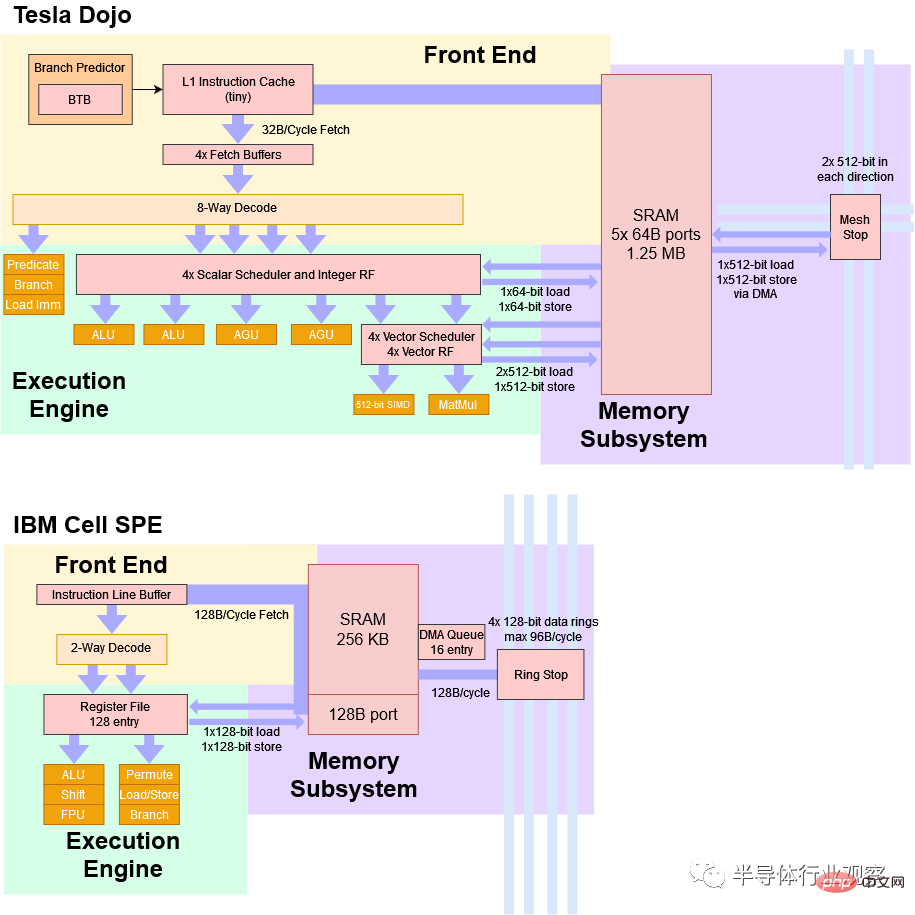

Introduit au milieu des années 2000, le processeur IBM Cell comprend huit « éléments de traitement synergiques » ou SPE, constitués d'un cœur de processeur entièrement fonctionnel (« Power Processing Element » ou PPE : Power Processing Elemen). À première vue, Dojo présente de nombreuses similitudes avec SPE.

Dojo et SPE sont tous deux optimisés pour le traitement vectoriel et s'appuient sur des processeurs hôtes distincts pour la répartition du travail. Le code exécuté sur Dojo ou SPE ne peut pas accéder directement à la mémoire système. Au lieu de cela, les applications devraient fonctionner principalement dans une petite partie de la SRAM locale. Cette SRAM locale est gérée par logiciel et ne peut pas être utilisée comme cache. Si des données de la mémoire principale sont requises, elles doivent être importées à l'aide d'une opération DMA.

Enfin, Dojo et le SPE de Cell ne prennent pas en charge la mémoire virtuelle. Nous reviendrons plus tard sur ce que cela signifie, mais en bref, cela rend le multitâche très difficile.

Une comparaison très simplifiée entre Tesla Dojo et IBM Cell SPE

Dojo diffère de plusieurs manières importantes. Étant donné que Dojo n'a pas été conçu pour des déploiements à petite échelle, le processeur hôte réside sur un système hôte distinct. Ces systèmes hôtes disposent de cartes PCIe avec des processeurs d'interface, qui sont ensuite connectés aux puces Dojo via des liaisons réseau à haut débit. En revanche, le processeur principal de Cell réside sur la même puce. Cela permet de déployer des puces Cell individuelles individuellement, ce qui n'est pas possible dans Dojo.

Le bloc local de SRAM de 1,25 Mo du Dojo est beaucoup plus grand et a une bande passante plus élevée que le Cell SPE qui ne dispose que de 256 Ko de SRAM. La SRAM de 256 Ko de Cell ne possède qu'un seul port, capable de fournir 128 Go par cycle. La SRAM de Dojo dispose de cinq ports 64B. Bien entendu, les objectifs architecturaux sont très différents. Dojo est doté d'une horloge large et d'une horloge faible, tandis que Cell SPE possède des pipelines étroits et profonds conçus pour une horloge élevée.

Front-end : confort du processeur, etc.

Présentons brièvement les pipelines Dojo en commençant par le front-end. Il existe une sorte de prédicteur de branche, comme le montre le diagramme de Tesla BTB (branch target buffer : branch target buffer). Ses capacités prédictives pourraient ne pas atteindre le niveau que nous voyons sur les cœurs hautes performances d'AMD, ARM et Intel, car Dojo doit donner la priorité aux dépenses en matière d'exécution vectorielle. Mais même un prédicteur de branchement de base constitue une grande amélioration par rapport à l'absence de prédicteur, et les capacités de prédiction de branchement de Dojo devraient offrir de meilleures performances que le GPU lorsqu'il s'agit de code ramifié ou d'empreintes d'instructions plus importantes.

Une fois que le prédicteur de branche génère le prochain pointeur de récupération d'instruction, Dojo peut récupérer 32 octets par cycle du "petit" cache d'instructions dans des tampons de récupération par thread. Ce cache d'instructions peut aider à réduire la pression de la bande passante des instructions sur la SRAM locale, garantissant que le côté données peut accéder à la SRAM avec le moins de conflits possible. De plus, le cache d’instructions n’est pas cohérent. Si un nouveau code est chargé dans la SRAM locale, le cache d'instructions doit être vidé avant de passer au nouveau code.

Présentation Hot Chips de Tesla

À partir du tampon de récupération, le décodeur de Dojo peut gérer huit instructions par cycle à partir de deux threads. Je suis un peu confus quant à ce que signifie "deux threads par cycle", car les processeurs avec SMT gèrent généralement un thread par cycle et changent de thread selon les limites du cycle. Peut-être que Dojo divise le décodeur en deux clusters et sélectionne deux threads pour leur fournir des données dans chaque boucle. Cela peut réduire la pénalité de débit de décodage pour la branche prise.

Pendant le décodage, certaines instructions (telles que les branchements, les opérations prédites et les chargements immédiats ("analyse de liste")) peuvent être exécutées dans le front-end et supprimées du pipeline. C'est un peu comme les processeurs x86 plus récents qui éliminent les copies de registre à registre dans le renamer. Mais vous avez bien entendu : Dojo ne suit pas les instructions « d'élimination » tout au long du pipeline pour maintenir la retraite dans l'ordre. D'autres processeurs suivent tout jusqu'à la sortie afin de pouvoir s'arrêter à n'importe quelle limite d'instruction et maintenir tout l'état nécessaire pour reprendre l'exécution. Cette capacité est appelée « exceptions précises » et les systèmes d'exploitation modernes l'utilisent pour fournir toutes sortes de fonctionnalités, comme la pagination sur le disque, ou vous indiquer exactement où votre code est erroné.

Tesla ne se soucie pas des exceptions précises. Dojo dispose d'un mode de débogage dans lequel davantage d'instructions sont transmises via le pipeline pour fournir des exceptions "plus précises", mais il n'y a pas de logique de sortie ordonnée comme un processeur normal dans le désordre.

Moteur d'exécution du Dojo

Après avoir vu un front-end large, il peut être un peu étrange de voir un moteur d'exécution d'entiers de largeur 4 avec seulement deux ALU et deux AGU. Mais ce pipeline en forme d’entonnoir est logique car certaines instructions sont exécutées et ignorées dès le début.

Dojo ne réussira pas non plus dans les systèmes clients où les performances des entiers scalaires sont importantes. Par conséquent, le côté entier fournit un débit suffisant pour gérer le flux de contrôle et la génération d’adresses afin de maintenir les cellules vectorielles et matricielles alimentées.

Les extrémités d'exécution vectorielles et matricielles de Dojo sont placées après le moteur d'exécution scalaire dans le pipeline principal, et il existe deux pipelines d'exécution. Deux pipelines peuvent sembler peu, mais Dojo dispose d'unités d'exécution très larges derrière ces pipelines. Un pipeline peut effectuer une exécution vectorielle de 512 bits, tandis que l'autre pipeline effectue une multiplication matricielle 8x8x4. Par conséquent, tant que les instructions exposent suffisamment de parallélisme explicite, Dojo peut atteindre un débit très élevé, en particulier lors de l'utilisation d'unités matricielles. Tesla affirme qu'une puce dotée de 354 cœurs Dojo peut atteindre 362 TFLOPS BF16 à 2 GHz, ce qui suggère que chaque cœur peut exécuter 512 FLOPS BF16 par cycle.

Nous ne savons pas si Dojo peut s'exécuter complètement dans le désordre. Mais Tesla a déclaré que le côté entier peut fonctionner bien avant le côté vectoriel, suggérant qu'il pourrait exécuter des instructions qui s'arrêtaient jusqu'à ce que l'un des planificateurs soit rempli. L’absence de retrait ordonné indique également des capacités d’exécution dans le désordre.

Généralement, la mise en œuvre d'une exécution dans le désordre s'accompagne d'une grande complexité. En effet, le CPU doit exécuter les instructions dans l'ordre. Les processeurs hautes performances d'AMD, ARM et Intel utilisent de grands tampons de réorganisation (et d'autres structures) pour suivre les instructions afin que leurs résultats puissent être validés dans l'ordre du programme. Cela signifie que si un programme fait quelque chose de stupide, comme diviser par zéro, ces cœurs peuvent montrer exactement quelle instruction a mal tourné. De plus, ils peuvent afficher un état du processeur qui reflète les actions de toutes les instructions avant la panne, mais pas après. Cela signifie que vous pouvez corriger ce qui a causé le dysfonctionnement de l'instruction et reprendre l'exécution. Dojo abandonne cette capacité. En échange, Dojo évite les frais généraux d'énergie et de surface associés au suivi de chaque instruction dans son pipeline pour garantir que les résultats sont fournis dans l'ordre du programme.

Accès SRAM

Normalement, on parlerait ici de mise en cache. Mais Dojo n'a pas d'accès direct à la mémoire système, nous allons donc discuter du bloc de 1,25 Mo de SRAM. Il peut gérer deux charges de 512 bits par cycle, ce qui lui confère une bande passante par cycle qui correspond aux processeurs Intel compatibles AVX-512. Tesla indique que la SRAM dispose de cinq ports de 512 bits (2 ports de chargement, 1 port de magasin et deux ports d'arrêt vers le réseau). Mais il n'y a que deux AGU du côté scalaire, ce qui signifie probablement que le cœur ne peut pas gérer deux charges de 512 bits et un magasin de 512 bits par cycle.

Étant donné que le bloc SRAM local de Dojo n'est pas mis en cache, il ne nécessite pas la balise et les bits d'état stockés avec les données. SRAM n'a pas non plus de cache L1D devant elle, elle doit donc être suffisamment rapide pour gérer toutes les instructions de chargement et de stockage sans provoquer de goulot d'étranglement, même si sa taille est plus proche du cache L2. Ne pas implémenter SRAM comme cache peut être un moyen pour Tesla de maintenir une latence faible. Si nous regardons l'architecture Hammer d'AMD d'il y a longtemps, nous pouvons voir que l'accès à 1 Mo de L2 après avoir détecté un échec L1D prenait 8 cycles (pour une latence totale de 12 cycles). Si 1 Mo de SRAM était adressé directement plutôt que utilisé comme cache, trois étapes pourraient être supprimées, réduisant ainsi la latence à 5 cycles :

Diapositive d'une précédente présentation Hot Chips montrant L2 Les étapes du pipeline impliquées dans l'accès au cache. Si L2 n'est pas un cache, les étapes qui peuvent être ignorées sont marquées en rouge.

Étant donné des décennies d'améliorations des nœuds de processus et des objectifs de vitesse d'horloge encore plus faibles qu'Athlon, il est facile de voir comment Tesla pourrait accéder à des blocs SRAM de taille L2 avec une latence de type L1. Ignorer le cache L1 permet certainement d'économiser de l'espace et de l'énergie.

Pour réduire davantage la latence, la surface et la complexité du cœur, Dojo ne prend pas en charge la mémoire virtuelle. Par conséquent, il ne dispose pas de mécanismes TLB ou de parcours de page. Les systèmes d'exploitation modernes utilisent la mémoire virtuelle pour donner à chaque processus sa propre vision de la mémoire. L'adresse mémoire utilisée par le programme n'est pas un accès direct à l'adresse mémoire physique, mais est convertie en adresse physique par le processeur à l'aide de la structure de pagination définie par le système d'exploitation. C'est ainsi que les systèmes d'exploitation modernes isolent les programmes les uns des autres et empêchent une application qui se comporte mal de faire tomber l'ensemble du système.

La mémoire virtuelle vous permet également d'exécuter plus de programmes que la mémoire physique. Lorsque vous manquez de mémoire réelle, le système d'exploitation démappe la page, l'écrit sur le disque et donne à votre programme la mémoire dont il a besoin. Lorsqu'un autre programme merdique tente d'accéder à cette mémoire, le processeur essaie de traduire l'adresse virtuelle en adresse physique, mais constate que la traduction n'existe pas. Le processeur génère une exception de défaut de page, que le système d'exploitation gère en relisant la page expulsée dans la mémoire physique et en remplissant l'entrée de la table des pages.

Rien de tout cela n'est possible sur Dojo. La fonctionnalité SMT à 4 voies du noyau vise davantage à exposer une seule application à un parallélisme explicite qu'à améliorer les performances multitâches. Par exemple, un thread peut effectuer des calculs vectoriels tandis qu'un autre thread charge de manière asynchrone les données de la mémoire système vers la SRAM (via DMA).

Pour simplifier davantage la conception, Dojo peut adresser la SRAM avec seulement 21 bits d'adresse, ce qui peut simplifier l'AGU et le bus d'adressage de Dojo. Ces compromis pourraient permettre à Tesla d’accéder à cette SRAM avec une latence suffisamment faible pour éviter de mettre en place un cache de données L1 distinct devant celle-ci.

Accès mémoire

En parlant de mémoire système, la puce Dojo n'est pas directement connectée à la mémoire. Au lieu de cela, ils se connectent à un processeur d'interface équipé d'un HBM. Ces processeurs d'interface sont également chargés de communiquer avec le système hôte.

La tuile Dojo avec 25 puces indépendantes peut accéder à 160 Go de mémoire HBM Tesla affirme qu'elle peut transférer 900 Go/s depuis chaque bord de puce à travers les limites de la tuile, ce qui signifie qu'elle peut transférer une bande passante de liaison de 4,5 To/s. processeur d'interface d'accès et son HBM. L’accès au HBM passant par une puce distincte, la latence d’accès peut être très élevée.

est petit, comment faire ?

Dojo est un noyau de taille 8 avec au moins quelques capacités d'exécution OoO, un débit vectoriel décent et une unité de multiplication matricielle. Mais même avec 1,25 Mo de SRAM locale, cela reste un très petit cœur. En comparaison, l'A64FX de Fujitsu occupe plus de deux fois la surface sur le même nœud de processus. La conception d’un processeur consiste à faire les bons compromis. Tesla souhaite maximiser le débit de l'apprentissage automatique en regroupant un grand nombre de cœurs sur une puce, de sorte que les cœurs individuels doivent être petits. Pour atteindre son efficacité de zone, Dojo utilise des techniques familières. Il fonctionne à une fréquence conservatrice de 2 GHz. Les circuits d'horloge inférieurs ont tendance à occuper moins de place. Il peut avoir un prédicteur de branche de base et un petit cache d'instructions. Si le programme a une empreinte de code importante ou comporte de nombreuses branches, cela sacrifiera certaines performances.

Mais Tesla réduit également davantage la consommation d'énergie et de surface en supprimant les fonctionnalités non nécessaires à l'exécution des charges de travail internes. Ils n'effectuent pas de mise en cache côté données, ne prennent pas en charge la mémoire virtuelle et ne prennent pas en charge les exceptions précises.

Le résultat est un cœur de processeur qui offre la flexibilité des performances des cœurs de processeur modernes tout en étant à bien des égards moins convivial pour l'utilisateur et le programmeur que l'Intel 8086. En plus du cœur, Tesla économise également de la place sur les puces à grande échelle en concevant des puces Dojo spécifiquement pour le déploiement.

Implémentation Physique

En rétrécissant, le noyau Dojo est implémenté sur une très grande matrice de 645 mm2 appelée D1. Contrairement aux autres puces que nous connaissons, une seule puce Dojo n’est pas autosuffisante. Il n'a pas de contrôleur DDR ou PCIe. Il existe des interfaces IO sur les bords de la puce qui permettent à la puce de communiquer avec les puces adjacentes avec une latence d'environ 100 ns.

Pour accéder à la mémoire système, la puce Dojo D1 doit communiquer avec un processeur d'interface doté d'un HBM intégré. Le processeur d'interface est à son tour connecté au système hôte via PCIe (le processeur d'interface est installé sur une carte PCIe). En théorie, un déploiement fonctionnel minimal de Dojo impliquerait une puce Dojo, une carte processeur d'interface et un système hôte. Mais Tesla déploie les matrices Dojo dans des modules contenant 25 matrices chacun pour donner une idée d'échelle. La matrice Dojo D1 est spécialement conçue pour être un élément de base pour les superordinateurs et rien de plus.

Cette spécialisation peut économiser plus de zone de matrice. Dojo D1 ne gaspille pas d'espace sur les contrôleurs DDR et PCIe. La majeure partie de la puce est occupée par l'énorme noyau Dojo, à l'exception des connecteurs IO personnalisés à l'extérieur conçus pour s'interfacer avec la puce adjacente.

En revanche, les puces conçues avec une plus grande flexibilité de déploiement à l'esprit consacrent beaucoup d'espace aux E/S. Les puces Zen 1 « Zeppelin » d’AMD le démontrent très bien. Zeppelin peut se connecter directement à la mémoire DDR4, aux périphériques PCIe, aux disques SATA et aux périphériques USB – parfait pour les besoins des clients. Dans un serveur, l'interface IFOP lui permet de communiquer avec les puces adjacentes. De gros morceaux de SRAM situés à proximité de l'IFOP peuvent être des filtres de surveillance, aidant à maintenir efficacement la cohérence du cache dans des paramètres à nombre de cœurs élevé. Dojo ne tente pas de maintenir la cohérence du cache entre les cœurs et n'utilise aucune SRAM pour le filtrage de surveillance.

De la démonstration des chipsets d'AMD à l'ISSCC 2021

AMD y est parvenu en consacrant environ 44 % de la zone de puce « Zeppelin » à une logique autre que les cœurs et le cache pour payer cela flexibilité. Dojo n'utilise que 28,9 % de la surface de la puce pour des éléments autres que la SRAM et les cœurs.

Derniers mots

La microarchitecture derrière le supercalculateur Tesla Dojo montre comment atteindre une densité de calcul très élevée tout en conservant la capacité du processeur à gérer le code de branchement. Pour y arriver, vous devez renoncer à la plupart des conforts qui définissent notre expérience informatique moderne. Si vous pouvez hypothétiquement construire votre bureau autour du noyau Dojo, l'expérience semblera probablement familière à tous ceux qui ont utilisé MS-DOS. Vous ne pouvez pas exécuter plusieurs applications en même temps. Une seule application qui se comporte mal peut vous obliger à redémarrer votre système. Si vous ne disposez pas de suffisamment de RAM pour exécuter un programme, vous pouvez oublier de l'exécuter complètement (sans paginer sur le disque).

Mais ces compromis sont parfaitement logiques dans le supercalculateur de Tesla. Tesla n'a pas besoin d'un cœur Dojo pour gérer plusieurs applications en cours d'exécution simultanément, Dojo n'a besoin que d'exécuter du code fiable à l'intérieur. Ainsi, Tesla ne se soucie pas de la prise en charge de la mémoire virtuelle. De même, les programmes d'apprentissage automatique exécutés sur Dojo seront écrits en tenant compte de ce système spécifique. Vous n'aurez pas un lot de programmes arbitraires pouvant nécessiter plus de mémoire que celle disponible. Cela signifie que vous n'avez pas besoin d'exceptions précises (ni de mémoire virtuelle) pour autoriser des techniques telles que la surutilisation de la mémoire, la compression de la mémoire ou l'échange de pages de mémoire entre les disques. Des exceptions précises sont également utiles pour le débogage, mais Tesla le fait de manière moins coûteuse via un mode de débogage distinct.

Il y a fort à parier que les compromis utilisés par Tesla pour atteindre une densité de calcul élevée ne sont pas possibles dans les processeurs grand public ou serveur. Mais ils sont très amusants en action, et nous devons remercier Tesla d'avoir pris le temps de les montrer chez Hot Chips. Au cours des deux dernières décennies, les améliorations apportées aux nœuds de processus ont ralenti, ce qui a entraîné une progression encore plus lente des performances monothread. Les contraintes d'alimentation et de refroidissement ont réduit les performances multithread au cours des cinq dernières années. Mais le besoin en puissance de calcul ne ralentit pas, c'est pourquoi les entreprises se tournent vers du matériel plus spécialisé pour suivre le rythme.

L'architecture du supercalculateur Dojo de Tesla est un bon exemple de la manière dont des compromis sont faits pour augmenter la densité de calcul et de la manière dont les tendances actuelles favorisent l'introduction de matériel spécialisé pour les applications à débit limité.

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!

Articles Liés

Voir plus- Tendances technologiques à surveiller en 2023

- Comment l'intelligence artificielle apporte un nouveau travail quotidien aux équipes des centres de données

- L'intelligence artificielle ou l'automatisation peuvent-elles résoudre le problème de la faible efficacité énergétique des bâtiments ?

- Co-fondateur d'OpenAI interviewé par Huang Renxun : les capacités de raisonnement de GPT-4 n'ont pas encore atteint les attentes

- Bing de Microsoft surpasse Google en termes de trafic de recherche grâce à la technologie OpenAI