Maison >Opération et maintenance >exploitation et maintenance Linux >Vous amène à maîtriser l'outil de construction automatisé du projet Linux Makefile make

Vous amène à maîtriser l'outil de construction automatisé du projet Linux Makefile make

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBavant

- 2022-01-24 17:11:362032parcourir

Cet article vous présente l'outil de construction automatique de projet sous Linux. Dans la vraie vie, nous ne pouvons souvent pas nous fier uniquement au code d'un fichier pour faire fonctionner une certaine fonction. Il nécessite actuellement la combinaison et l'implémentation de plusieurs sections différentes. à intégrer dans un projet et tous les modules emballés et combinés pour atteindre la fonction finale. J'espère que cela aide tout le monde.

Makefile

Makefile est un fichier texte qui enregistre le processus de règle de construction d'un projet. Le fait que vous puissiez ou non écrire des makefiles au travail montre d'un côté si une personne a la capacité de réaliser des projets à grande échelle. Dans le même temps, les fichiers sources d'un projet ne sont pas comptés. Ils sont placés dans plusieurs répertoires selon leur type. , fonction et module.Makefile Une série de règles sont définies pour spécifier quels fichiers doivent être compilés en premier, quels fichiers doivent être compilés plus tard, quels fichiers doivent être recompilés, et des opérations fonctionnelles encore plus complexes peuvent être effectuées. cela apporte - "compilation automatisée". Une fois écrit, une seule commande make est nécessaire et l'ensemble du projet est entièrement compilé et traduit, ce qui améliore considérablement l'efficacité du développement logiciel.

Principe de fonctionnement

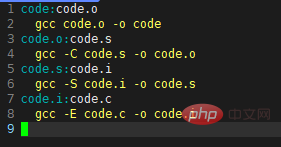

Dans le Makefile, des dépendances entre différents fichiers seront formées. Par exemple, un code.exe est généré via un lien basé sur code.o, et code.o est généré sur la base de code.s. formé par assemblage, code.s est généré par compilation basée sur code.i, code.i est généré une fois le prétraitement terminé sur la base de code.c et la source est trouvée couche par couche. Ses règles utilisent une méthode de flashback, traitant le premier fichier comme le dernier fichier terminé. Si le fichier actuel n'est pas généré, il avancera couche par couche via les dépendances et les méthodes de génération mutuelle, et terminera enfin la formation de tous les fichiers.

DépendancesA:B A dépend de B

Méthode de dépendanceoption gcc + B -o +A A est le fichier généré par B après le traitement

Nettoyage du projet Les projets doivent être nettoyés. Comme clean, s'il n'est pas directement ou indirectement associé au premier fichier cible, alors les commandes définies après celui-ci ne seront pas automatiquement exécutées. Cependant, nous pouvons montrer que make est exécuté. Autrement dit, la commande "make clean" est utilisée pour effacer tous les fichiers cibles à recompiler. Mais généralement pour nos fichiers cibles propres, nous le définissons comme pseudo cible et le modifions avec .PHONY. La caractéristique de la pseudo cible est qu'elle est toujours exécutée par

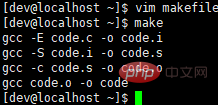

.Principemake cherchera un fichier nommé "Makefile" ou "makefile" dans le répertoire courant.

S'il est trouvé, il trouvera le premier fichier dans le contenu du fichier et utilisera ce fichier comme fichier cible final.

Si le fichier n'existe pas actuellement, ou si l'heure de modification des fichiers dépendants du fichier est plus récente que le fichier actuel, alors il exécutera la commande définie ultérieurement pour générer le fichier actuel.

Si le fichier dépendant du fichier n'existe pas, alors passez aux étapes 2 et 3 pour ce fichier dépendant jusqu'à ce que le fichier source final soit trouvé

Bien sûr, votre fichier C et votre fichier H existent donc make générera le . o, puis utilisez le fichier .o pour déclarer la tâche ultime de make, qui consiste à exécuter le fichier.

Il s'agit de la dépendance de l'ensemble du make. Make recherchera les dépendances de fichiers couche par couche jusqu'à ce que le premier fichier cible soit finalement compilé.

Pendant le processus de recherche, si une erreur se produit, par exemple si le dernier fichier dépendant est introuvable, make se fermera directement et signalera une erreur. Cependant, en cas d'erreurs dans les commandes définies ou d'échec de la compilation, make ne raisonnera pas.

make ne se soucie que des dépendances de fichiers, c'est-à-dire que si après avoir trouvé les dépendances, le fichier après les deux points n'est toujours pas là, alors je suis désolé, je ne travaillerai pas.

make ne trouvera à chaque fois que le premier objet cible dans le Makefile pour la génération, et il se fermera après la génération (le deuxième objet ne sera pas généré)

.PHONY : clean

clear:

rm -rf $( obj)

【Supplément】

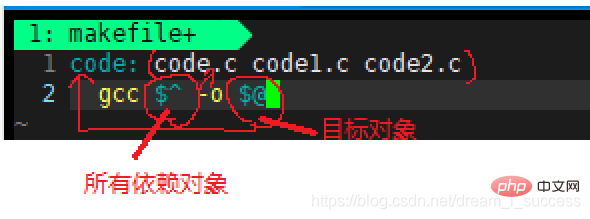

1. L'utilisation de variables prédéfinies : [$@ ], [ $^], [ $

$@ : signifie Objet cible

$^ : Représente tous les objets dépendants

&

2 $ (caractère générique ./.c) Obtient les noms de fichiers de tous les fichiers se terminant par .c dans le répertoire actuel [Exemple] src=$(wildcard ./.c) code : $ (str)

3. $ (patsubst %.c, %.o,$(str)) signifie remplacer le fichier .c dans la variable str par .o, puis stocké dans la variable obj.

4. Pseudo objet : Déclarez qu'un objet cible n'a rien à voir avec des fichiers externes, ce qui signifie que l'objet doit être régénéré à chaque fois, qu'il soit le plus récent ou non, et que l'extérieur puisse exister, l'instruction doit être exécuté à chaque fois [.PHONY: ]

5. Le processus de compilation du programme : comprend généralement le prétraitement, la compilation, l'assemblage et la liaison, mais dans la construction réelle du projet, il est divisé en deux étapes, à savoir la compilation et la liaison. L'avantage est que si vous ne modifiez qu'un seul fichier .c, par rapport au processus précédent de compilation directe de tous les fichiers .c pour générer des programmes exécutables, vous devez recompiler tous les fichiers .c pour générer des programmes exécutables, ce qui est très inefficace. , donc l'opération est divisée en deux étapes. Tout d'abord, chaque .c génère son propre .o, puis relie tous les .o ensemble. Une fois que a .c change, seul ce .c doit être généré. module spécifié dans le programme.

Exemple 1. Créer un Makefile général

Exemple 2. Utiliser un Makefile prédéfini

Recommandations associées : "Tutoriel vidéo Linux"

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!