Maison >Problème commun >Que peut-on faire pour résoudre le problème de la correspondance de vitesse entre le processeur et la mémoire principale ?

Que peut-on faire pour résoudre le problème de la correspondance de vitesse entre le processeur et la mémoire principale ?

- 王林original

- 2020-12-11 15:23:4313664parcourir

Pour résoudre le problème de correspondance de vitesse entre le processeur et la mémoire principale, la mémoire cache peut être utilisée. La mémoire cache est une mémoire petite mais rapide située entre le processeur et la mémoire principale DRAM. Elle est généralement composée de mémoire statique. La mémoire statique est une mémoire de petite capacité mais à grande vitesse située entre le processeur et la mémoire.

L'environnement d'exploitation de ce tutoriel : système Windows 7, ordinateur Dell G3.

Afin de résoudre le problème de correspondance de vitesse entre le CPU et la mémoire principale, l'implémentation peut utiliser un cache entre le CPU et la mémoire principale.

Qu'est-ce que le cache

La mémoire cache, une mémoire cache à grande vitesse dans un ordinateur, est située dans le processeur et le principal mémoire DRAM (Dynamic Random Access Memory), une mémoire plus petite mais à très grande vitesse, généralement composée de SRAM (Static Random Access Memory). Il s'agit d'une mémoire de petite capacité mais à grande vitesse située entre le processeur et la mémoire.

La vitesse du CPU est bien supérieure à celle de la mémoire. Lorsque le CPU accède directement aux données de la mémoire, il doit attendre un certain temps, tandis que le cache peut enregistrer une partie des données. données que le CPU vient d'utiliser ou de recycler. Si le CPU a besoin d'accéder à nouveau aux données, lors de l'utilisation de cette partie des données, elle peut être appelée directement depuis le cache, évitant ainsi les accès répétés aux données et réduisant le temps d'attente du CPU. , améliorant ainsi l’efficacité du système.

Fonction du cache

La fonction du cache est d'augmenter le taux d'entrée et de sortie des données du processeur. La capacité du cache est petite mais rapide, la vitesse de la mémoire est faible mais la capacité est grande. En optimisant l'algorithme de planification, les performances du système seront grandement améliorées, comme si la capacité du système de stockage était équivalente à la mémoire et que la vitesse d'accès était similaire à celle-ci. la Cache.

La vitesse du CPU est bien supérieure à celle de la mémoire. Lorsque le CPU accède directement aux données de la mémoire, il doit attendre un certain temps, tandis que le cache peut enregistrer une partie des données. données que le CPU vient d'utiliser ou de recycler. Si le CPU a besoin d'accéder à nouveau aux données, lors de l'utilisation de cette partie des données, elle peut être appelée directement depuis le cache, évitant ainsi les accès répétés aux données et réduisant le temps d'attente du CPU. , améliorant ainsi l’efficacité du système. Le cache est divisé en L1Cache (cache de niveau un) et L2Cache (le cache de niveau deux est principalement intégré au CPU, tandis que L2Cache est intégré sur la carte mère ou le CPU).

Principes de base du cache

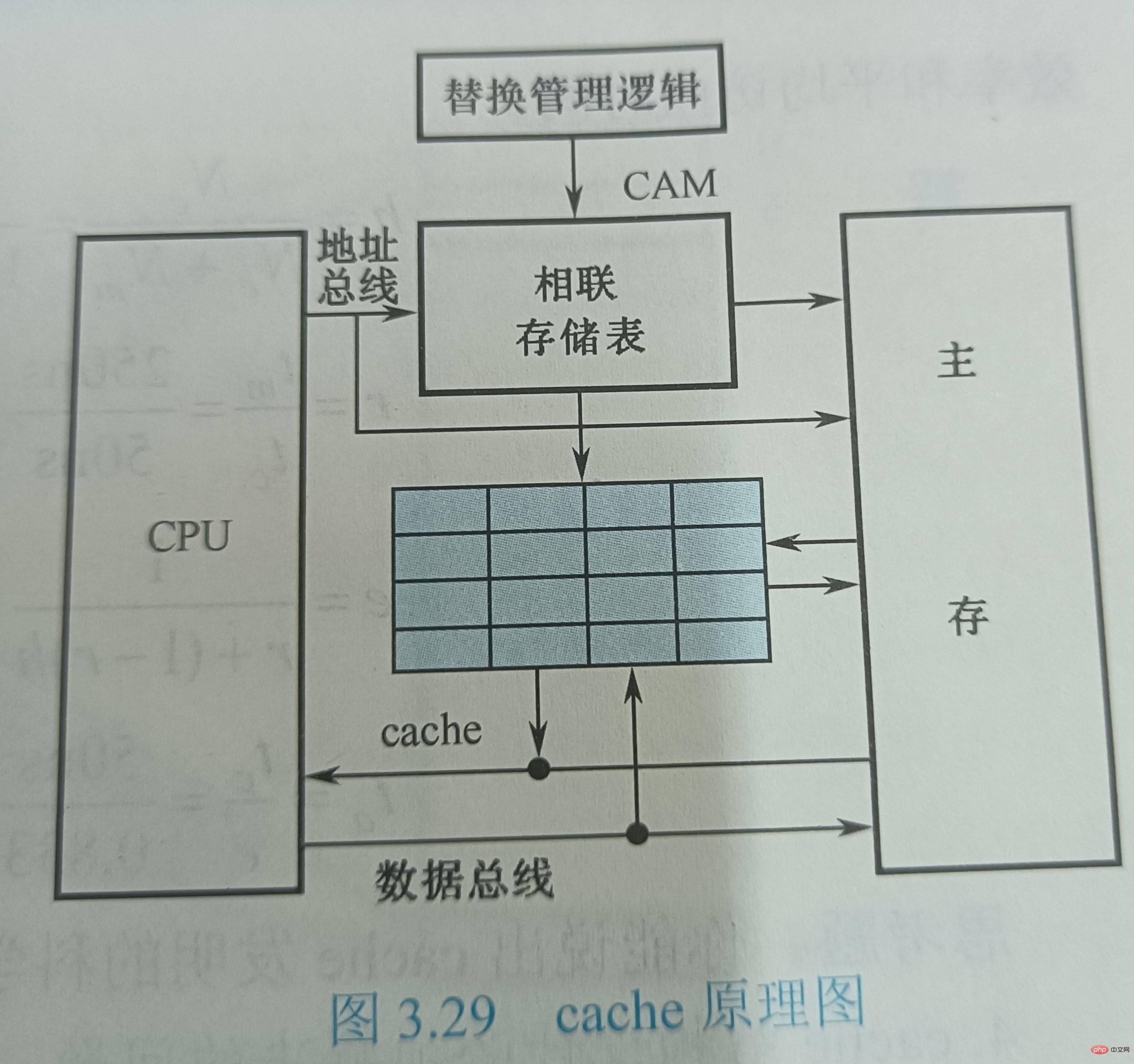

En plus de la SRAM, le cache dispose également d'une logique de contrôle. Si le cache est à l'extérieur de la puce CPU, sa logique de contrôle est généralement combinée avec la logique de contrôle de la mémoire principale, appelée contrôleur de mémoire principale/chace ; si le cache est à l'intérieur du CPU, le CPU fournit sa logique de contrôle ;

L'échange de données entre le CPU et le cache se fait en unités de mots, tandis que l'échange de données entre le cache et la mémoire principale se fait en unités de bloc. Un bloc est composé de plusieurs mots et a une longueur fixe. Lorsque le CPU lit un mot en mémoire, il envoie l'adresse mémoire du mot au cache et à la mémoire principale. A ce moment, la logique de contrôle du cache détermine si le mot est actuellement dans le cache en fonction de l'adresse : si c'est le cas, le cache arrive et le mot est immédiatement transféré au CPU, sinon, le cache est manquant (manqué), et ; le cycle de lecture de la mémoire principale est utilisé pour lire le mot dans la mémoire principale. La lecture est envoyée au CPU. En même temps, l'intégralité du bloc de données contenant ce mot est lue dans la mémoire principale et envoyée au cache.

La figure 3.29 montre le diagramme schématique du cache. Supposons que le temps de lecture du cache soit de 50 ns et que le temps de lecture de la mémoire principale soit de 250 ns. Le système de stockage est modulaire, et chaque module 8K de la mémoire principale est associé à un cache d'une capacité de 16 mots. Le cache est divisé en 4 lignes, chaque ligne comporte 4 mots (W). L'adresse attribuée au cache est stockée dans une mémoire associative CAM, qui est une mémoire adressable par le contenu. Lorsque le CPU exécute une instruction d'accès à la mémoire, il envoie l'adresse du mot auquel accéder au CAM si W n'est pas dans le cache, W est transféré de la mémoire principale vers le CPU ; Dans le même temps, une ligne de données composée de quatre mots consécutifs contenant W est envoyée au cache, remplaçant la ligne de données d'origine dans le cache. Ici, l'algorithme de remplacement est implémenté par des circuits logiques matériels qui gèrent toujours l'utilisation du cache.

Problèmes qui doivent être résolus dans la conception de la structure du cache

Il ressort du principe de fonctionnement de base du cache dont la conception du cache a besoin suivre deux principes : l'un est d'espérer que le taux de réussite du cache soit le plus élevé possible, qui devrait en fait être proche de 1 ; l'autre est d'espérer que le cache est transparent pour le CPU, c'est-à-dire s'il existe un cache ; ou non, le CPU accède à la mémoire de la même manière et le logiciel n'a pas besoin d'ajouter quoi que ce soit. Les instructions peuvent accéder au cache. Les problèmes de taux de réussite et de transparence sont résolus du point de vue de l'accès du CPU à la mémoire, la mémoire aura la capacité de la mémoire principale et une vitesse proche du cache. À cette fin, un certain circuit matériel doit être ajouté pour compléter la fonction de contrôle, c'est-à-dire le contrôleur de cache.

Lors de la conception de la structure du cache, plusieurs problèmes doivent être résolus : ① Comment stocker le contenu de la mémoire principale lorsqu'il est transféré dans le cache ? ② Comment retrouver les informations dans le cache lors de l'accès à la mémoire ? ③ Comment remplacer le cache lorsque l'espace du cache est insuffisant Quel contenu existe déjà dans le cache ? ④ Comment réécrire le contenu du cache lorsqu'une opération d'écriture est requise

Parmi elles, les deux premières questions sont liées les unes aux autres, c'est-à-dire comment localiser les informations de la mémoire principale dans le cache et comment convertir l'adresse de la mémoire principale en adresse de cache. Par rapport à la capacité de la mémoire principale, la capacité du cache est très petite. Le contenu qu'il enregistre n'est qu'un sous-ensemble du contenu de la mémoire principale, et l'échange de données entre le cache et la mémoire principale s'effectue en unités de bloc. Afin de placer le bloc de mémoire principale dans le cache, une méthode doit être utilisée pour localiser l'adresse de la mémoire principale dans le cache, appelée mappage d'adresses. La signification physique du mot « cartographie » est de déterminer la relation correspondante entre les emplacements et de la mettre en œuvre avec du matériel. De cette façon, lorsque le CPU accède à la mémoire, l'adresse mémoire d'un mot qu'il donne sera automatiquement convertie en adresse de cache, c'est-à-dire la conversion d'adresse de cache.

Le problème du remplacement du cache consiste principalement à sélectionner et à exécuter l'algorithme de remplacement pour remplacer le contenu du cache lorsque le cache manque. La dernière question concerne la stratégie d'opération d'écriture du cache, qui se concentre sur le maintien de la cohérence entre la mémoire principale et le cache lors des mises à jour.

(Partage de vidéos d'apprentissage : Vidéo de programmation)

Ce qui précède est le contenu détaillé de. pour plus d'informations, suivez d'autres articles connexes sur le site Web de PHP en chinois!