Home >Operation and Maintenance >Linux Operation and Maintenance >what is linux vcs

what is linux vcs

- 藏色散人Original

- 2023-04-10 10:55:391753browse

Linux vcs is a compiled verilog simulator, a tool used to simulate and view waveforms; it is similar to tools such as modelsim and questasim under windows, as well as quartus and vivado simulation operations.

#The operating environment of this tutorial: linux5.9.8 system, Dell G3 computer.

What is linux vcs?

The basic use of VCS tools

VCS is The tools used to simulate and view waveforms under Linux are similar to tools such as modelsim and questasim under Windows, as well as quartus and vivado simulation operations.

1.Basic instructions for vcs

Common instruction suffixes for vcs

| Command | Meaning |

|---|---|

-l readme.log |

is used to compile the information generated Place it in the log file |

v2k |

is the standard that makes VCS compatible with verilog before 2001 |

-debug_all |

Files required to generate debug |

##-f verilog_file.f | You can compile all the source code in the .f file|

-R | Run immediately after compilation, that is, execute immediately after compilation is completed./simv |

-Mupdate | When the source file is modified, only the modified **.v* will be recompiled * file, saving compilation time. |

-sverilog | Turn on support for Systemverilog and use it when compiling Systemverilog files. |

-timescale=1ns/1ns | Set simulation accuracy|

-o simv_file | The executable file generated by compilation is simv by default. You can use -o to change the executable file name. If you modify it here, you will not use simv but the corresponding o name when executing the simulation. |

Common commands for simv

| Meaning | |

|---|---|

./simv -l run.log | Save the execution log file|

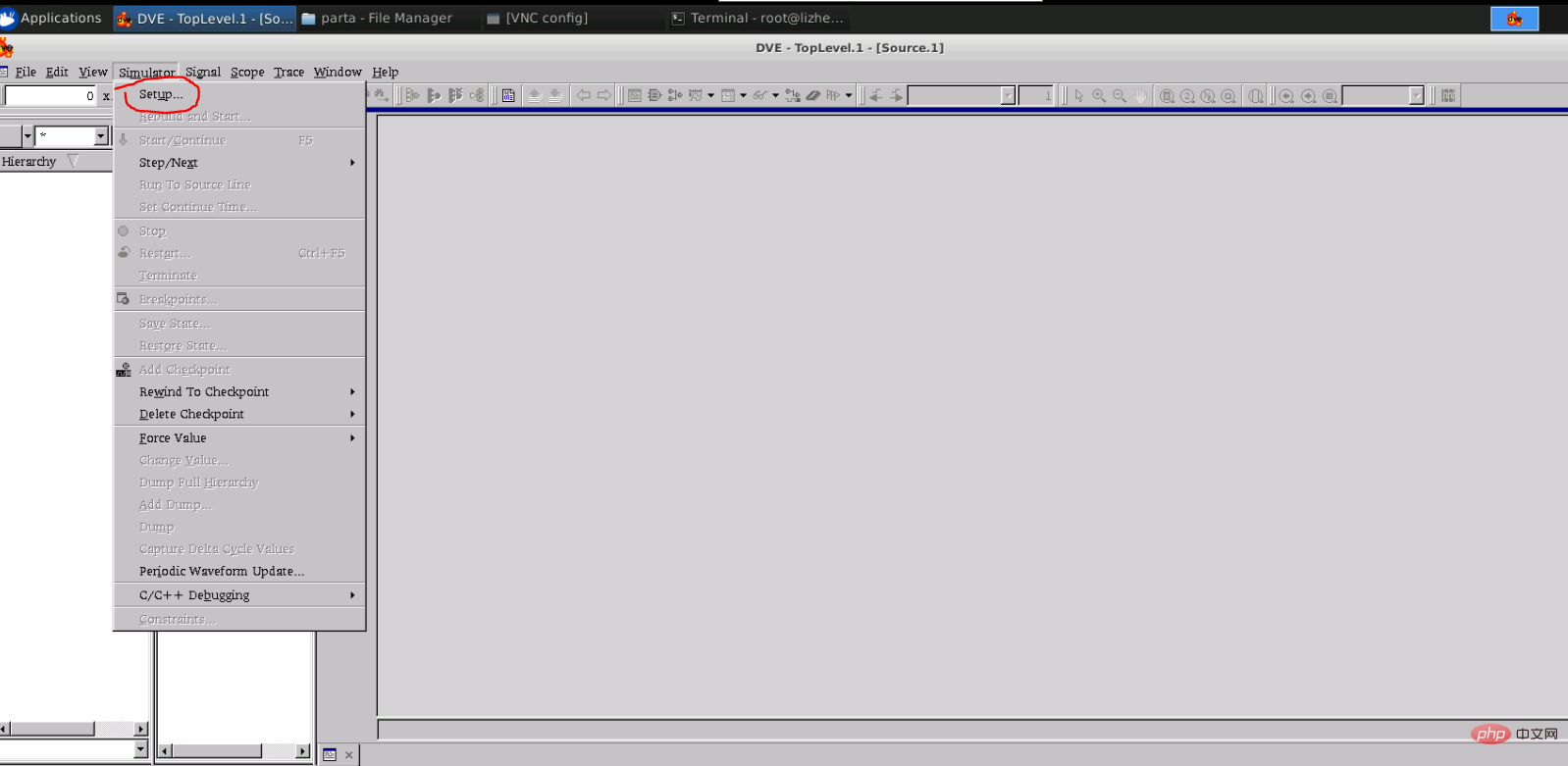

./simv -gui | Open with graphical interface

The above is the detailed content of what is linux vcs. For more information, please follow other related articles on the PHP Chinese website!