Home >Operation and Maintenance >Linux Operation and Maintenance >Take you to master the Linux project automated construction tool Makefile make

Take you to master the Linux project automated construction tool Makefile make

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBforward

- 2022-01-24 17:11:362074browse

This article brings you the automatic project construction tool in Linux. In real life, we often cannot rely solely on the code of a file to operate a certain function. It requires a combination of multiple different sections. At this time, you need to build a project and package and combine all modules to achieve the final function. I hope everyone has to help.

Makefile

Makefile is a text file that records the build rule process of a project. Whether or not you can write makefiles at work shows from one side whether a person has the ability to complete large-scale projects. At the same time, the source files in a project are not counted. They are placed in several directories according to type, function, and module. Makefile A series of rules are defined to specify which files need to be compiled first, which files need to be compiled later, which files need to be recompiled, and even more complex functional operations can be performed. The benefit it brings is - "automated compilation". Once written, only one make command is needed, and the entire project is completely automatically compiled and translated, which greatly improves the efficiency of software development.

compilation method in engineering. Make is a command and makefile is a file. They are used together to complete the automated construction of the project.

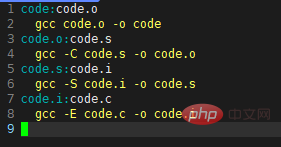

Dependency

Dependency method

gcc option B -o A A is the file generated by B after processingProject cleanup

The project needs to be Cleaning, like clean, is not directly or indirectly associated with the first target file, then the commands defined after it will not be automatically executed. However, we can show that make is executed. That is, the command - "make clean" is used to clear all target files for recompiling. But generally for our clean target files, we set it as a pseudo target and modify it with .PHONY. The characteristic of the pseudo target is that it is always executed by.

Principle

make will look for a file named "Makefile" or "makefile" in the current directory. If found, it will find the first file in the content of the file and use this file as the final target file. If the file does not currently exist, or the modification time of the file's dependent files is newer than the current file, then it will execute the command defined later to generate the current file. If the dependent file of the file does not exist, then proceed to steps 2 and 3 for this dependent file until the final source file is found Of course, your C file and H files exist, so make will generate the .o file, and then use the .o file to declare the ultimate task of make, which is to execute the file. This is the dependency of the entire make. Make will look for file dependencies layer by layer until the first target file is finally compiled. During the search process, if an error occurs, such as the last dependent file cannot be found, make will exit directly and report an error. For errors in the defined command, or the compilation will not be successful. , make ignores it at all. make only cares about the dependencies of files, that is, if after I find the dependencies, the file after the colon is still not there, then I'm sorry, I won't work. make will only find the first target object in the Makefile for generation each time, and it will exit after generation (the second object will not be generated).PHONY: cleanclear: œrm -rf $(obj)[Supplement]

5. The compilation process of the program: generally includes preprocessing, compilation, assembly, and linking, but in actual project construction, it is divided into two steps, namely compilation and linking. The advantage of this is that if you only modify one .c file, compared to the previous process of directly compiling all .c files to generate executable programs, you need to recompile all .c files to generate executable programs, which is very inefficient. , so the operation is divided into two steps. First, each .c generates its own .o, and then links all .o together. Once a .c changes, only this .c needs to be generated. oAfter that, just replace the specified module in the program.

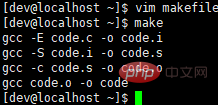

Example 1. Create a general Makefile

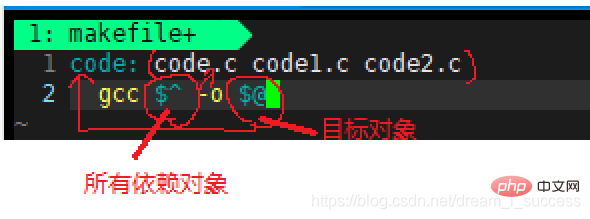

Example 2. Use predefined Makefile

Related recommendations: "Linux Video Tutorial"

The above is the detailed content of Take you to master the Linux project automated construction tool Makefile make. For more information, please follow other related articles on the PHP Chinese website!