Heim >Hardware-Tutorial >Hardware-Neuigkeiten >AMD Zen 5-Ausführungs-Engine enthüllt: Verwendung echter 512-Bit-FPU

AMD Zen 5-Ausführungs-Engine enthüllt: Verwendung echter 512-Bit-FPU

- 王林nach vorne

- 2024-04-05 16:37:13550Durchsuche

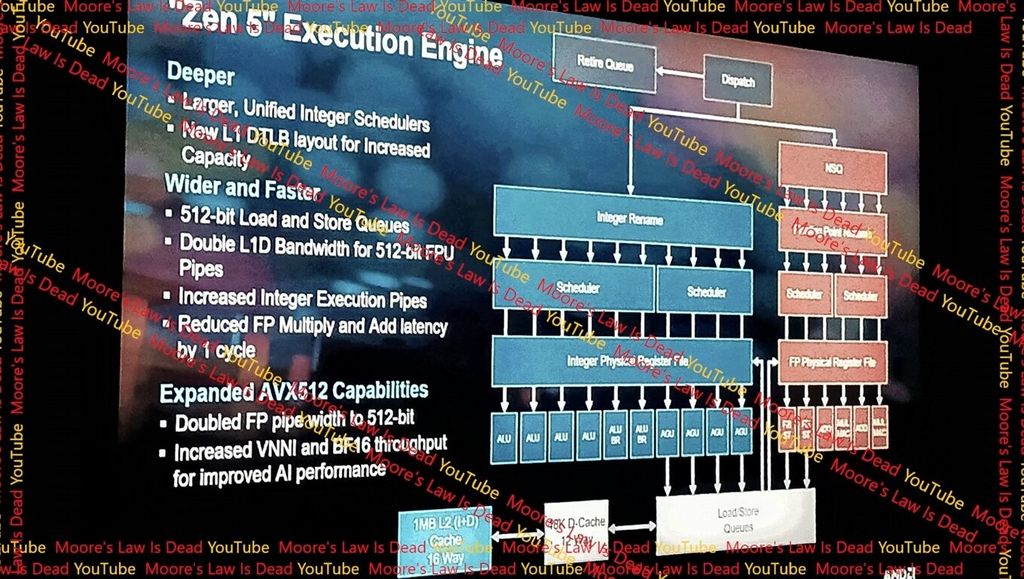

Neuigkeiten von dieser Website am 5. April. Im neuesten Video teilte die Quelle Moore's Law is Dead Informationen über die Ausführungs-Engine des AMD Zen 5-Prozessors (Execution Engine) mit und sagte, dass sie eine echte 512-Bit-Gleitkomma-Operationseinheit (FPU) verwenden wird ).

Den von der Quelle geteilten Folien zufolge wird die Ausführungs-Engine von Zen 5 detailliert beschrieben und verwendet eine echte 512-Bit-FPU.

Der AMD Zen 4-Prozessor verwendet eine zweikanalige 256-Bit-FPU bei der Ausführung der AVX-512-Anweisungsarbeitslast, während der Zen 5 eine echte 512-Bit-FPU zur Verarbeitung von 512-Bit-AVX- oder VNNI-Anweisungen verwendet. Es wird eine höhere Leistung erzielt.

Diese Seite erfuhr außerdem aus Berichten, dass AMD entsprechende Komponenten für die 512-Bit-FPU aktualisiert, die Kapazität von L1 DTLB erhöht, die Load-Store-Warteschlange erweitert, die Bandbreite des L1-Datencaches verdoppelt und die Größe um 50 erhöht hat %. Die Größe von L1D ist von 32 KB in „Zen 4“ auf nun 48 KB gestiegen.

FPU MADD-Latenz um 1 Zyklus reduziert. Zusätzlich zur FPU hat AMD die Anzahl der Integer-Ausführungspipes von 8 (Zen 4) auf 10 erhöht, wobei die exklusive L2-Cache-Größe weiterhin bei 1 MB pro Kern liegt.

Das obige ist der detaillierte Inhalt vonAMD Zen 5-Ausführungs-Engine enthüllt: Verwendung echter 512-Bit-FPU. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Einführung in die JavaScript-Modulspezifikationen CommonJS, AMD und CMD

- Der Testbericht zum Intel Raptor Lake i9-13900 der 13. Generation deutet darauf hin, dass AMD Ryzen 7000 der König sein könnte

- AMD plant, im Jahr 2024 die neuen Prozessoren der Ryzen 8000-Serie auf den Markt zu bringen, ein riesiges Upgrade, angeführt von der Zen5-Architektur

- Was ist amd240

- AMD Zen 5-Prozessoren haben damit begonnen, vorläufige Einreichungen für Linux 6.6 zu unterstützen