Heim >Technologie-Peripheriegeräte >IT Industrie >Intel plant, seine 3D-Foveros-Verpackungskapazität bis 2025 zu vervierfachen

Intel plant, seine 3D-Foveros-Verpackungskapazität bis 2025 zu vervierfachen

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBnach vorne

- 2023-08-23 23:53:021601Durchsuche

Laut Nachrichten dieser Website vom 22. August investiert Intel aktiv in die Forschung und Entwicklung fortschrittlicher Prozesse und stärkt gleichzeitig sein fortschrittliches Verpackungsgeschäft. Derzeit baut das Unternehmen die neueste Verpackungsfabrik in Penang, Malaysia, und stärkt sein 2.5D-Geschäft /3D-Verpackungslayout.

Das Unternehmen plant, seine Produktionskapazität für 3D-Foveros-Verpackungen bis 2025 zu vervierfachen. Intel-Vizepräsident Robin Martin gab heute in einem Interview in Penang bekannt, dass die neue Fabrik in Penang in Zukunft die größte 3D-Advanced-Packaging-Basis des Unternehmens sein wird.

Im Jahr 2021 kündigte Intel an, 7,1 Milliarden US-Dollar (Anmerkung auf dieser Website: derzeit etwa 51,759 Milliarden Yuan) in den Bau einer neuen führenden Halbleiterverpackungsfabrik von Intel in Bayan Lepas, Penang, zu investieren.

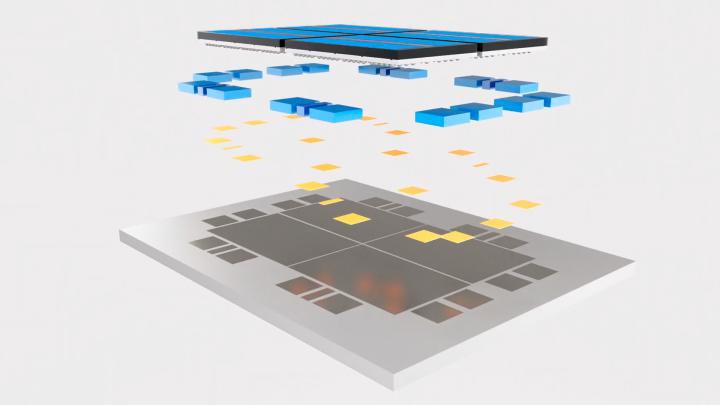

Laut Intel dient die Verpackung des Chips als physische Schnittstelle zwischen dem Prozessor und dem Motherboard und spielt eine entscheidende Rolle für die Leistung auf Produktebene. Fortschrittliche Verpackungstechnologie kann die Integration von Multiprozesstechnologie durch verschiedene Computer-Engines erleichtern und dabei helfen, neue Methoden in der Systemarchitektur einzuführen. Berichten zufolge nutzt die Foveros-Verpackungstechnologie von Intel 3D-Stacking, um eine Logik-zu-Logik-Integration zu erreichen Flexibilität, Technologie-IP-Blöcke mit verschiedenen Speicher- und Eingabe-/Ausgabeelementen in neuen Geräteformfaktoren zu kombinieren. Produkte können in kleinere Chiplets oder Kacheln unterteilt werden, wobei I/O-, SRAM- und Stromversorgungsschaltkreise im Basischip hergestellt werden und Hochleistungs-Logik-Chiplets oder -Kacheln darauf gestapelt werden. Darüber hinaus werden Intels neue Verpackungsmöglichkeiten erschlossen neue Designs durch die Kombination von EMIB- und Foveros-Technologien, die die Verbindung verschiedener Chiplets und Blöcke mit einer Leistung ermöglichen, die im Wesentlichen der eines einzelnen Chips entspricht. Laut Intel können Designer mit Foveros Omni eine größere Kommunikationsflexibilität erreichen, indem sie kleine Chips oder Blöcke innerhalb eines Gehäuses nutzen.

Das obige ist der detaillierte Inhalt vonIntel plant, seine 3D-Foveros-Verpackungskapazität bis 2025 zu vervierfachen. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!

In Verbindung stehende Artikel

Mehr sehen- Das Intel-Bedienfeld fehlt

- Intel veröffentlicht eine Softwareplattform für Quantencomputing-Entwickler, die bei der Entwicklung von Quantenalgorithmen helfen soll

- Der Mac Mini und der Mac Pro sind die letzten beiden Intel-Macs, die nach der Einführung von Mac Studio durch Apple übrig geblieben sind

- AMD demonstriert in Taipeh die Ryzen XDNA AI-Technologie, um mit Intel bei den KI-Fähigkeiten zu konkurrieren

- Intel veröffentlicht den neuesten 4644-Grafikkartentreiber, der starke Unterstützung für „Madden NFL 24' und „Pathfinder' bietet.