Heim >häufiges Problem >Was ist FPGA?

Was ist FPGA?

- 青灯夜游Original

- 2023-01-29 15:59:4354872Durchsuche

FPGA ist ein integrierter Chip, der auf digitalen Schaltkreisen basiert und eine Art programmierbares Logikgerät (PLD) ist. FPGA erscheint als halbkundenspezifischer Schaltkreis im Bereich der anwendungsspezifischen integrierten Schaltkreise (ASIC) und behebt nicht nur die Mängel von kundenspezifischen Schaltkreisen, überwindet aber auch die Mängel der begrenzten Anzahl von Gate-Schaltkreisen der ursprünglichen programmierbaren Geräte.

Die Betriebsumgebung dieses Tutorials: Windows 7-System, Dell G3-Computer.

Was ist FPGA?

FPGA (Field Programmable Gate Array) ist ein Produkt, das auf der Basis programmierbarer Geräte wie PAL (Programmable Array Logic) und GAL (General Array Logic) weiterentwickelt wird. Es handelt sich um eine semi-kundenspezifische Schaltung im Bereich der anwendungsspezifischen integrierten Schaltkreise (ASIC), die nicht nur die Mängel kundenspezifischer Schaltungen behebt, sondern auch die Mängel der begrenzten Anzahl von Gattern in den ursprünglichen programmierbaren Geräten überwindet.

FPGA ist im Wesentlichen ein Chip, ein integrierter Chip, der hauptsächlich aus digitalen Schaltkreisen besteht.

FPGA wurde 1985 von Ross Freeman, einem der Gründer von Xilinx, erfunden. Es handelt sich um eine Art programmierbares Logikgerät (PLD). Dieses Mal liegt die Entstehung des berühmten Mooreschen Gesetzes etwa 20 Jahre zurück, doch nach der Erfindung des FPGA überstieg die anschließende Entwicklungsgeschwindigkeit die Vorstellungskraft der meisten Menschen.

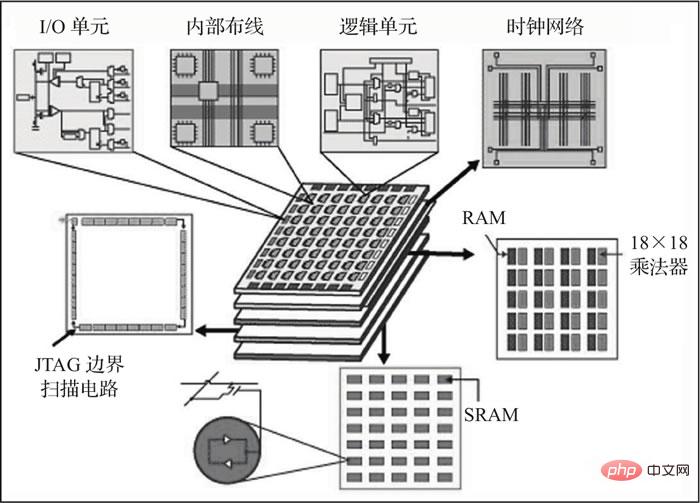

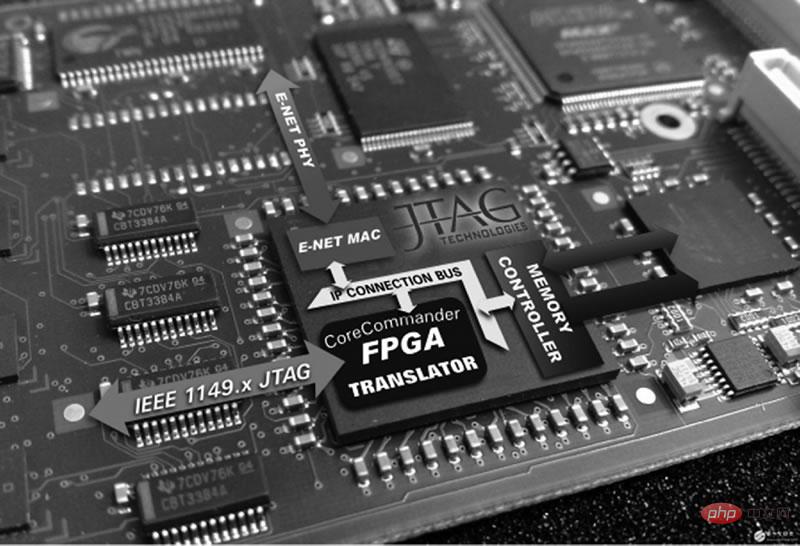

Abbildung 1 zeigt das physische Bild des FPGA-Chips:

Abbildung 1 Das physische Bild des FPGA-Chips

FPGA-Entwicklungsgeschichte

Vor der Erfindung von PLD verwendeten Ingenieure diskrete Logikchips mit mehreren Logikgattern Beim Aufbau eines Schaltungssystems ist es schwierig, komplexe Logikfunktionen zu implementieren.

Um dieses Problem zu lösen, wurde in den 1970er Jahren das Programmable Logic Array (PLA) herausgebracht, das eine feste Anzahl von UND-Gattern und NICHT-Gattern enthält, die die „UND-Ebene“ bzw. „ODER-Ebene“ bilden ", also "AND-Verbindungsmatrix" und "OR-Verbindungsmatrix", sowie die Verbindungsmatrix, die nur einmal programmiert werden kann (da die Programmierung hier auf dem Fuse-Prozess basiert), also einige relativ komplexe UND oder mehrere Ausdrücke können realisiert werden. Die interne Struktur von PLA ist in Abbildung 2 dargestellt:

Abbildung 2 Interne Struktur von PLA

Gleichzeitig mit PLA kam der Programmable Read-Only Memory (PROM) und seine interne Struktur heraus Wie in Abbildung 3 dargestellt. Wie PLA enthält PROM intern eine „AND-Verbindungsmatrix“ und eine „OR-Verbindungsmatrix“, aber die Verbindungsmatrix des UND-Gatters ist in der Hardware festgelegt und nur die Verbindungsmatrix des ODER-Gatters ist programmierbar.

Abbildung 3 PROM-interne Struktur

Wenn nur die Verbindungsmatrix des UND-Gatters programmierbar ist und die Verbindungsmatrix des ODER-Gatters durch Hardware festgelegt ist, wird diese Art von Chip als Programmable Array Logic (PAL) bezeichnet. ) kann PAL entsprechend den unterschiedlichen Arbeitsmodi der Ausgangsschaltung in Dreizustandsausgabe, Registerausgabe und Komplementärausgabe unterteilt werden, PAL verwendet jedoch immer noch Sicherungstechnologie und kann nur einmal programmiert werden. Das Strukturdiagramm von PAL ist in Abbildung 4 dargestellt.

Abbildung 4 PAL-Strukturdiagramm

Auf der Basis von PAL wurde ein allgemeines Array-Logikgerät (Generic Array Logic, GAL) entwickelt. Im Vergleich zu PAL weist GAL zwei Verbesserungen auf:

- Übernimmt die elektrisch löschbare Der CMOS-Prozess kann mehrfach kompiliert werden, was die Rekonfigurierbarkeit und Flexibilität des Geräts verbessert.

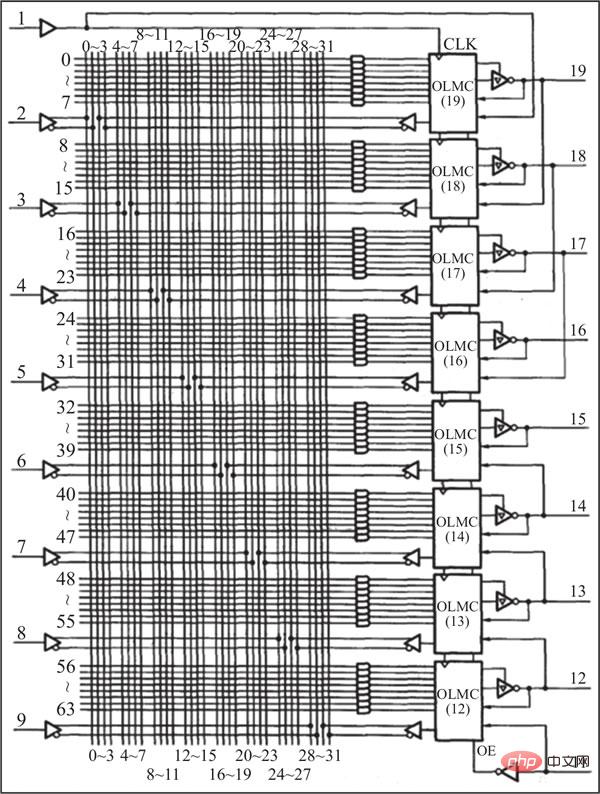

- Übernimmt eine programmierbare Ausgangslogik-Makrozelle (Output Logic Macro Cell, OLMC), die durch Programmieren von OLMC programmiert werden kann Nur ein GAL-Modell kann die Arbeitsmodi aller PAL-Geräte-Ausgangsschaltungen realisieren, was die Vielseitigkeit des Geräts erhöht. Das Strukturdiagramm von

GAL ist in Abbildung 5 dargestellt:

Abbildung 5 GAL-Strukturdiagramm

Frühes PLD bestand hauptsächlich aus den oben genannten vier Arten von Chips, nämlich PROM, PLA, PAL und GAL. Ihr gemeinsames Merkmal besteht darin, dass sie Logikfunktionen mit guten Geschwindigkeitseigenschaften implementieren können, aufgrund ihrer zu einfachen Strukturen jedoch nur kleinere digitale Schaltungen implementieren können.

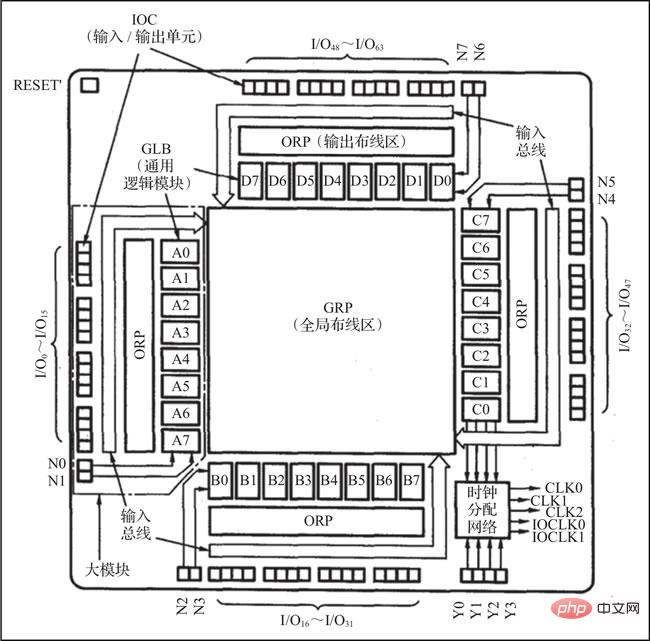

Mit der Entwicklung von Wissenschaft und Technologie und dem Fortschritt der Gesellschaft stellen die Menschen immer höhere Anforderungen an die Integration von Chips. Frühe PLD-Produkte konnten die Bedürfnisse der Menschen nicht erfüllen und so wurde das Complex Programmable Logic Device (CPLD) geboren. CPLD kann als Fortsetzung der PLA-Gerätestruktur betrachtet werden, und ein CPLD-Gerät kann auch als eine Sammlung mehrerer PLAs und einer programmierbaren Verbindungsmatrix betrachtet werden. Das interne Strukturdiagramm von CPLD ist in Abbildung 6 dargestellt.

Abbildung 6 CPLD-Strukturdiagramm

FPGA kam einige Jahre früher als CPLD auf den Markt und wird zusammen mit CPLD als programmierbares Logikgerät mit hoher Dichte bezeichnet, unterscheidet sich jedoch grundlegend. Die interne Architektur des FPGA-Chips folgt keiner ähnlichen Struktur wie PLA, sondern übernimmt das Konzept des Logic Cell Array (LCA), das die Idee der Verwendung einer großen Anzahl von UND-Gattern und NICHT-Gattern ändert Früher wurden PLD-Geräte verwendet, die hauptsächlich Nachschlagetabellen und Register verwenden.

Darüber hinaus weisen FPGA und CPLD auch Unterschiede in Bezug auf Ressourcentyp, Geschwindigkeit usw. auf, wie in der folgenden Tabelle dargestellt.

Das obige ist der detaillierte Inhalt vonWas ist FPGA?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!