Heim >Betrieb und Instandhaltung >Betrieb und Wartung von Linux >Machen Sie sich mit dem automatisierten Konstruktionstool Makefile make für Linux-Projekte vertraut

Machen Sie sich mit dem automatisierten Konstruktionstool Makefile make für Linux-Projekte vertraut

- WBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBOYWBnach vorne

- 2022-01-24 17:11:362032Durchsuche

Dieser Artikel stellt Ihnen das automatische Projektkonstruktionstool in Linux vor. Im wirklichen Leben können wir uns oft nicht nur auf den Code einer Datei verlassen, um eine bestimmte Funktion auszuführen. Zu diesem Zeitpunkt sind mehrere verschiedene Abschnitte erforderlich in ein Projekt eingebaut werden und alle Module gepackt und kombiniert werden, um die endgültige Funktion zu erreichen. Ich hoffe, es hilft allen.

Makefile

Makefile ist eine Textdatei, die den Build-Regelprozess eines Projekts aufzeichnet. Ob Sie bei der Arbeit Makefiles schreiben können, zeigt einerseits, ob eine Person in der Lage ist, umfangreiche Projekte abzuschließen. Gleichzeitig werden die Quelldateien in einem Projekt nicht gezählt. Sie werden je nach Typ in mehreren Verzeichnissen abgelegt , Funktion und Modul Es werden eine Reihe von Regeln definiert, um anzugeben, welche Dateien zuerst kompiliert werden müssen, welche Dateien später kompiliert werden müssen und noch komplexere Funktionsoperationen ausgeführt werden können Es bringt Folgendes mit sich: „Automatisierte Kompilierung“. Nach dem Schreiben ist nur ein Make-Befehl erforderlich, und das gesamte Projekt wird vollständig automatisch kompiliert und übersetzt, was die Effizienz der Softwareentwicklung erheblich verbessert.

Arbeitsprinzip

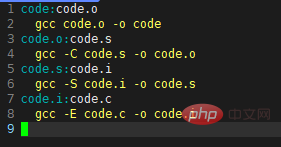

Im Makefile werden Abhängigkeiten zwischen verschiedenen Dateien gebildet. Beispielsweise wird eine code.exe über einen Link basierend auf code.o generiert, und code.o wird basierend auf code.s generiert Code.s wird durch Kompilierung basierend auf Code.i generiert, Code.i wird nach Abschluss der Vorverarbeitung basierend auf Code.c generiert und die Quelle wird Schicht für Schicht gefunden. Seine Regeln verwenden eine Flashback-Methode, bei der die erste Datei als letzte abgeschlossene Datei behandelt wird. Wenn die aktuelle Datei nicht generiert wird, wird sie durch Abhängigkeiten und gegenseitige Generierungsmethoden Schicht für Schicht weiterentwickelt und schließlich die Bildung aller Dateien abgeschlossen.

AbhängigkeitenA:B A ist abhängig von B

Abhängigkeitsmethodegcc-Option + B -o +A A ist die von B nach der Verarbeitung generierte Datei

Projekt. Bereinigung Projekte müssen bereinigt werden. Wenn sie nicht direkt oder indirekt mit der ersten Zieldatei verknüpft sind, werden die danach definierten Befehle nicht automatisch ausgeführt. Wir können jedoch zeigen, dass make ausgeführt wird. Das heißt, der Befehl „make clean“ wird verwendet, um alle Zieldateien für die Neukompilierung zu löschen. Aber im Allgemeinen legen wir unsere sauberen Zieldateien als Pseudoziel fest und ändern es mit .PHONY. Das Merkmal des Pseudoziels ist, dass es immer von

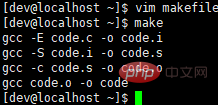

ausgeführt wird.Prinzipmake sucht im aktuellen Verzeichnis nach einer Datei mit dem Namen „Makefile“ oder „makefile“.

Wenn es gefunden wird, wird die erste Datei im Inhalt der Datei gefunden und diese Datei als endgültige Zieldatei verwendet.

Wenn die Datei derzeit nicht existiert oder die Änderungszeit der abhängigen Dateien der Datei neuer ist als die der aktuellen Datei, wird der später definierte Befehl ausgeführt, um die aktuelle Datei zu generieren.

Wenn die abhängige Datei der Datei nicht existiert, fahren Sie mit den Schritten 2 und 3 für diese abhängige Datei fort, bis die endgültige Quelldatei gefunden wird.

Natürlich sind Ihre C-Datei und Ihre H-Datei vorhanden. Make generiert also die . o-Datei und verwenden Sie dann die .o-Datei, um die ultimative Aufgabe von make zu deklarieren, nämlich die Ausführung der Datei.

Dies ist die Abhängigkeit des gesamten Make. Make sucht Schicht für Schicht nach Dateiabhängigkeiten, bis die erste Zieldatei schließlich kompiliert ist.

Wenn während des Suchvorgangs ein Fehler auftritt, beispielsweise wenn die letzte abhängige Datei nicht gefunden werden kann, wird make direkt beendet und meldet einen Fehler. Bei Fehlern in den definierten Befehlen oder einer fehlgeschlagenen Kompilierung gibt make jedoch keinen Grund aus.

make kümmert sich nur um Dateiabhängigkeiten. Das heißt, wenn die Datei nach dem Doppelpunkt immer noch nicht vorhanden ist, nachdem ich die Abhängigkeiten gefunden habe, tut es mir leid, ich werde nicht arbeiten.

make findet jedes Mal nur das erste Zielobjekt im Makefile zur Generierung und wird nach der Generierung beendet (das zweite Objekt wird nicht generiert)

.PHONY: clean

clear:

rm -rf $( obj)

【Ergänzung】

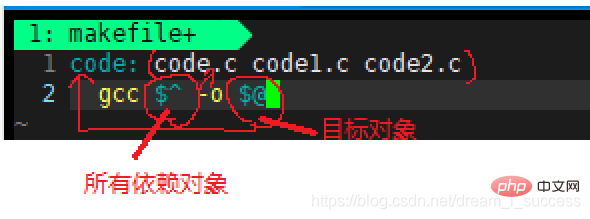

1. Die Verwendung vordefinierter Variablen: [$@], [ $^], [ $

$@ : bedeutet Zielobjekt

$^: Repräsentiert alle abhängigen Objekte

&<: repr das erste>

2. $ (Platzhalter ./.c) Ruft die Dateinamen aller Dateien ab, die mit .c im aktuellen Verzeichnis enden [Beispiel] src=$(wildcard ./.c) Code: $ (str)

3. $ (patsubst %.c, %.o,$(str)) bedeutet, dass die .c-Datei in der str-Variablen durch .o ersetzt wird, und dann in der obj-Variablen gespeichert.

4. Pseudoobjekt: Die Erklärung, dass ein Zielobjekt nichts mit externen Dateien zu tun hat, bedeutet, dass das Objekt jedes Mal neu generiert werden muss, unabhängig davon, ob es aktuell ist oder nicht, und unabhängig davon, ob die Anweisung von außen existieren kann jedes Mal ausgeführt [.PHONY: ]

5. Der Kompilierungsprozess des Programms: umfasst im Allgemeinen Vorverarbeitung, Kompilierung, Assemblierung und Verknüpfung, ist jedoch bei der eigentlichen Projektkonstruktion in zwei Schritte unterteilt, nämlich Kompilierung und Verknüpfung. Dies hat den Vorteil, dass Sie, wenn Sie nur eine .c-Datei ändern, im Vergleich zum vorherigen Prozess, bei dem alle .c-Dateien direkt kompiliert werden, um ausführbare Programme zu generieren, alle .c-Dateien neu kompilieren müssen, um ausführbare Programme zu generieren, was sehr ineffizient ist. Daher ist der Vorgang in zwei Schritte unterteilt: Zuerst generiert jede .o-Datei ihre eigene .o-Datei und verknüpft dann alle .o-Dateien miteinander. Sobald sich eine .c-Datei ändert, muss nur noch diese .c-Datei generiert werden angegebenen Modul im Programm.

Beispiel 1. Erstellen Sie ein allgemeines Makefile

Beispiel 2. Verwenden Sie ein vordefiniertes Makefile

Verwandte Empfehlungen: „Linux-Video-Tutorial“

Das obige ist der detaillierte Inhalt vonMachen Sie sich mit dem automatisierten Konstruktionstool Makefile make für Linux-Projekte vertraut. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!