Heim >häufiges Problem >Was kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?

Was kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?

- 王林Original

- 2020-12-11 15:23:4313738Durchsuche

Um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen, kann Cache-Speicher verwendet werden. Cache-Speicher ist ein kleiner, aber schneller Speicher, der sich zwischen der CPU und dem Hauptspeicher DRAM befindet. Er besteht normalerweise aus statischem Speicher. Statischer Speicher ist ein Speicher mit geringer Kapazität, aber hoher Geschwindigkeit, der zwischen der CPU und dem Speicher liegt.

Die Betriebsumgebung dieses Tutorials: Windows 7-System, Dell G3-Computer.

Um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen, kann die Implementierung den Cache zwischen CPU und Hauptspeicher verwenden.

Was ist Cache?

Cache-Speicher, ein Cache-Speicher in einem Computer, ist ein kleiner, aber schneller Speicher, der normalerweise zwischen der CPU und dem Hauptspeicher DRAM (Dynamic Random Access Memory) liegt von SRAM (Static Random Access Memory). Es handelt sich um einen Speicher mit geringer Kapazität, aber hoher Geschwindigkeit, der zwischen der CPU und dem Speicher liegt.

Die Geschwindigkeit der CPU ist viel höher als die des Speichers. Wenn die CPU direkt auf Daten aus dem Speicher zugreift, muss sie eine gewisse Zeit warten, während der Cache einen Teil der von der CPU gespeicherten Daten speichern kann gerade verwendet oder recycelt, wenn die CPU diesen Teil der Daten erneut verwenden muss. Er kann direkt aus dem Cache aufgerufen werden, wodurch wiederholter Zugriff auf Daten vermieden, die Wartezeit der CPU verkürzt und somit die Effizienz des Systems verbessert wird .

Funktion des Cache

Die Funktion des Cache besteht darin, die Rate der CPU-Dateneingabe und -ausgabe zu erhöhen. Die Cache-Kapazität ist klein, aber schnell, die Speichergeschwindigkeit ist niedrig, aber die Kapazität ist groß. Durch die Optimierung des Planungsalgorithmus wird die Leistung des Systems erheblich verbessert, als ob die Speichersystemkapazität dem Speicher entspricht und die Zugriffsgeschwindigkeit ähnlich ist der Cache.

Die Geschwindigkeit der CPU ist viel höher als die des Speichers. Wenn die CPU direkt auf Daten aus dem Speicher zugreift, muss sie eine gewisse Zeit warten, während der Cache einen Teil der von der CPU gespeicherten Daten speichern kann gerade verwendet oder recycelt, wenn die CPU diesen Teil der Daten erneut verwenden muss. Er kann direkt aus dem Cache aufgerufen werden, wodurch wiederholter Zugriff auf Daten vermieden, die Wartezeit der CPU verkürzt und somit die Effizienz des Systems verbessert wird . Der Cache ist in L1Cache (Level-1-Cache) und L2Cache (Level-2-Cache) unterteilt, der hauptsächlich in die CPU integriert ist, während L2Cache auf dem Motherboard oder der CPU integriert ist.

Grundprinzipien des Caches

Zusätzlich zum SRAM verfügt der Cache auch über eine Steuerlogik. Befindet sich der Cache außerhalb des CPU-Chips, wird seine Steuerlogik im Allgemeinen mit der Hauptspeicher-Steuerlogik kombiniert, die als Hauptspeicher-/Cache-Controller bezeichnet wird. Wenn sich der Cache innerhalb der CPU befindet, stellt die CPU ihre Steuerlogik bereit. C Der Datenaustausch zwischen CPU und Cache basiert auf Worten, während der Datenaustausch zwischen Cache und Hauptspeicher auf Blöcken basiert. Ein Block besteht aus mehreren Wörtern und hat eine feste Länge. Wenn die CPU ein Wort im Speicher liest, sendet sie die Speicheradresse des Worts an den Cache und den Hauptspeicher. Zu diesem Zeitpunkt bestimmt die Cache-Steuerlogik anhand der Adresse, ob sich das Wort derzeit im Cache befindet: Wenn dies der Fall ist, trifft der Cache zu und das Wort wird sofort an die CPU übertragen. Wenn nicht, fehlt der Cache Der Hauptspeicher-Lesezyklus wird verwendet, um das Wort aus dem Hauptspeicher zu lesen. Der Lesevorgang wird an die CPU gesendet. Gleichzeitig wird der gesamte Datenblock, der dieses Wort enthält, aus dem Hauptspeicher gelesen und an den Cache gesendet.

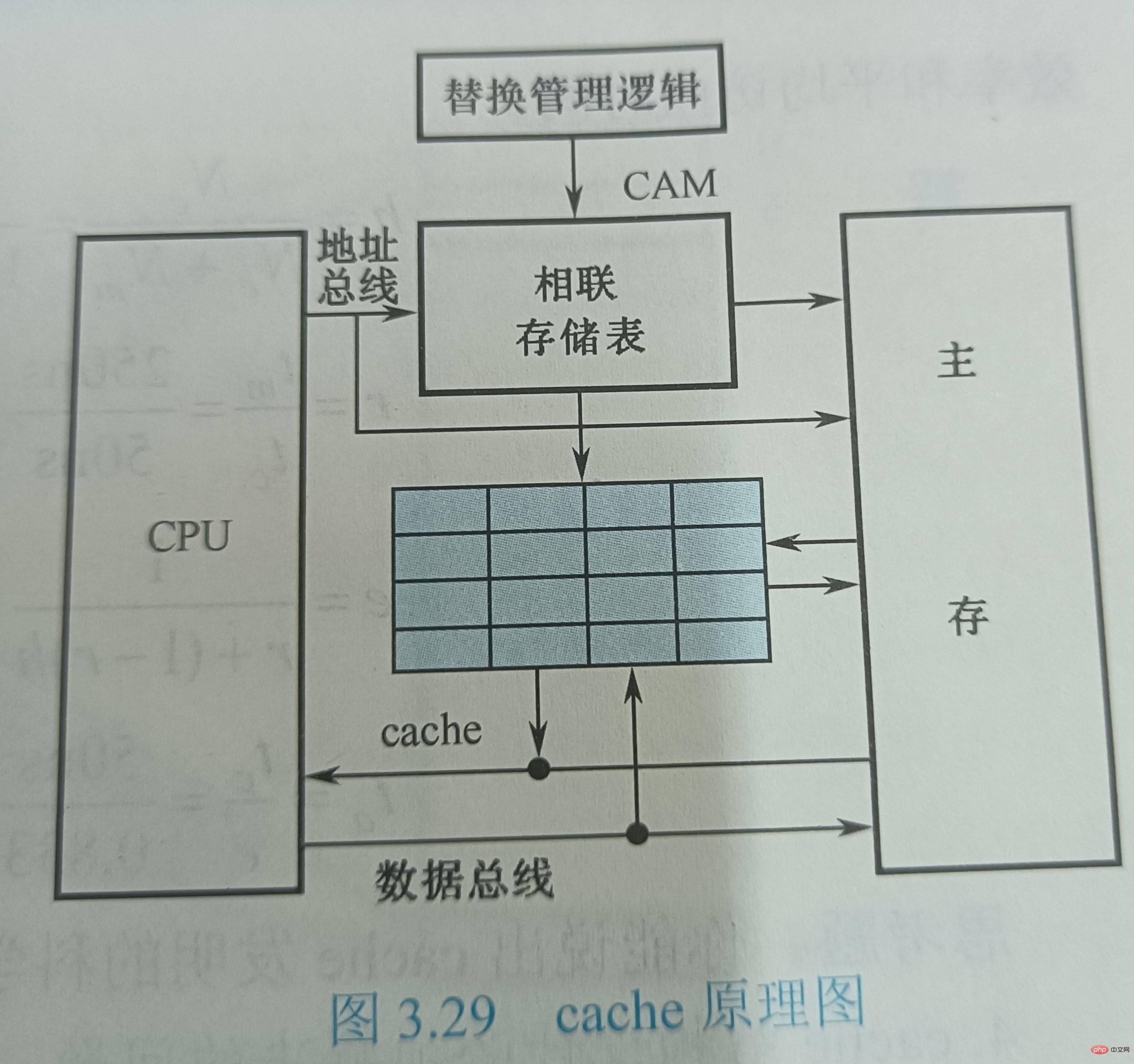

Abbildung 3.29 zeigt das schematische Diagramm des Caches. Nehmen Sie an, dass die Cache-Lesezeit 50 ns und die Hauptspeicher-Lesezeit 250 ns beträgt. Das Speichersystem ist modular aufgebaut und jedem 8K-Modul im Hauptspeicher ist ein Cache mit einer Kapazität von 16 Wörtern zugeordnet. Der Cache ist in 4 Zeilen unterteilt, jede Zeile enthält 4 Wörter (W). Die dem Cache zugewiesene Adresse wird in einem assoziativen Speicher CAM gespeichert, bei dem es sich um einen inhaltsadressierbaren Speicher handelt. Wenn die CPU einen Speicherzugriffsbefehl ausführt, sendet sie die Adresse des Wortes, auf das zugegriffen werden soll, an das CAM; wenn W nicht im Cache ist, wird W vom Hauptspeicher an die CPU übertragen. Gleichzeitig wird eine Datenzeile, die aus vier aufeinanderfolgenden Wörtern mit W besteht, an den Cache gesendet und ersetzt die ursprüngliche Datenzeile im Cache. Hier wird der Ersetzungsalgorithmus durch Hardware-Logikschaltungen implementiert, die stets die Cache-Nutzung verwalten.

Abbildung 3.29 zeigt das schematische Diagramm des Caches. Nehmen Sie an, dass die Cache-Lesezeit 50 ns und die Hauptspeicher-Lesezeit 250 ns beträgt. Das Speichersystem ist modular aufgebaut und jedem 8K-Modul im Hauptspeicher ist ein Cache mit einer Kapazität von 16 Wörtern zugeordnet. Der Cache ist in 4 Zeilen unterteilt, jede Zeile enthält 4 Wörter (W). Die dem Cache zugewiesene Adresse wird in einem assoziativen Speicher CAM gespeichert, bei dem es sich um einen inhaltsadressierbaren Speicher handelt. Wenn die CPU einen Speicherzugriffsbefehl ausführt, sendet sie die Adresse des Wortes, auf das zugegriffen werden soll, an das CAM; wenn W nicht im Cache ist, wird W vom Hauptspeicher an die CPU übertragen. Gleichzeitig wird eine Datenzeile, die aus vier aufeinanderfolgenden Wörtern mit W besteht, an den Cache gesendet und ersetzt die ursprüngliche Datenzeile im Cache. Hier wird der Ersetzungsalgorithmus durch Hardware-Logikschaltungen implementiert, die stets die Cache-Nutzung verwalten.

Probleme, die beim Design der Cache-Struktur gelöst werden müssenAus dem Grundprinzip des Caches geht hervor, dass das Cache-Design zwei Prinzipien folgen muss: Erstens hoffen wir, dass die Cache-Trefferquote so hoch ist wie möglich, was eigentlich nahe bei 1 liegen sollte; Die zweite besteht darin, zu hoffen, dass der Cache für die CPU transparent ist, dh unabhängig davon, ob ein Cache vorhanden ist oder nicht, greift die CPU auf die gleiche Weise auf den Speicher zu und die Software kann darauf zugreifen den Cache, ohne irgendwelche Anweisungen hinzuzufügen. Die Probleme mit der Trefferquote und der Transparenz sind gelöst. Aus Sicht des CPU-Zugriffs auf den Speicher wird der Speicher die Kapazität des Hauptspeichers und eine Geschwindigkeit haben, die nahe am Cache liegt. Zu diesem Zweck muss eine bestimmte Hardwareschaltung hinzugefügt werden, um die Steuerfunktion zu vervollständigen, nämlich den Cache-Controller.

Beim Entwerfen der Cache-Struktur müssen mehrere Probleme gelöst werden: ① Wie werden die Inhalte des Hauptspeichers gespeichert, wenn sie in den Cache übertragen werden? ② Wie werden die Informationen im Cache gefunden, wenn auf den Speicher zugegriffen wird? die vorhandenen Informationen im Cache, wenn der Cache-Speicherplatz nicht ausreicht. ④ Wie kann der Cache-Inhalt neu geschrieben werden, wenn ein Schreibvorgang erforderlich ist?

Unter diesen hängen die ersten beiden Fragen miteinander zusammen, nämlich wie man die Hauptspeicherinformationen im Cache findet und wie man die Hauptspeicheradresse in eine Cache-Adresse umwandelt. Im Vergleich zur Hauptspeicherkapazität ist die Cache-Kapazität sehr gering. Der gespeicherte Inhalt ist nur eine Teilmenge des Hauptspeicherinhalts, und der Datenaustausch zwischen Cache und Hauptspeicher erfolgt in Blockeinheiten. Um den Hauptspeicherblock in den Cache zu legen, muss eine Methode verwendet werden, um die Hauptspeicheradresse im Cache zu lokalisieren, was als Adresszuordnung bezeichnet wird. Die physikalische Bedeutung des Wortes „Mapping“ besteht darin, die entsprechende Beziehung zwischen Standorten zu ermitteln und diese mit Hardware umzusetzen. Auf diese Weise wird beim Zugriff der CPU auf den Speicher die Speicheradresse eines von ihr angegebenen Wortes automatisch in eine Cache-Adresse umgewandelt, dh eine Cache-Adresskonvertierung.

Das Cache-Ersetzungsproblem besteht hauptsächlich darin, den Ersetzungsalgorithmus auszuwählen und auszuführen, um den Inhalt im Cache zu ersetzen, wenn der Cache fehlt. Die letzte Frage betrifft die Schreiboperationsstrategie des Caches, die sich auf die Aufrechterhaltung der Konsistenz zwischen Hauptspeicher und Cache während Aktualisierungen konzentriert.

(Teilen von Lernvideos: Programmiervideo)

Das obige ist der detaillierte Inhalt vonWas kann getan werden, um das Problem der Geschwindigkeitsanpassung zwischen CPU und Hauptspeicher zu lösen?. Für weitere Informationen folgen Sie bitte anderen verwandten Artikeln auf der PHP chinesischen Website!